1、背景介绍

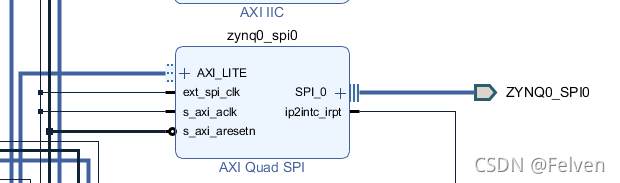

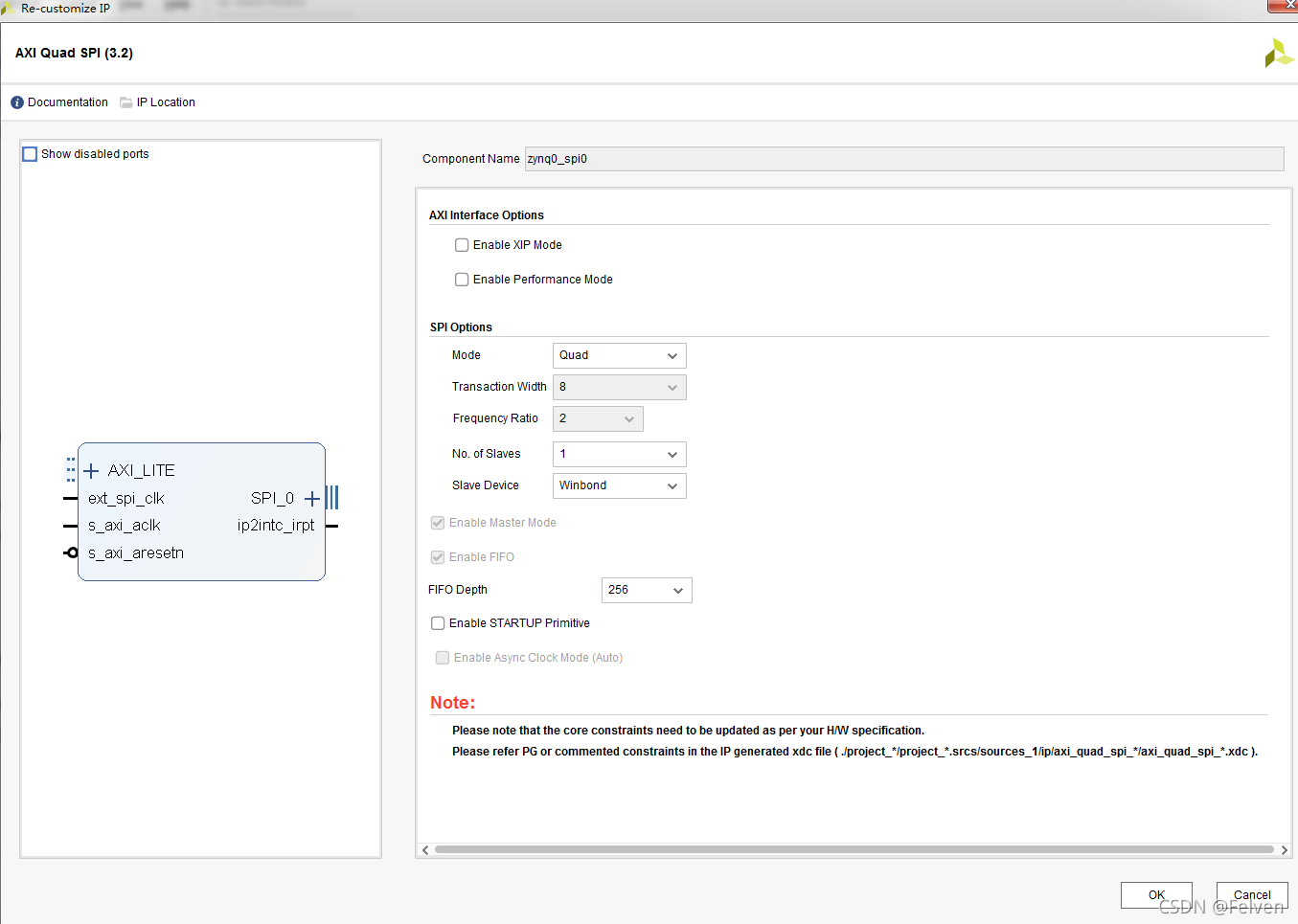

国产ZYNQ下通过PL部分IP核连接一片国产兆易创新GD25Q256E flash。FPGA中的IP核配置如下

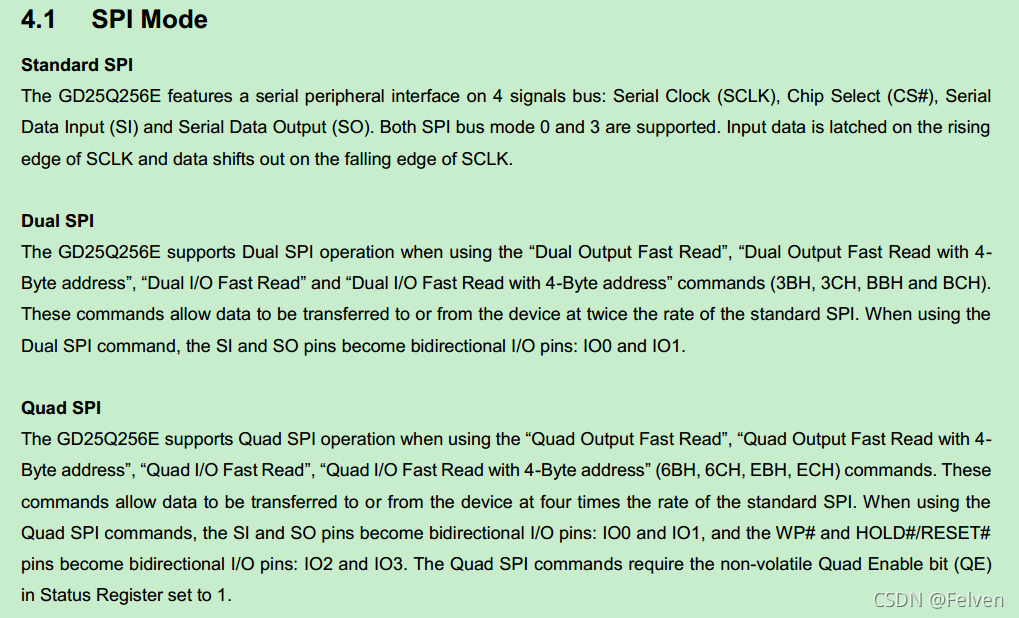

2、flash介绍

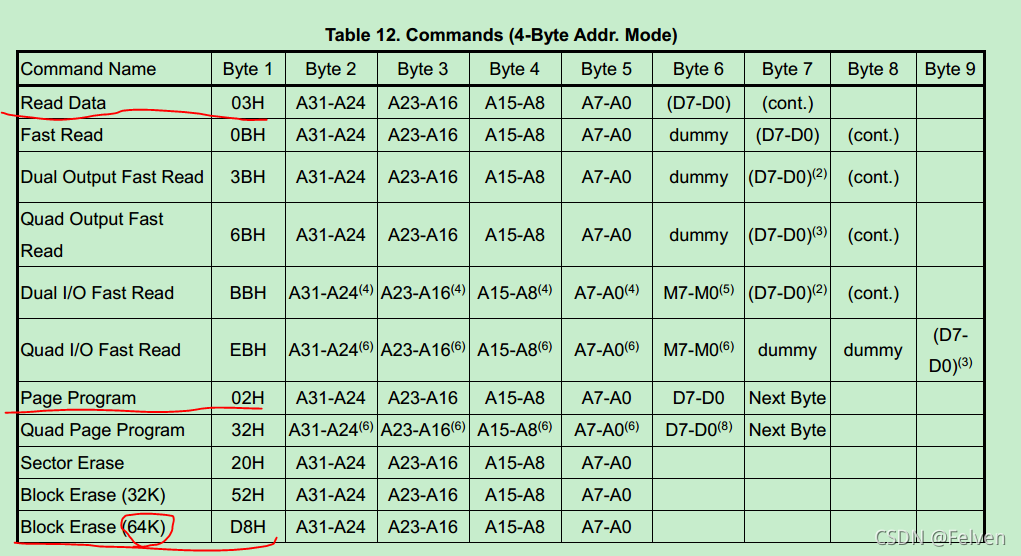

GD25Q256E支持下面几种方式

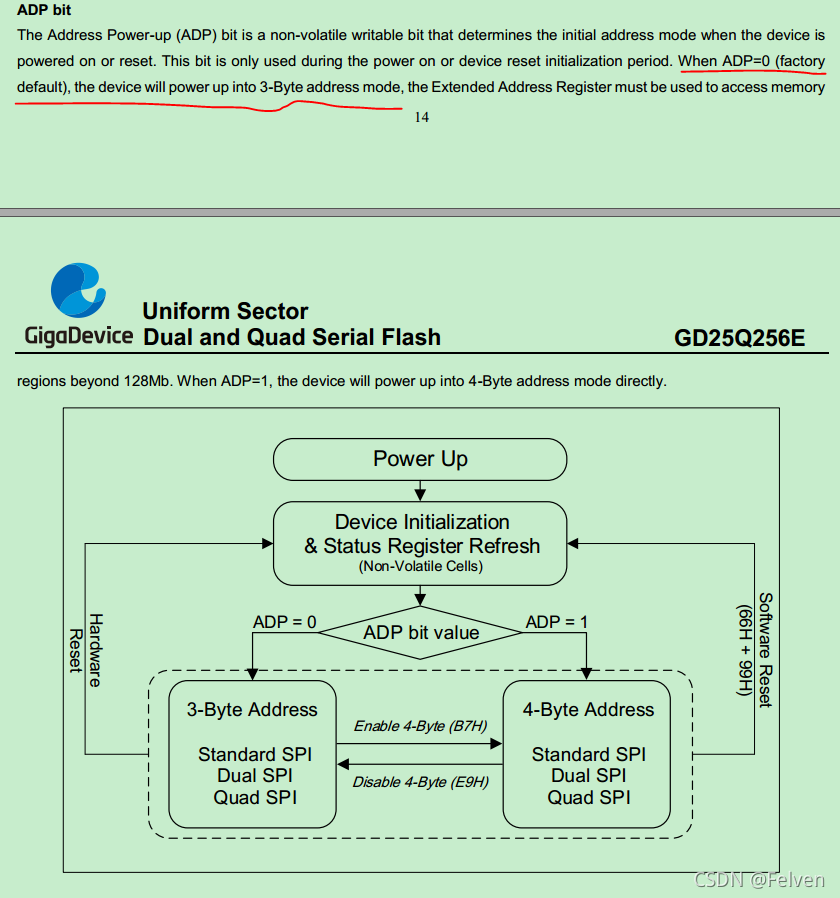

其中出厂默认方式为standard SPI模式,为了和PL部分的Quad SPI IP核配合使用,需要通过standalone方式配置flash寄存器,将其改为Quad SPI工作方式,同时也需要将3 byte address方式改为4 byte address

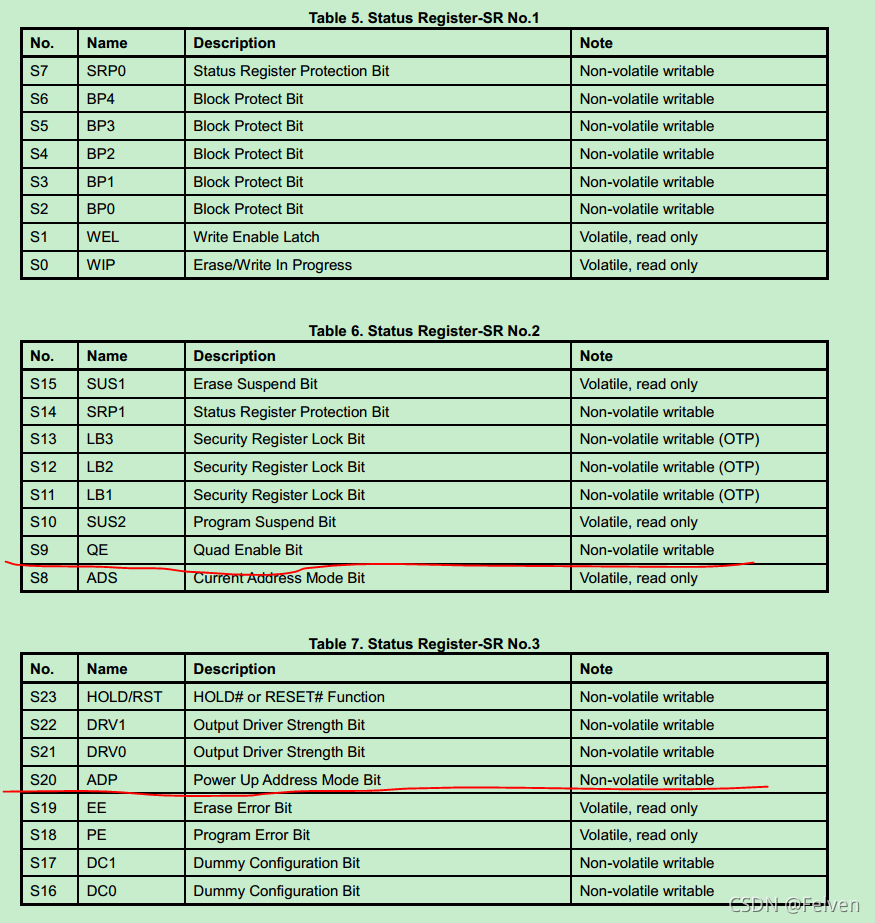

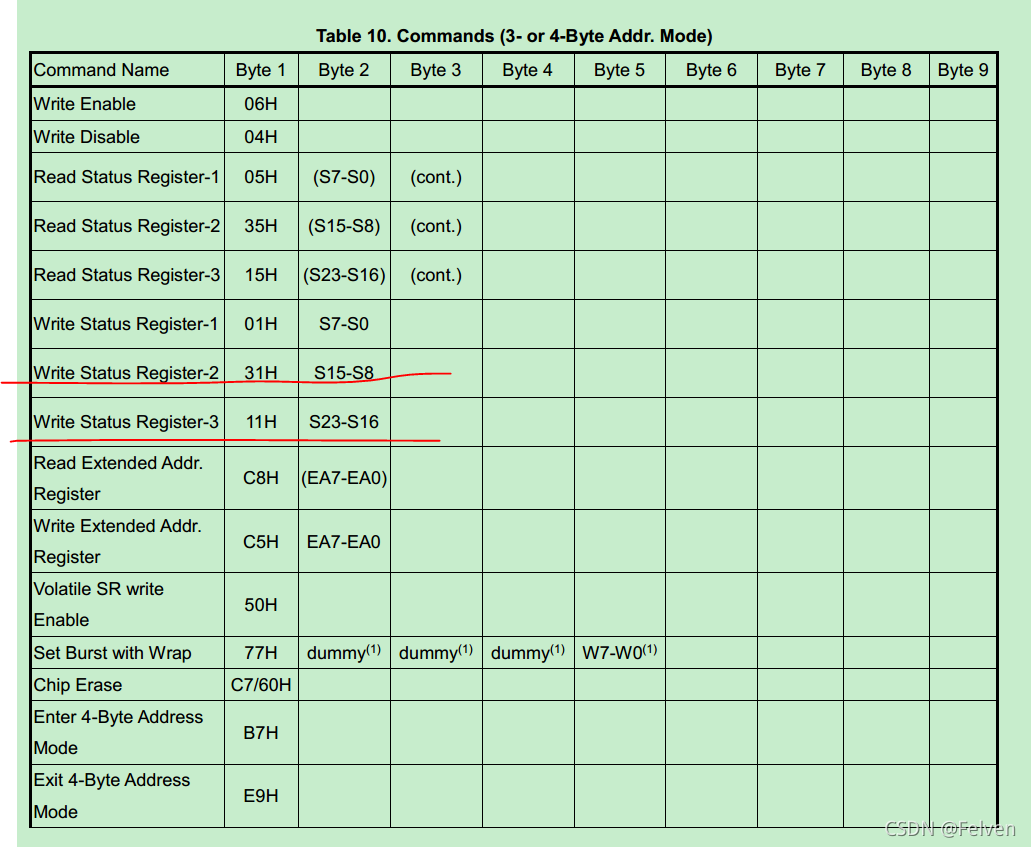

为此需要配置两个寄存器位置,将两个相应BIT位置1

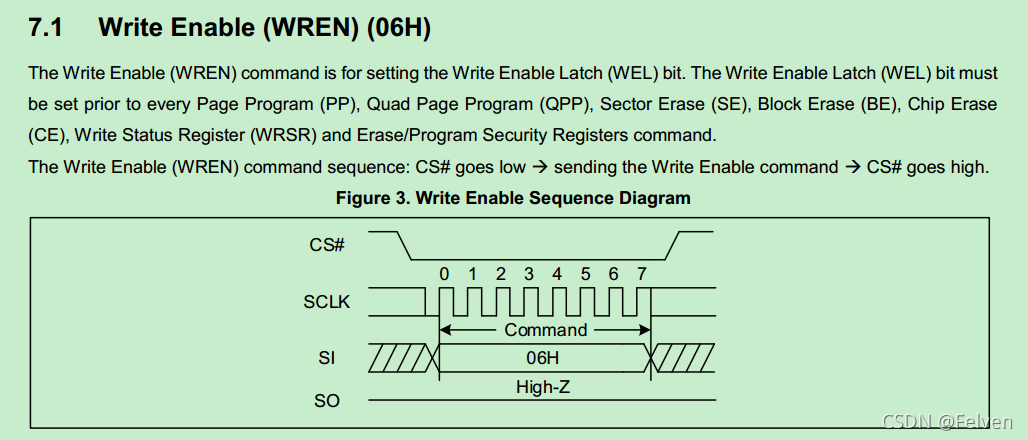

写寄存器时序在datasheet中也有说明,参考手册操作即可。

注意每次写之前要write enable

3、内核修改

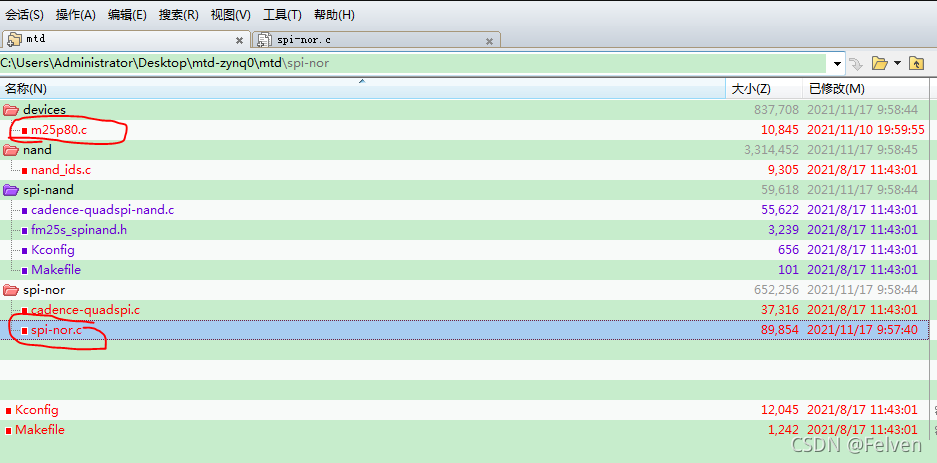

内核中需要修改/drivers/mtd下面的两个文件,如图

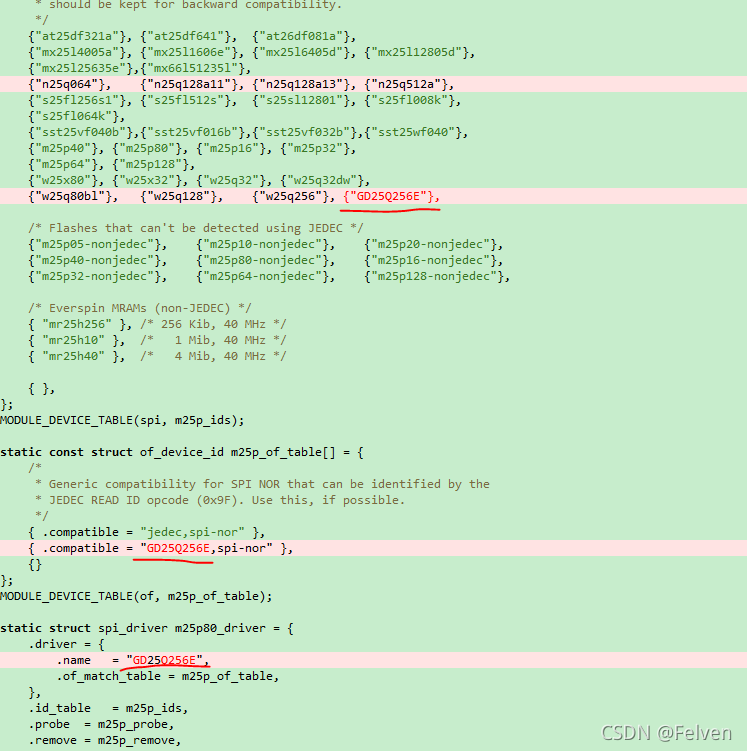

在m25p80.c中增加设备类型GD25Q256E

Spi-nor.c中修改如下

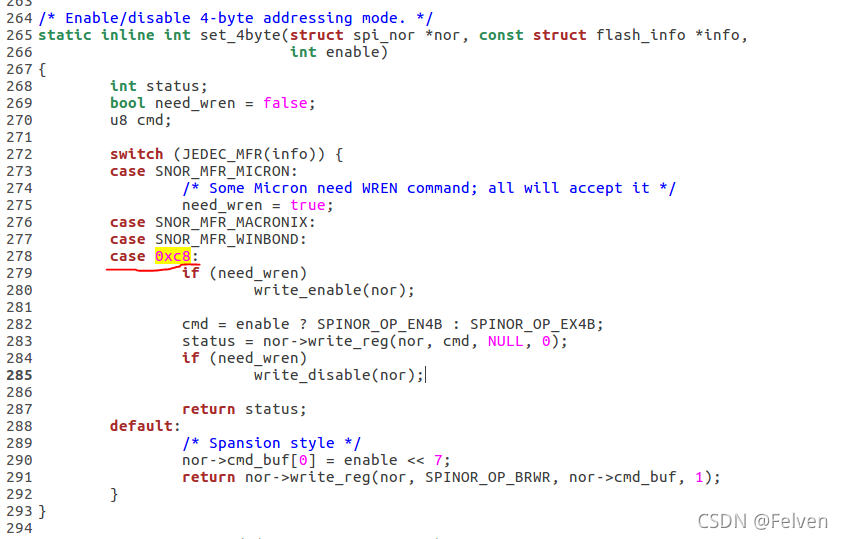

首先修改set_4byte,增加兆易创新ID 0xc8

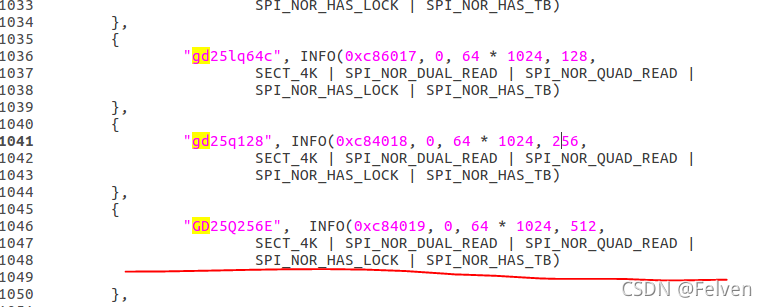

增加flash设备类型

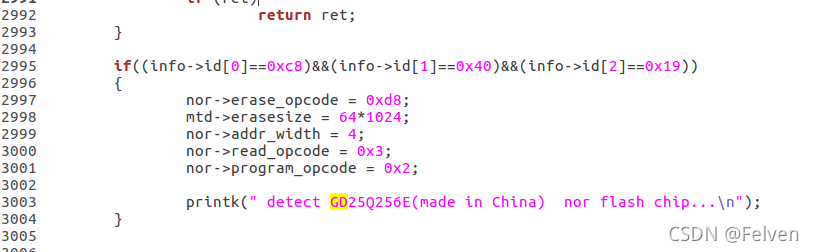

在spi_nor_scan函数中增加flash设备类型判断,当匹配到GD25Q256E时配置下面的操作命令,命令见datasheet,注意此时flash已经是4byte地址方式了

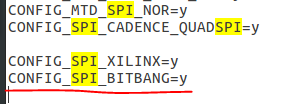

在defconfig中增加XILINX_SPI控制器配置

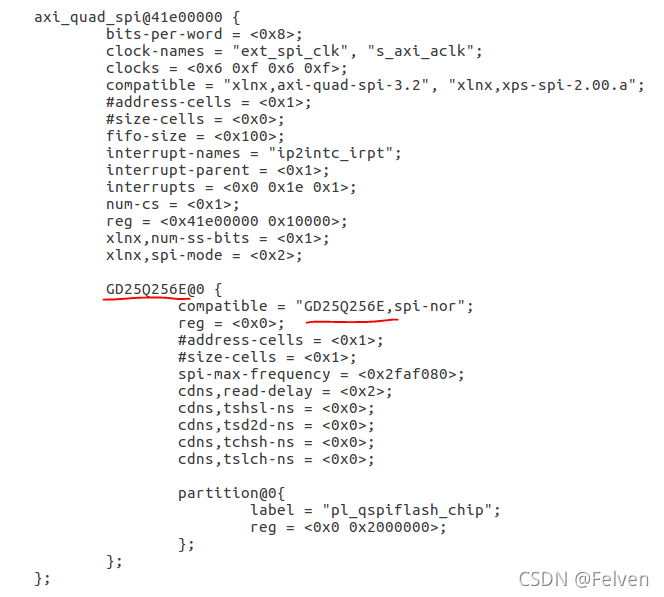

4、devicetree配置

这里对flash只分配一个分区,大小为32MB

5、验证

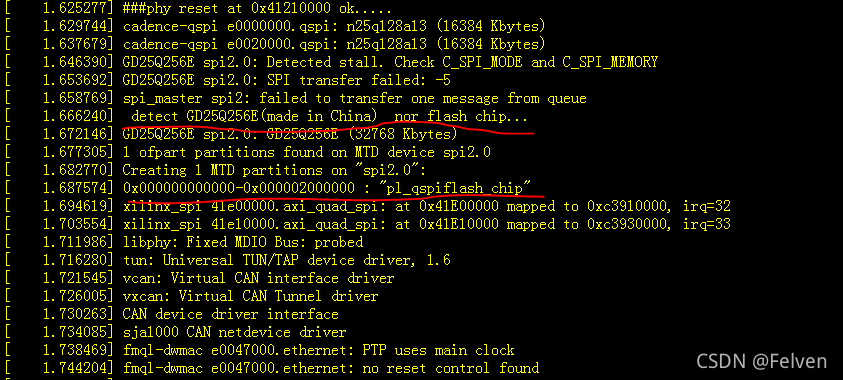

系统上电之后能看到打印信息,表明flash已经挂载成功,后续使用ubi文件系统来进行格式化即可。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?