前言

博主只是一个普通的大二本科生喵,所以可能这篇文章有很多不对或者不严谨的地方,如果有小伙伴发现错误的话希望可以告诉博主喵,谢谢喵。

在采集信号的时候,我们有时会遇到一些信号幅度不断变化的情况,我们该怎么使输出信号幅度保持恒定或仅在较小范围内变化呢?这时候就要用到AGC电路了喵。

一、AGC电路是什么呢?

AGC其实就是自动增益控制的缩写喵,所以AGC电路是一种可以自动控制增益大小的电路,也就是说,我们需要在输入信号变大的时候减小增益,在输入信号减小的时候增大增益,看到这里,学习过模电的小伙伴应该有种奇妙的既视感了对吧?没错,这不就是负反馈嘛,也就是说,AGC电路就是要搭建一个负反馈电路,进而来实现自动增益控制。(可能说负反馈不太严谨,但是类似这个意思)

二、VCA821和VCA810

VCA821可以在±3.5V到±6V的电压范围内工作,有着很高精度的增益控制范围,在20dB最大增益下,增益控制输入电压在+1V到+2V之间变化时,增益偏差不超过±0.3dB。而VCA810 使用 ±5 V 的电源工作,增益控制电压从 0 V 到 -2 V 变化时,增益从 -40 dB 线性变化到 +40 dB。它们的增益控制特性使其能够用于自动增益控制(AGC)应用,不过VCA821有着更高的带宽,而且支持差分输入,因此这里我选择VCA821喵~(在使用一个芯片之前一定要学会看数据手册喔,后续会单独出一篇怎么看数据手册的文章喵~可以关注喵个涛涛喵)

| 参数 | VCA821 | VCA810 |

|---|---|---|

| 带宽 | 小信号时为 710 MHz,大信号时为 320 MHz | 恒定带宽为 35 MHz |

那么有了VCA821,我们就可以来着手设计我们的AGC电路了,根据数据手册,VCA821的Vg端就是电压控制增益的引脚,也就是说我们要构建一个从输出端引回来的反馈电路来控制Vg端的电压的大小,那么我们应该从哪里下手呢?

三、电路的原理

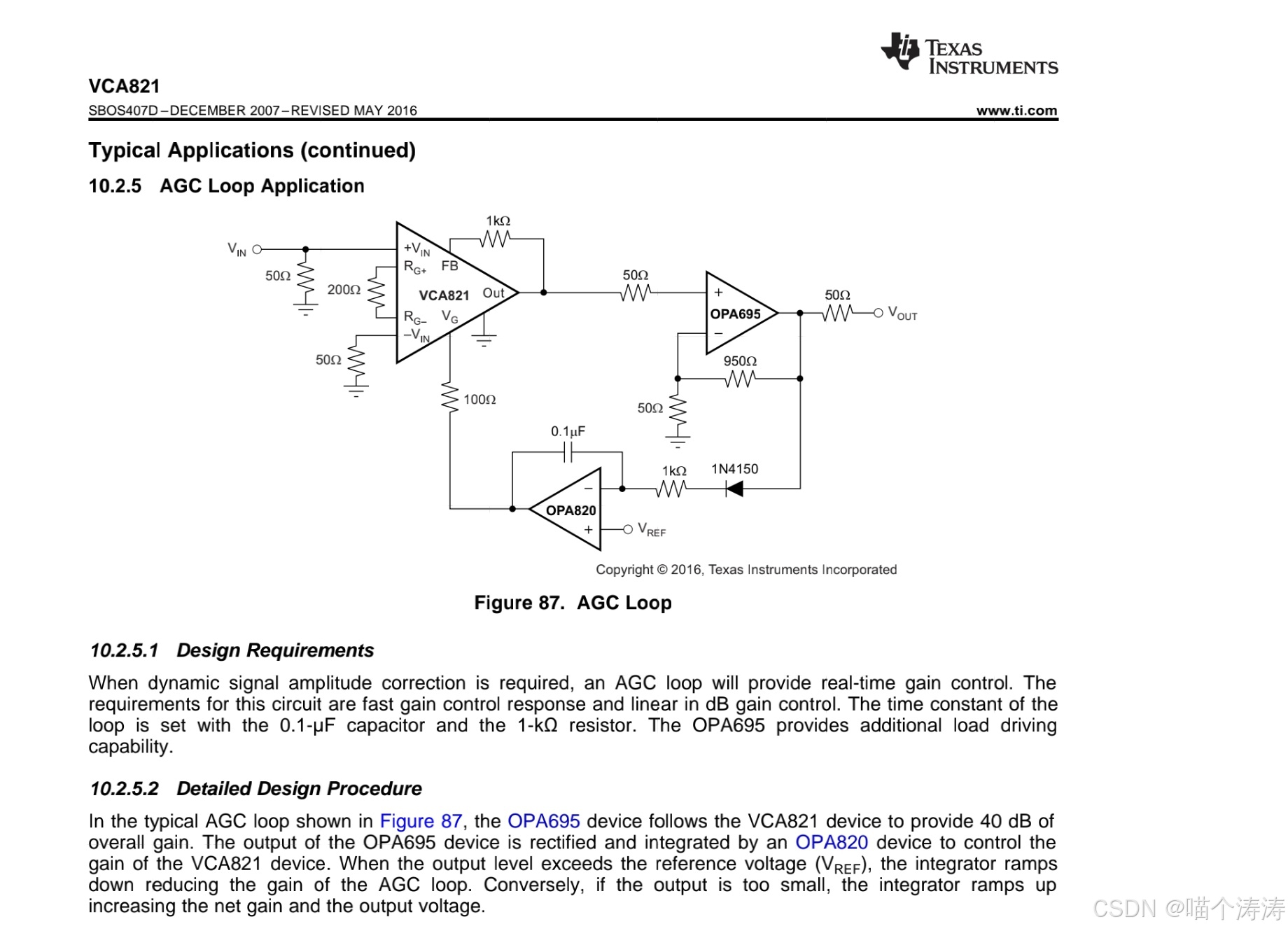

VCA821的数据手册中有一个AGC电路的运用例子喵

这里给出了设计要求和详细的设计步骤,(有些小伙伴可能看到英语就头疼,但是学习一点相关的英语词汇对阅读数据手册有着很大的提升喔),这两段的意思大概是说,当需要动态信号幅度校正时,AGC环路将提供实时增益控制,而环路的时间常数由0.1μF电容和1kΩ电阻设置。OPA695提供额外的负载驱动能力。OPA695连在VCA821后,提供40 dB的整体增益。OPA695的输出被OPA820整流和积分,来控制VCA821的增益。当输出电平超过参考电压(VREF)时,积分器电位逐渐降低,减少AGC环路的增益。相反,如果输出太小,积分器电位逐渐增加,增加净增益和输出电压。

那么问题就来了,这个电路是怎么实现这个功能的呢,我们来看OPA820部分的电路网络,它由一个电容,一个电阻,一个二极管组成,如果小伙伴们有一定的电路基础,那么应该可以立马联想到峰值检波电路,我个人认为在这里原理是差不多的,就算不知道峰值检波也没关系,我们把式子算出来不就好了

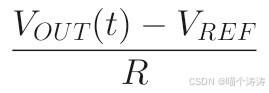

我们假设1k电阻右端的电压为Vout(t),那么电阻左端的电压就是Vref,那么通过电阻的电流

i(t)就是:

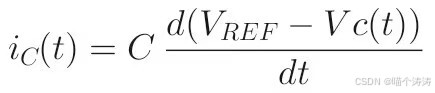

假设运放输出端电压为Vc(t),电压电流取关联参考方向,那么电容上的电流ic(t)就是:

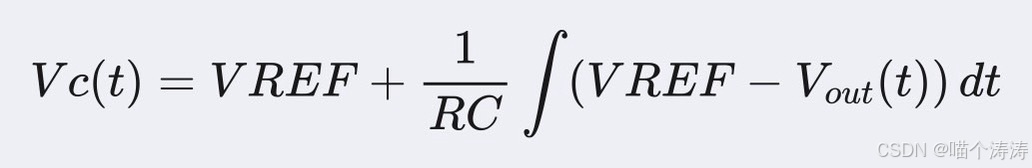

由ic(t)=i(t),将等式两边同时积分并整理:

就得到了Vc(t)的表达式,我们就会发现,当Vout小于Vref的时候,Vc就会增大,而Vout大于Vref的时候,Vc就会减小,而我们只需要将Vc连接到VCA821的Vg端,那么当Vc增大时,VCA821的增益便会增大,进而增大Vout,导致Vc减小,反之亦然,最终达到一个稳定的状态,即Vc = Vref,此时,VCA821的增益便被设置在了一个特定的大小,进而实现了自动增益控制。

这时候可能有人想问,那二极管是干嘛的嘞?

实际上,二极管在这里可以将信号负半周截断,将交流信号变为直流脉冲,如果不加二极管的话,电路中出现的反向电流将使积分器工作异常,让积分器无法实现负反馈的功能(可以仿真一下awa,或者将负半周代入公式算一遍,就会发现负半周信号使它变成了类似正反馈的情况),进而导致电路爆炸喵!

到了这里,我们就已经把电路的原理搞清楚了,至于该如何选取反馈电阻Rg与Rf,如何知道Vref与VCA821的增益之间的关系,我会在我的下一篇文章《怎么阅读数据手册呢?》结合数据手册的阅读方法告诉大家喵,大家可以关注喵个涛涛喵~(梅开二度喵~)

四、电路的Layout

PCB设计中,我们常说七分布局,三分布线,所以布局是很重要的,好的布局不仅可以简化走线,还可以提高电路的性能,那么我们应该如何进行该电路的布局呢?

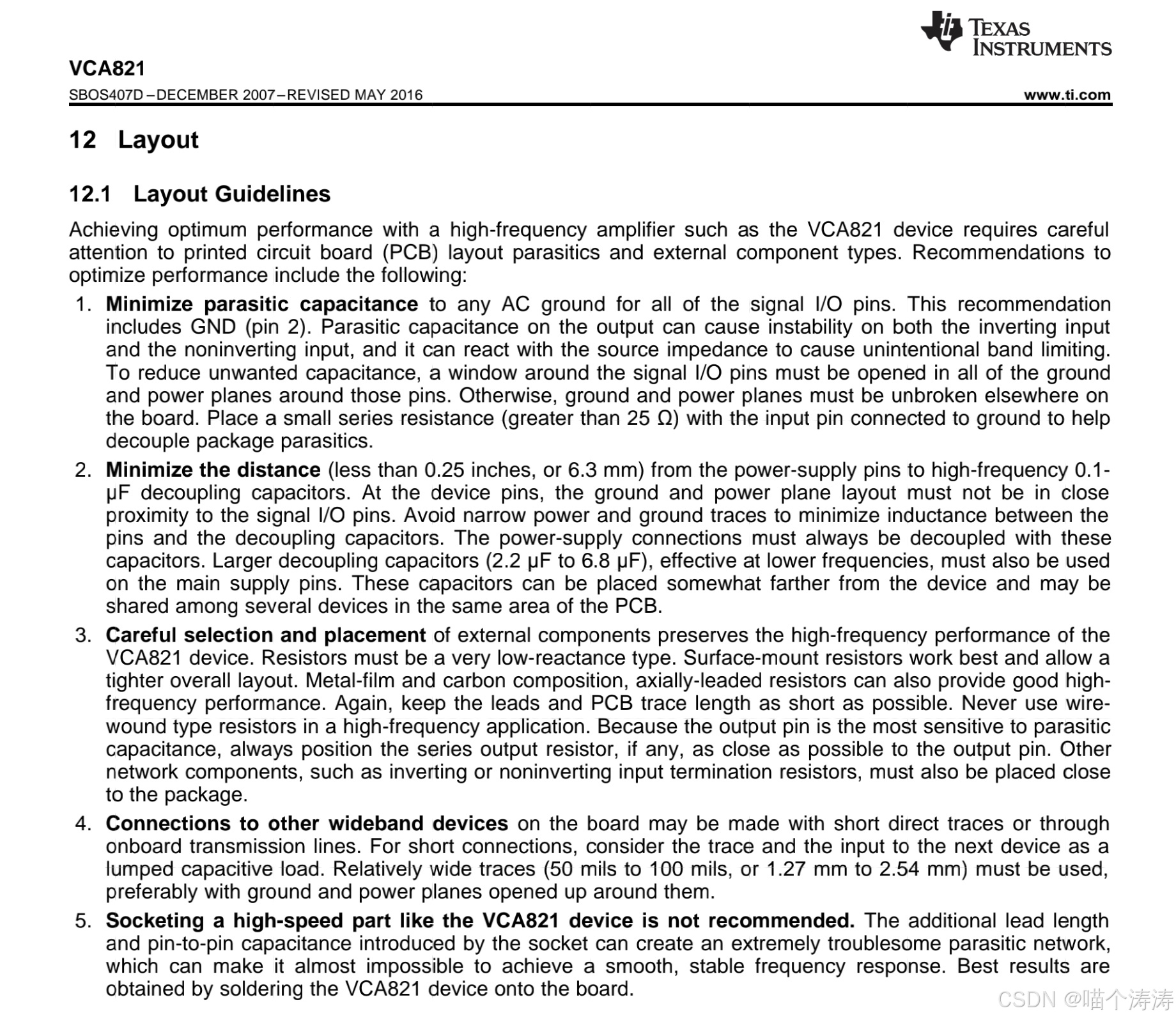

实际上数据手册有给出我们答案喵

我来给大家总结一下这里面的大致内容喵:

第一点是说要最小化信号I/O引脚到地的寄生电容,所有信号I/O引脚(包括地(GND,引脚2))的寄生电容必须最小化。具体做法就是在所有地平面和电源平面中,信号I/O引脚周围开一个窗口。此外,保证地平面和电源平面在板上的其他位置是完整的。在输入引脚连接到地时,放置一个小系列电阻(大于25Ω)可以去耦封装的寄生电容。

第二点是说地平面和电源平面的布局必须不要靠近信号I/O引脚,避免狭窄的电源和地走线,以最小化引脚和去耦电容之间的电感。然后就是电源输入,遵循大电容靠近电源输入端,远离器件,而在器件的电源引脚处放置小电容,并且尽量靠近电源引脚喵(小于6.3mm)。

第三点是说选择和放置外部元件可以保持VCA821的高频性能。就使用表面贴装电阻效果最好,可以紧凑的整体布局。同时保持引线和PCB走线长度尽可能短,不要使用绕线型电阻。将输出电阻尽可能靠近输出引脚放置,这是因为这个电阻可以去耦寄生电容喵,就是第一点的原理。其他网络元件,如反相或同相输入端接电阻,也必须靠近封装放置。

第四点是说板上的其他设备可以通过短的直接走线连接,对于短连接,可以将走线和输入到下一个设备视为一个集总电容负载(实际上就是将走线作为电容来使用)。建议使用相对较宽的走线(50mil到100mil,或1.27mm到2.54mm),最好在周围打开地平面和电源平面。(这里我觉得其实有点奇怪喵,因为50mil超级大喵!所以我并没有开到50mil那么大喵~)

最后就是不要插接高速器件喵,这个应该很好理解喵

五、原理图与实物测试

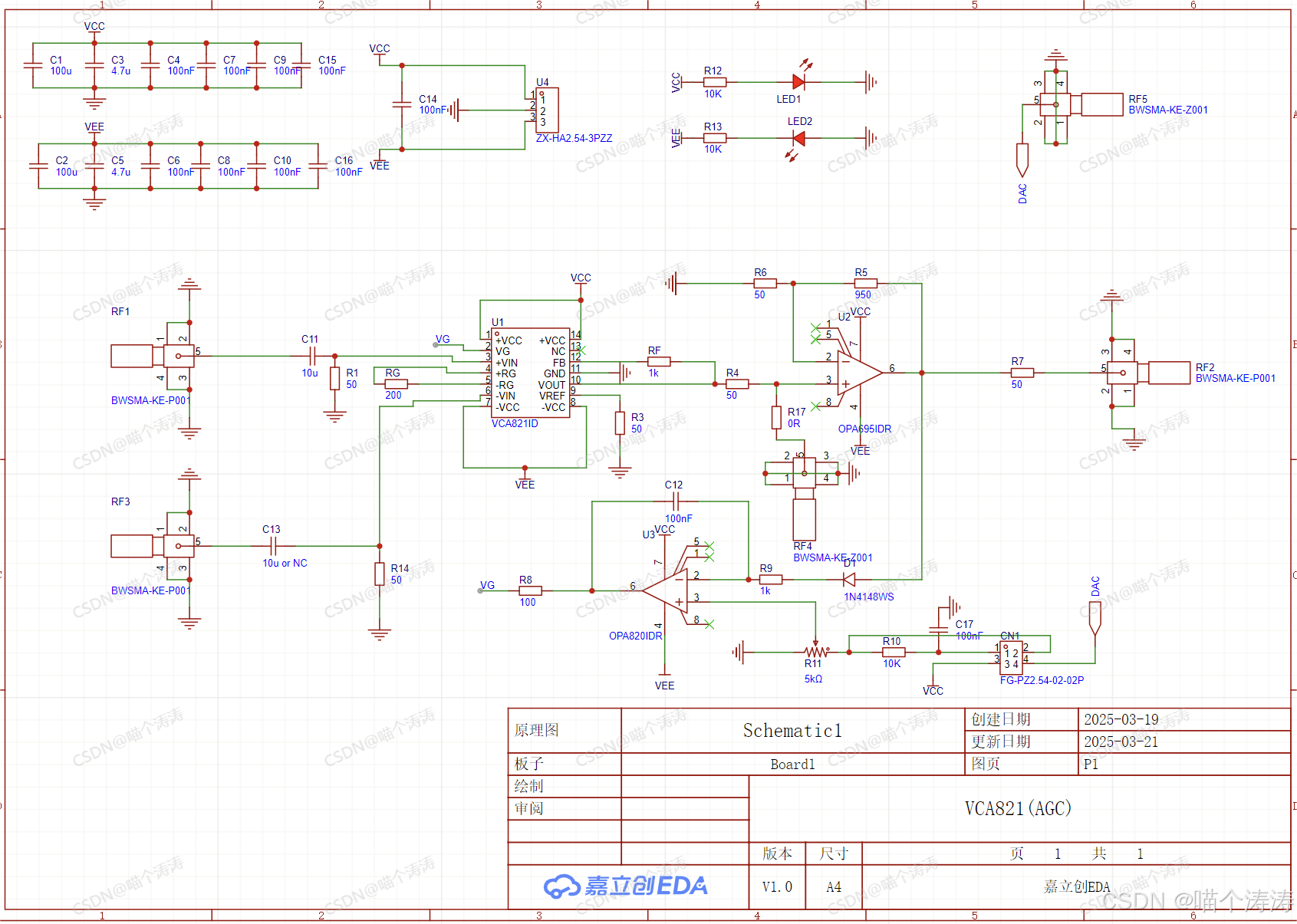

根据上面的说法,那么说明我们的PCB应该要开四层板才可以有完整的电源平面与地平面喵,而依据上面的原则,我们就可以根据我们设计的电路图来进行电路的布局啦!下面是博主的电路原理图和实物图。

添加了DAC入口用于程控Vref的值,改变增益大小。

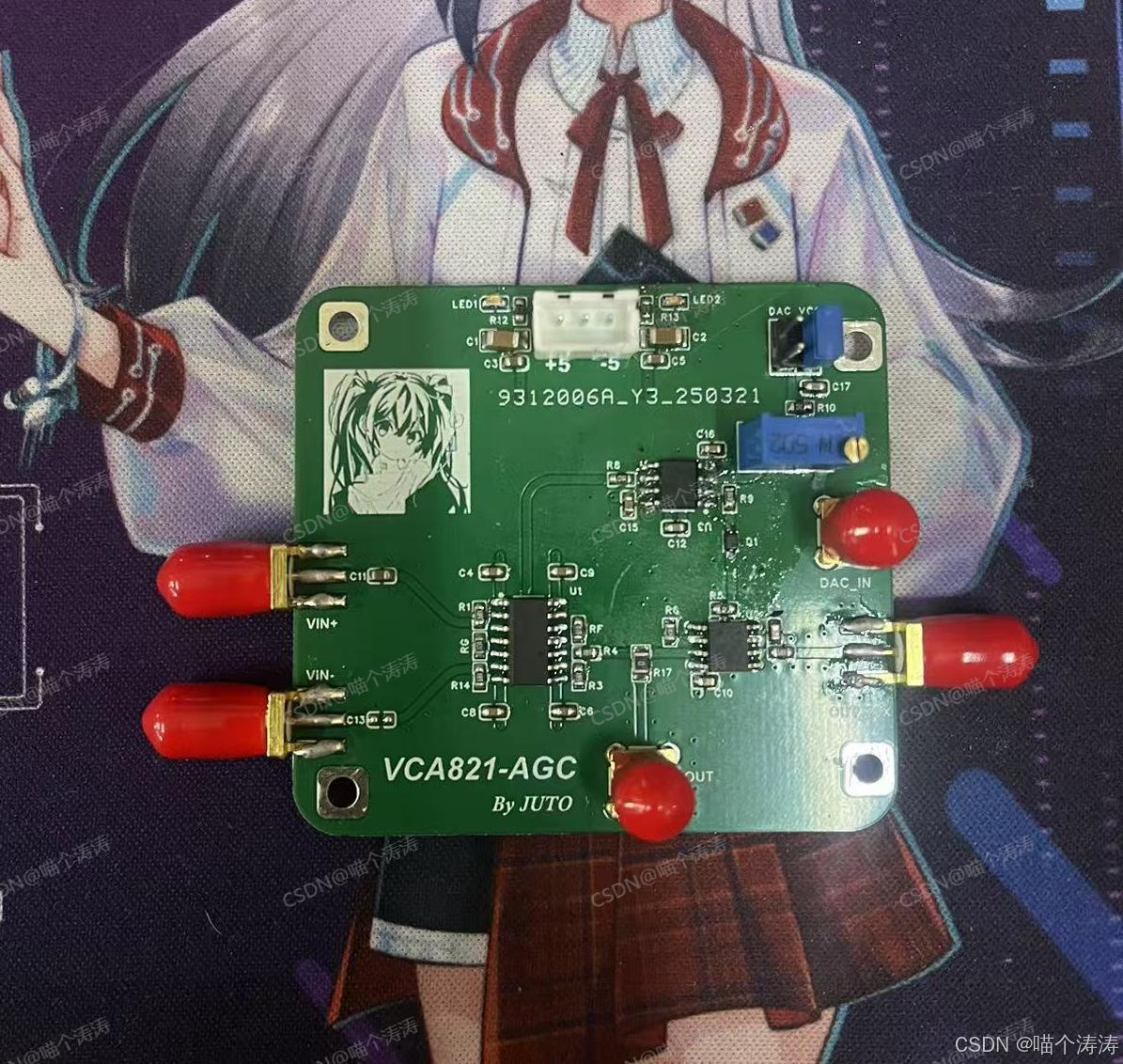

实物图

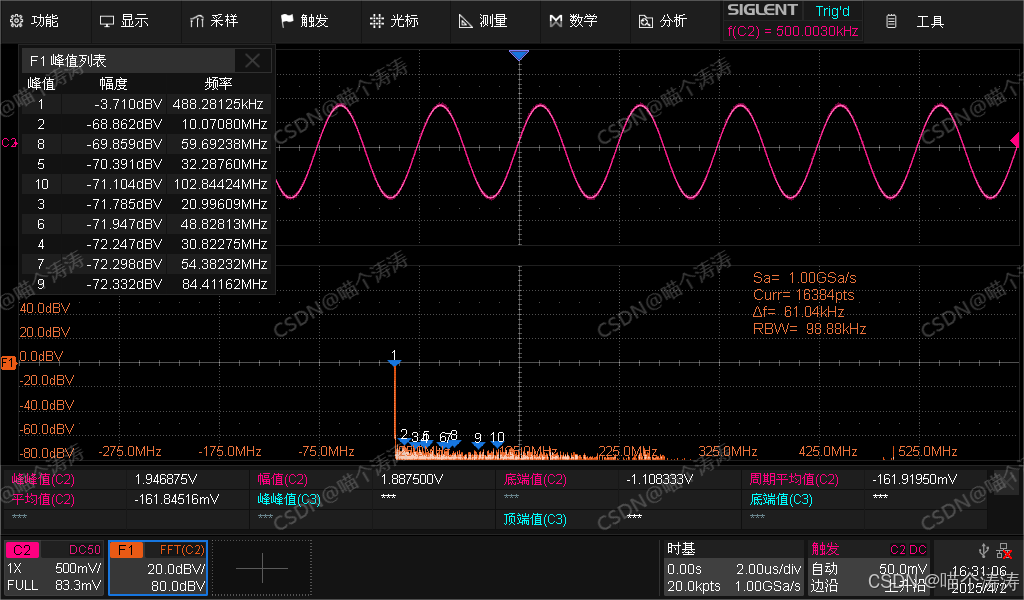

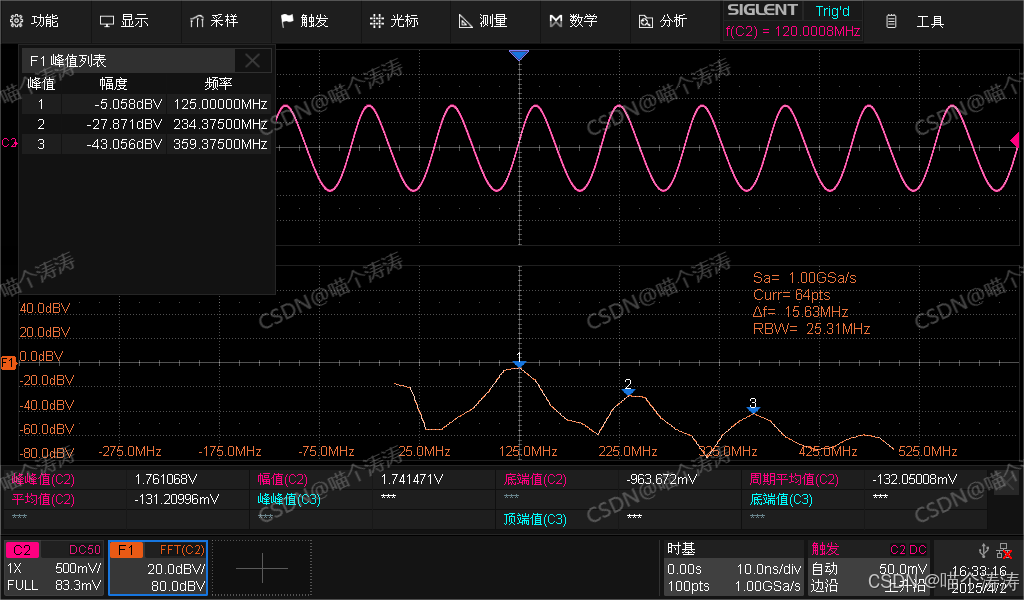

经过测试,VCA821的直接输出端非常干净,在120MHz的输入下二次谐波与三次谐波的衰减均为40dB以上,而OPA695输出端2次谐波衰减仅为20dB,可能是OPA695电路设计或者Layout的问题,但是在10MHz内的低频端,性能十分优秀,而在10MHz到120MHz内,增益的大小略有下降,但是波形失真并不明显,还算能用。(测试时输入信号在30mV到500mV之间)

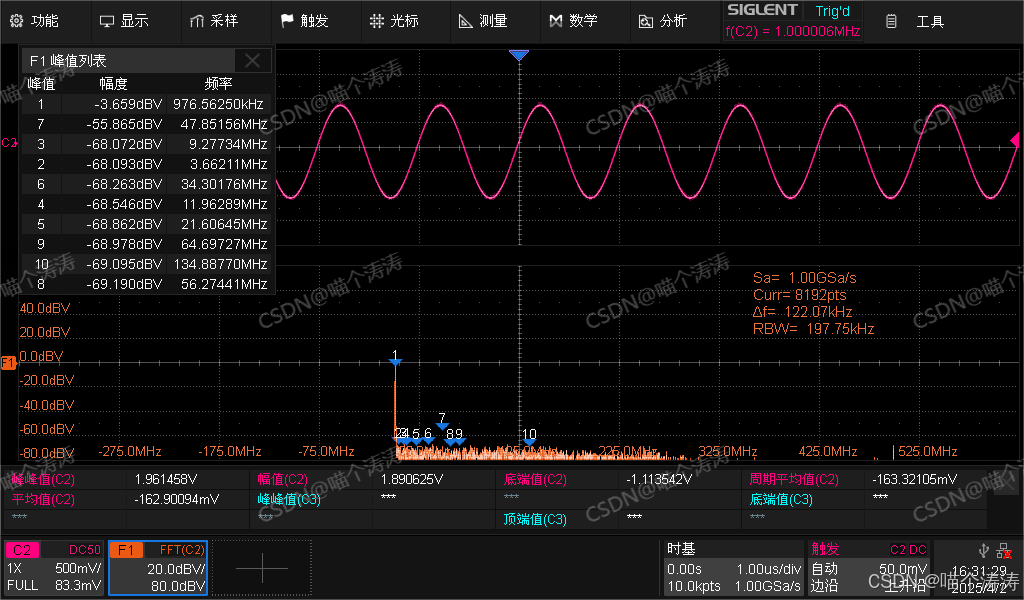

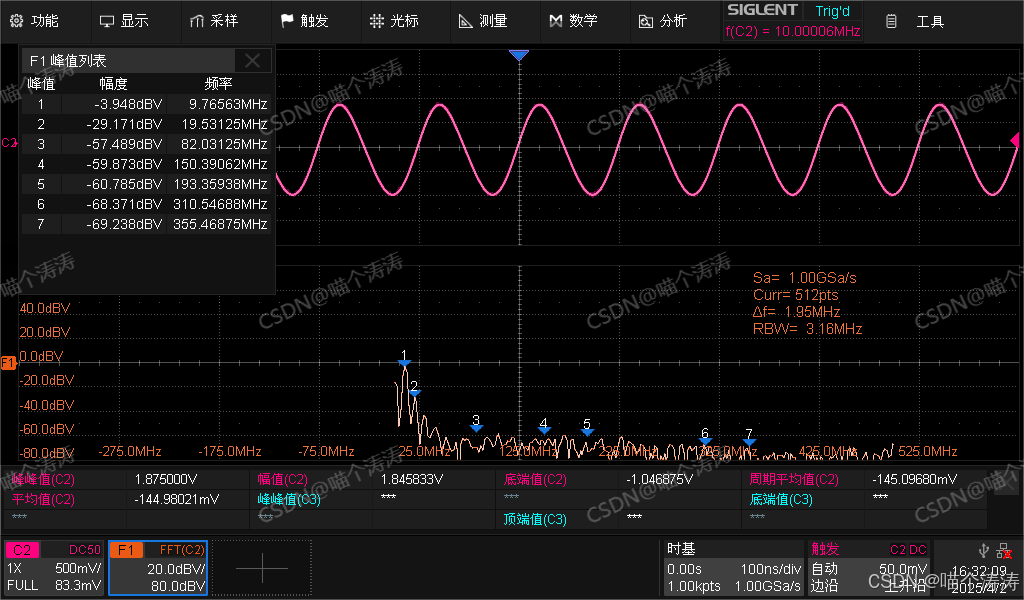

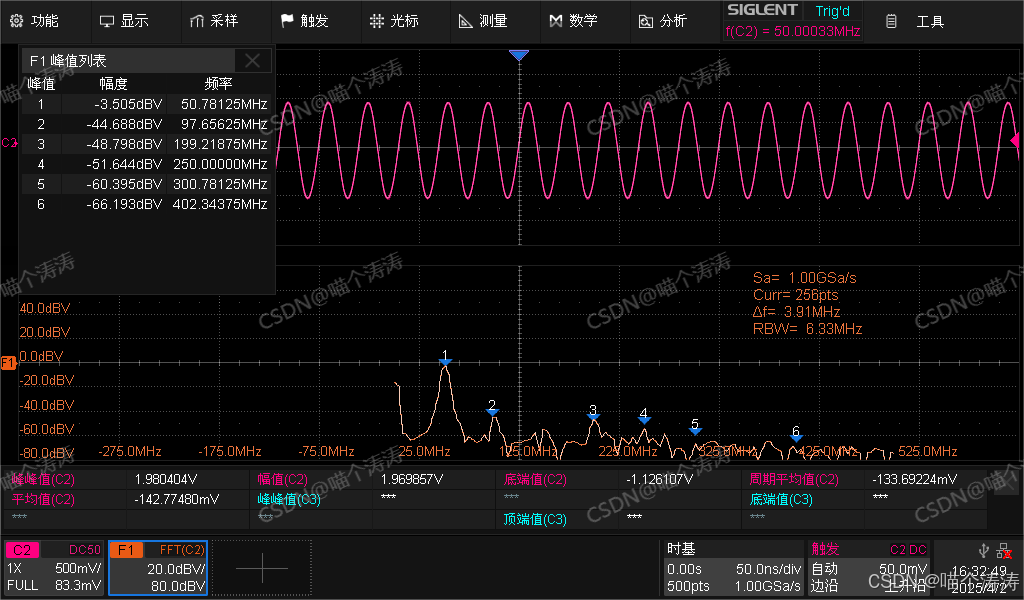

因为VCA821的直接输出端波形几乎没有任何失真,所以就不上传照片了,就上传波形略差一点的OPA695输出端的信号,因为低频端性能非常好,从500kHz开始。

10MHz后2次谐波和3次谐波压不住了,波形略有失真,峰峰值略有下降。

那这篇文章到这里就结束啦, 等创作等级达标了博主会将PCB文件上传到vip文章里喵~(画板子加测试也是很辛苦的喵,希望大家谅解喵qwq)

希望这篇文章能帮助小伙伴喵~

喜欢的话,关注喵个涛涛喵!

735

735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?