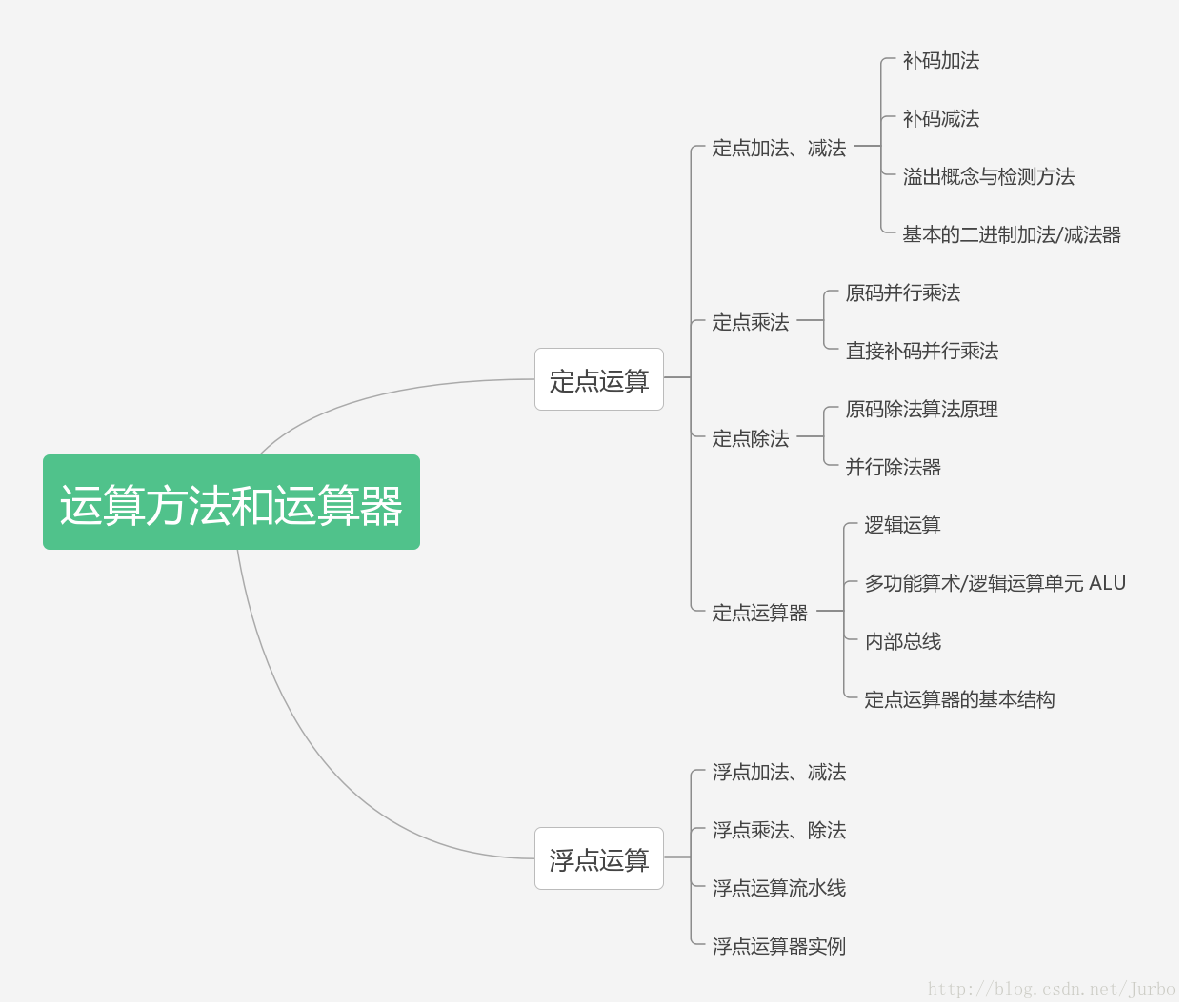

本文内容:定点运算,浮点运算,定点运算器和浮点运算器。

思维导图

在上篇文章中 计算机组成原理:数据与文字的表示方法 ,我们已经知道了数据与文字在计算机中是怎么表示的。在这一篇中,我们将知道数据是如何在计算机中运算的(运算方法),及是如何实现的(运算器)。

本文介绍定点运算和浮点运算及其运算器。定点运算中包括定点加法、减法;定点乘法;定点除法;定点运算器。浮点运算中包括浮点加法、减法;浮点乘法;浮点除法;浮点运算器。

定点运算

定点加法、减法

在上篇文章中 计算机组成原理:数据与文字的表示方法,我们已经介绍了数的补码表示法,负数用补码表示后,就可以和正数一样来处理。这样,运算器里只需要一个加法器就可以了,不必为了负数的加法运算,再配一个减法器。

定点数的加法、减法,实际上就是补码加法、减法。

补码加法

补码加法运算基本公式:

- 定点整数: [x+y]补 = [x]补 + [y]补 (mod 2n+1 )

- 定点小数: [x+y]补 = [x]补 + [y]补 (mod 2 )

简单来说,只需将符号位和数值部分一起参与运算,并且将符号位产生的进位丢掉即可

证明:

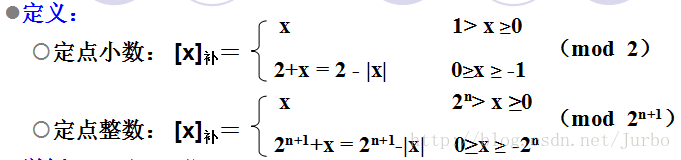

(1)证明依据:补码的定义

若 定点整数的补码形式为 x =

(2)证明思路:分三种情况。

x、y均为正值(x﹥0,y﹥0)

x、y一正一负(x﹥0,y﹤0 或者x<0,y>0)

x、y均为负值(x<0,y<0)

证明定点小数的补码加法:(定点整数的证明类似,此处不再证明)

1、x﹥0,y﹥0

[x]补 + [y]补 = x+y = [x+y]补 (mod 2 )

2、x﹥0,y﹤0 (x<0,y>0 的证明与此类似)

根据定义

所以

[x]补 + [y]补 = x+2+y = 2+(x+y)

这个地方要考虑 进位的问题。

当 x+y>0 时,2+(x+y) > 2 ,进位 2 必丢失;

故 [x]补 + [y]补 = x+y = [x+y]补 (mod 2)

当 x+y<0 时,2+(x+y) < 2 ;

故 [x]补 + [y]补 = 2+(x+y) = [x+y]补 (mod 2)

3、x<0,y<0

根据定义 [x]补 = 2+x, [y]补 = 2+y

所以

[x]补

+

[y]补

= 2+x+2+y

= 2+(2+x+y)

= 2+

[x+y]补

(mod 2)

=

[x+y]补

注:不懂mod 2 的可以转至上一篇 计算机组成原理:数据与文字的表示方法 查看补码的推导

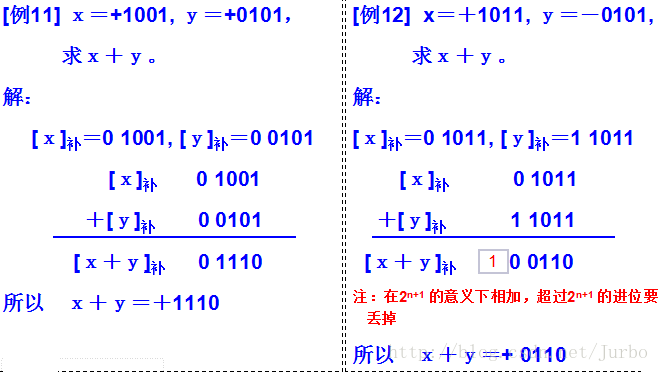

定点数补码加法举例

补码减法

补码减法运算基本公式:

- 定点整数: [x−y]补 = [x]补 - [y]补 = [x]补 + [−y]补 (mod 2n+1 )

- 定点小数: [x−y]补 = [x]补 - [y]补 = [x]补 + [−y]补 (mod 2 )

证明:只需要证明 已证明

[x+y]补

=

[x]补

+

[y]补

故

[y]补

=

[x]补

+

[y]补

-

[x]补

=

[x+y]补

-

[x]补

又

[x−y]补

=

[x+(−y)]补

=

[x]补

+

[−y]补

故

[−y]补

=

[x−y]补

-

[x]补

可得

[y]补

+

[−y]补

即证。

[−y]补

等于 对

[y]补

包括符号位取反且最末位加1 定点数补码减法举例 例1:已知

x1

= - 1110,

x2

= + 1101,求:

[x1]补

,

[−x1]补

,

[x2]补

,

[−x2]补

。 解:

[x1]补

= 1 0010

[−x1]补

= 0 1101+0 0001= 0 1110

[x2]补

= 0 1101

[−x2]补

=1 0010+0 0001= 1 0011 例2:x=+1101,y=+0110,求x-y。 解:

[x]补

= 0 1101,

[y]补

= 0 0110,

[−y]补

= 1 1010

[x−y]补

故 x-y=+0111 在定点整数机器中,数的表示范围

−2n

< x <

2n−1

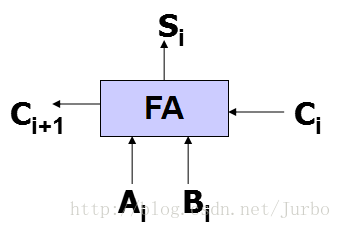

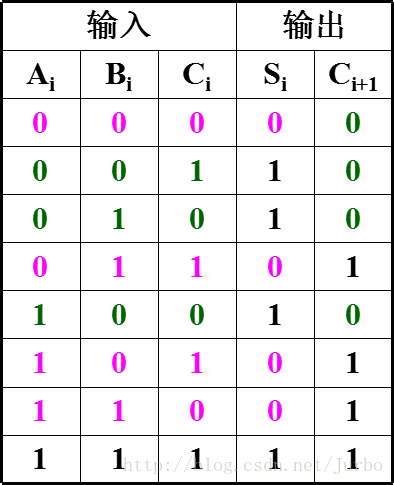

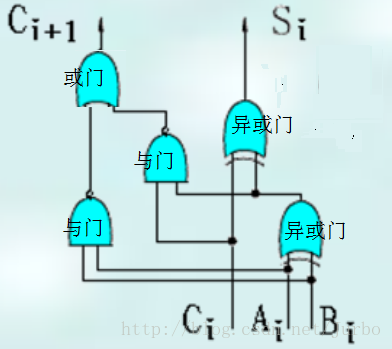

(补码表示)。在运算过程中。若数的大小超出了定点数能表示的范围,称为“溢出”。 上溢(正溢):数据大于机器所能表示的最大正数; 下溢(负溢):数据小于机器所能表示的最小负数 例如:4位补码表示的定点整数,范围为[-8,+7] 溢出判别方法 溢出判别方法——直接判别法 方法: 特点:硬件实现较复杂; 举例: 溢出判别方法——变形补码判别法(双符号位法) 变形补码,也叫模4补码:采用双符号位表示补码 判别方法: 特点:硬件实现简单,只需对结果符号位进行异或 举例: 溢出判别方法——进位判别法(单符号位法) 判别方法:最高数值位的进位与符号位的进位是否相同; 判别公式:V =

Cf

⊕

Cn−1

,其中

Cf

为符号位产生的进位,

Cn−1

为最高数值位产生的进位 简单来说,当最高有效位产生进位而符号位无进位时,产生正溢;当最高有效位无进位而符号位有进位时,产生负溢, 可以用异或门实现。 1 位 二进制数据的全加器: 1 位 二进制数据的全加器示意图: 全加运算的真值表如图所示: 根据真值表推出两个输出的逻辑表达式 方法:将真值表中函数值等于1的变量组合选出来;对于每一个组合,凡取值为1的变量写成原变量,取值为0的变量写成反变量,各变量相乘后得到一个乘积项;最后,把各个组合对应的乘积项相加,进行化简后,就得到了相应的逻辑表达式。 两个输出端的逻辑表达式

Si

=

Ai¯¯¯¯

Bi¯¯¯¯

Ci

+

Ai¯¯¯¯

Bi

Ci¯¯¯¯

+

Ai

Bi¯¯¯¯

Ci¯¯¯¯

+

Ai

Bi

Ci

=

Ai

⊕

Bi

⊕

Ci

Ci+1

=

Ai¯¯¯¯

Bi

Ci

+

Ai

Bi¯¯¯¯

Ci

+

Ai

Bi

Ci¯¯¯¯

+

Ai

Bi

Ci

=

Ai

Bi

+

Bi

Ci

+

Ci

Ai

=

Ai

Bi

+(

Ai

⊕

Bi

)

Ci

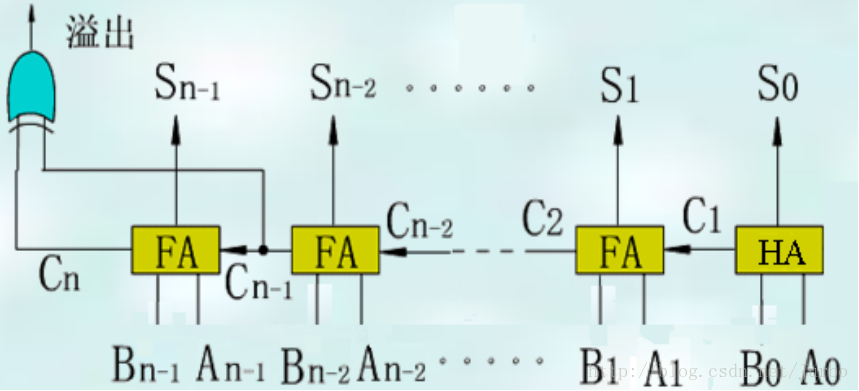

根据逻辑表达式,可画出全加器逻辑结构,如下图所示: 多位二进制数据加法器 两个 n 位的数据 A =

An−1

An−2

….

A1

A0

,B =

Bn−1

Bn−2

….

B1

B0

和 S =

Sn−1

Sn−2

….

S1

S0

采用 进位判别法 判断数据的溢出:V =

Cn

⊕

Cn−1

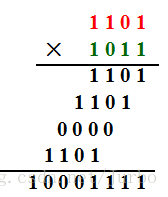

多位二进制数据加法器逻辑图如下所示: 多位二进制数据加法/减法器 加法转减法的异或门: 多位二进制数据加法/减法器逻辑图 如下所示: 多位二进制加法/减法器的输出延迟 分析笔算乘法 在定点计算机中,两个原码表示的数相乘的运算规则是:乘积的符号位 由两数的符号位按异或运算得到,而乘积的数值部分 则是两个正数相乘之积。 设 n 位被乘数和乘数用定点整数表示(

xf

,

yf

为乘数符号): 乘积符号的运算法则 是:同号相乘为正,异号相乘为负。积的符号可按“异或”运算得到。 即:异或运算,异号为1,则为负数;同号为0,则为正数。 例子: 特点: 设有两个不带符号的二进制整数: A =

am−1

….

a1

a0

B =

bn−1

….

b1

b0

它们的真值分别为 a 和 b,即 a =

∑m−1i=0ai2i

b =

∑n−1j=0nj2j

在二进制乘法中,被乘数 A 与乘数 B 相乘,产生 m+n 位乘积 P: P =

pm+n−1

….

p1

p0

乘积 P 的真值为: P = ab = (

∑m−1i=0ai2i

)(

∑n−1j=0nj2j

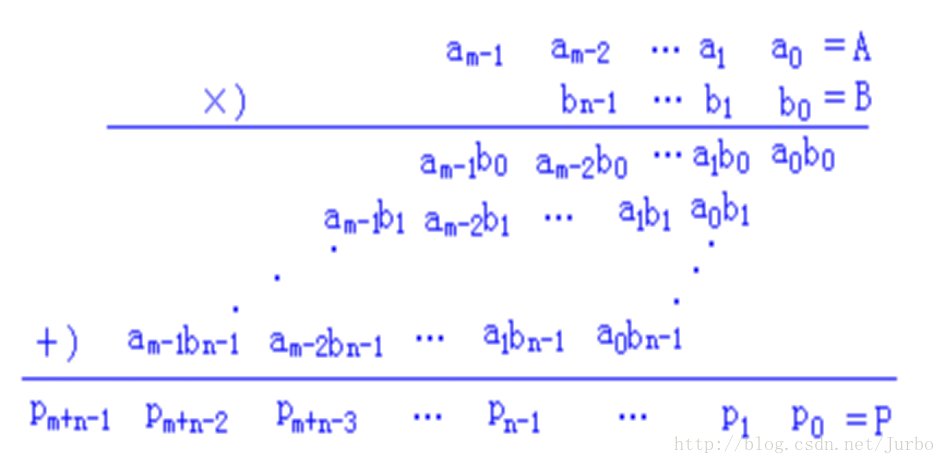

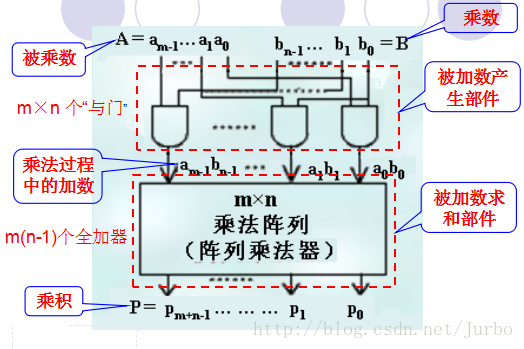

) 实现这个乘法过程所需要的操作和人们的习惯方法非常类似,二进制乘法的运算过程 上述过程说明了在 m 位 × n 位 不带符号的阵列乘法 中的被加数矩阵。每一个部分乘积项(位积)

ai

bj

叫做一个被加数。这 m×n 个被加数

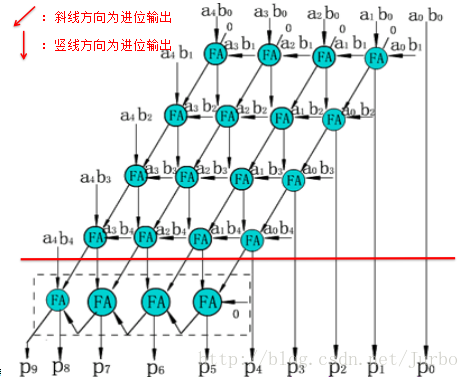

ai

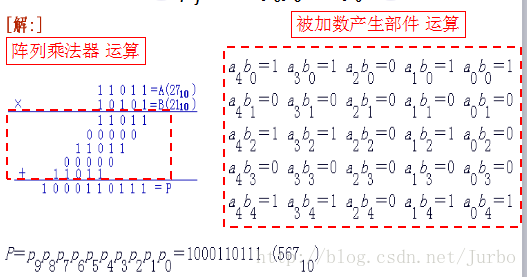

bj

可以用 m×n 个 “与”门并行地产生。如下图上半部分所示。 m×n位不带符号的阵列乘法器逻辑框图 接下来说明,并行阵列乘法器的基本原理。下面以 5×5 位并行阵列乘法器为例,来说明。 首先来看看 5×5 位并行阵列乘法器电路,如下所示 其中 FA 是前面 讲过的一位二进制全加器。FA 的斜线方向为进位输出,竖线方向为和输出,而所有 被加数项 的排列和前述 A×B = P 乘法过程中的被加数矩阵相同。图中用虚线围住的阵列中最后一行构成了一个行波进位加法器。 再通过 5×5 二进制例题讲解。 例题:已知两个不带符号的二进制整数A=11011,B=10101,求每一部分乘积项

ai

bj

的值与

p9

p8

….

p0

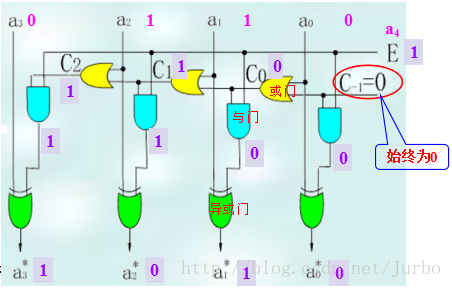

的值 在介绍带符号的阵列乘法器基本原理前,我们先来看看算术运算部件设计中经常用到的求补电路——对2求补器(即对模为2的数进行求补操作——二进制)。 下图示出了一个具有使能控制的二进制对2求补器的电路图 其逻辑表达式如下:

C−1

= 0,

Ci

=

ai

+

Ci−1

ai∗

=

ai

⊕

E

特点: 对2求补电路的原理 对2求补时,采用按位扫描技术来执行所需要的求补操作。令 A =

an

…

a1

a0

是给定的 n+1 位带符号的数,要求确定它的补码形式。进行求补的方法 就是从数的最右端

a0

开始,由右向左,直到找出第一个“1”。例如

ai

= 1,这样

ai

以右的每一位,包括

ai

自己,都保持不变,而

ai

以左 的每一位都求反,即 1变0,0变1。基于此,横向链式电路中的 第 i 扫描级的输出

Ci

为 1 的条件是:第 i 级的输入位

ai

= 1,或者第 i 级链式输入

Ci−1

= 1.另外,最右端的起始链式输入

C−1

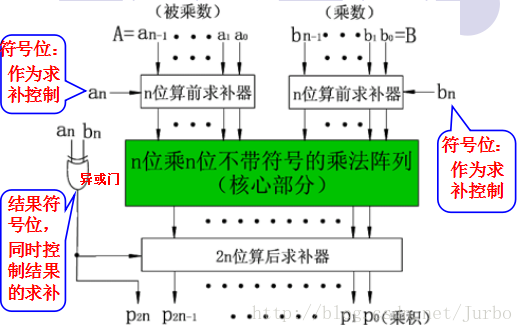

必须永远置 0。当 控制信号 E 为 1 时(即该数的符号位为1,即负数时),启动对2求补的操作;当 控制信号 E 为 0 时(正数)时,输入和输出相等。 例题: 例如,在一个 4位的对2求补器中,如果数为:1 0110。 那么,符号位 1 作为控制信号,进行对2求补操作,输入是 0110,输出将是 1010。 (注意,由此我们可以看出,对2求补电路 的功能是求二进制数的补码,但是输出时,只有数据位,不包含符号位。) 现在我们来讨论带符号的阵列乘法器。下图示出了(n+1)位 × (n+1)位带求补器的阵列乘法器逻辑方框图: 设 A =

an

an−1

…

a1

a0

和 B =

bn

bn−1

…

b1

b0

均为用定点表示的(n+1)位带符号整数。由上图可以看到,在进行完必要的求补操作以后,A 和 B 的数值位传送给 n位 × n位 不带符号的阵列乘法器,并由此产生 2n 位乘积为: 其中,

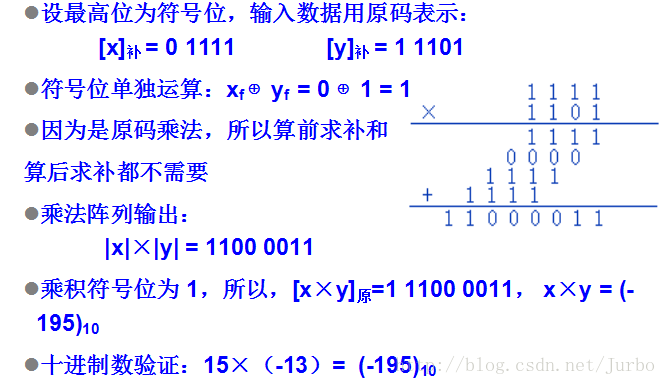

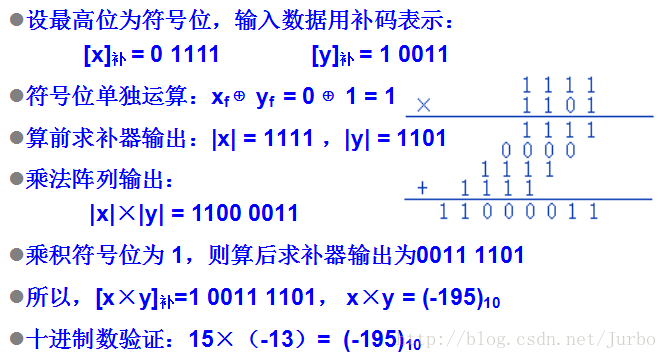

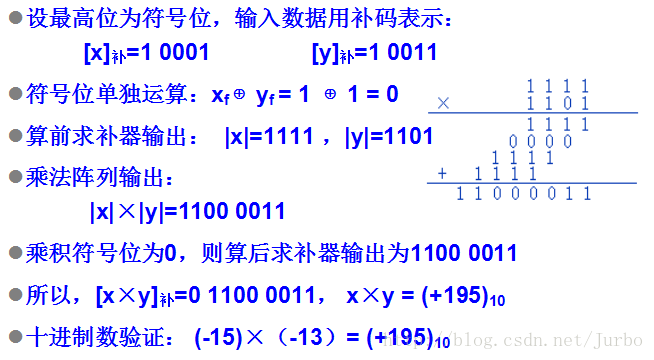

p2n−1

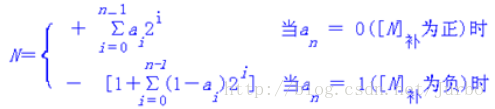

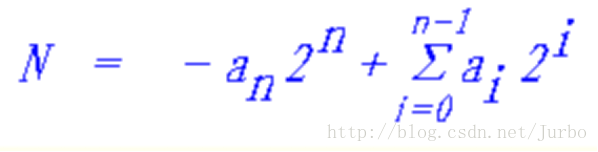

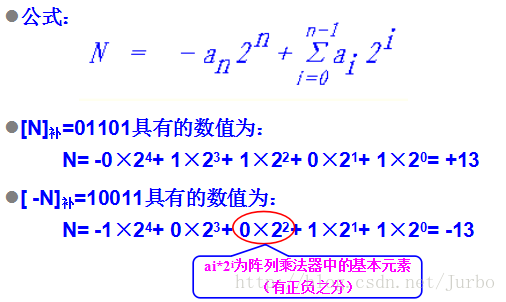

为符号位 带求补器的阵列乘法器,既使用于原码乘法,也使用于间接的补码乘法。不过,在原码乘法中,算前求补和算后求补都不需要,因为输入数据是立即可用的。而间接的补码阵列乘法却需要 3个求补器。 以下将介绍 3 个求补器的作用: 其中两个算前求补器的作用 是:将两个操作数 A 和 B 在被不带符号的乘法阵列(核心部件)相乘之前。若该数的符号位为1(负数),则对它的数值位进行求补操作,并将 求补后的数值位 输入给 不带符号的乘法阵列(核心部件);若该数的符号位为0(正数),则将它的数值位输入给 不带符号的乘法阵列(核心部件)。 算后求补器的作用 是:当两个操作数的符号不一致时(如01,10 相乘后,结果为负数,符号位为0),对 乘法阵列得到的结果,进行求补操作;当两个操作数的符号一致时(正数),则直接将 乘法阵列得到的结果 输出。 以下将给出 3个例题来理解 带符号的阵列乘法器 例 1:设 x=+15,y=-13,用带求补器的原码阵列乘法器求出乘积 x·y=? 例 2:设 x=+15,y=-13,用带求补器的补码阵列乘法器求出乘积 x·y=? 例 3: 设 x= -15,y=-13,用带求补器的补码阵列乘法器求出乘积 x·y=? 直接补码并行乘法——符号位参与运算,可以完成补码数的“直接”乘法,而不需要计算原值。 补码与真值的转换公式 假设有 N+1 位定点补码整数

[N]补

=

an

an−1

…

a1

a0

,其中

an

为符号位。根据

[N]补

的符号,补码数

[N]补

和 真值 N 的关系可以表示为: 若把负权因数

−2n

强加到符号位

an

上,那么就可以把上述方程组中的两个位值表达式合并成下面的统一形式: 例题:已知

[N]补

= 01101,

[−N]补

= 10011,求

[N]补

和

[−N]补

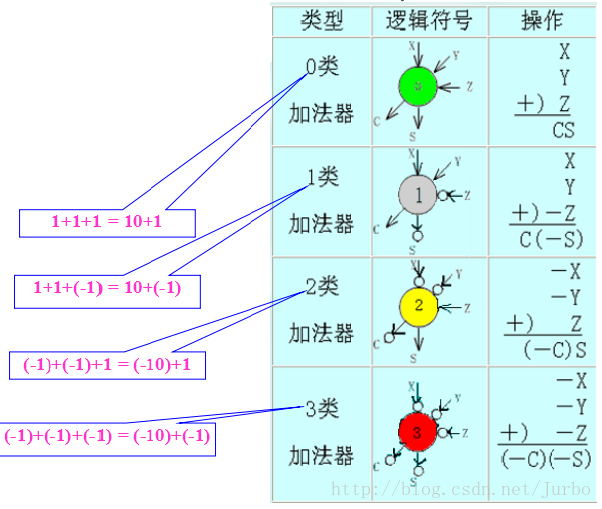

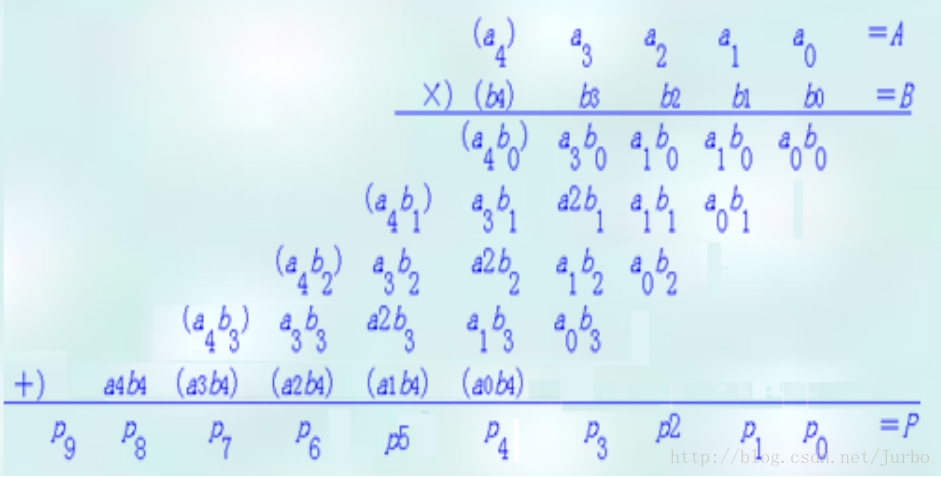

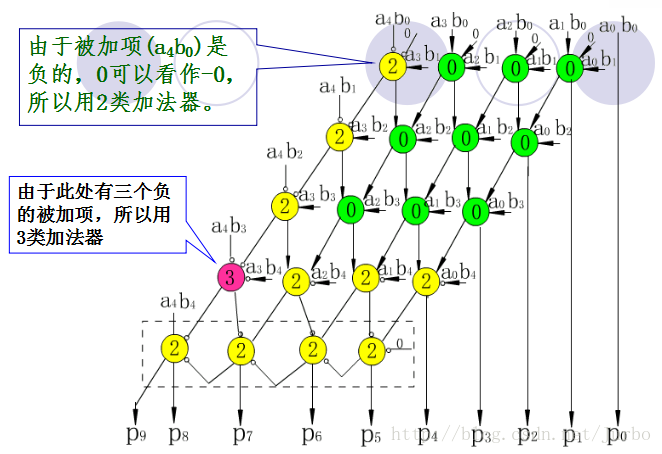

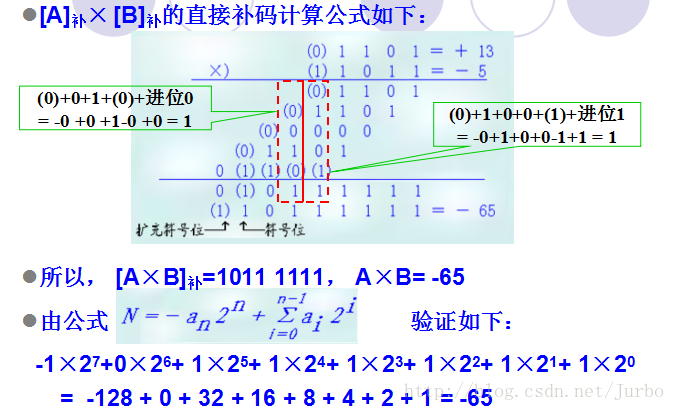

具有的数值。 一般化的全加器格式 通过把正权或负权加到输入/输出端,可以归纳出四类加法单元。 直接补码阵列乘法器 利用混合型的全加器就可以构成直接补码阵列乘法器。设被乘数 A 和乘数 B 是两个 5 位的二进制补码,即 它们具有带负权的符号位

a4

和

b4

,并用括号标注。如果我们用括号来标注负的被加项,例(

ai

bj

),那么 A 和 B 相乘过程中所包括的操作步骤如下面矩阵所示: 5 位 × 5 位 的直接补码阵列乘法器逻辑原理如下图所示: 例题:设

[A]补

=

(01101)2

,

[B]补

=

(11011)2

,求

[A×B]补

= ? 四种基本的逻辑运算 在 本文定点加法、减法 中,我们已经知道 一位全加器(FA)的逻辑表达式为:

Fi

=

Ai

⊕

Bi

⊕

Ci

Ci+1

=

Ai

Bi

+(

Ai

⊕

Bi

)

Ci

(

Fi

是第 i 位的和,

Ai

和

Bi

是第 i 位的被加数和加数,

Ci

是第 i 位的进位输入,

Ci+1

是第 i 位的进位输出) ALU 设计思想: ALU 逻辑结构原理框图: 因此,一位算术/逻辑运算单元的逻辑表达式为:

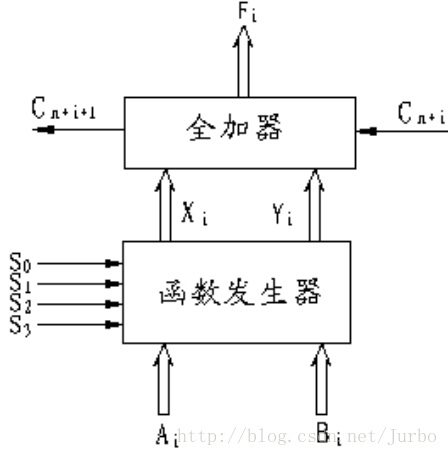

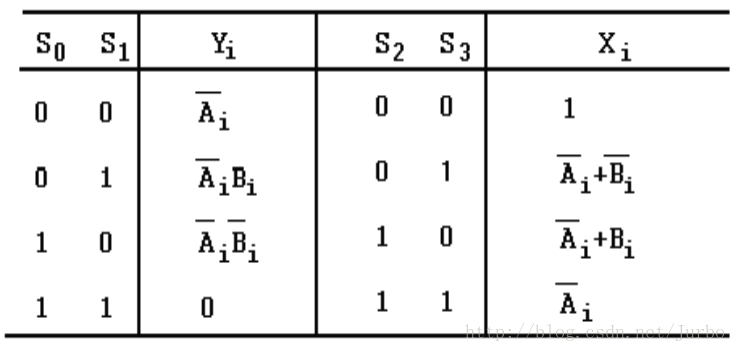

Fi

=

Xi

⊕

Yi

⊕

Cn+i

Cn+i+1

=

Xi

Yi

+

Yi

Cn+i

+

Cn+i

Xi

Xi

Yi

与控制参数和输入量的关系 74181ALU 算术/逻辑运算功能表 设有两个浮点数 x 和 y,它们分别为 x =

2Ex

·

Mx

其中,

Ex

和

Ey

分别为数 x 和 y 的阶码,

Mx

和

My

为数 x 和 y 的尾数。 两浮点数进行加法和减法的运算规则是: z = x ± y = (

Mx

2Ex−Ey

±

My

)

2Ey

,

Ex

<=

Ey

浮点数加减运算的步骤: 比较阶码大小并完成对阶 具体操作 求阶差 △E =

Ex

-

Ey

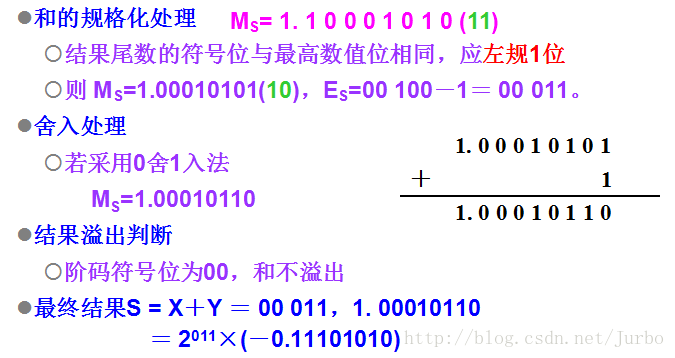

调整阶码较小的数据 结果规格化 当尾数运算结果出现下面情况时,需要规格化 结果的舍入处理 在对阶或向右规格化时,尾数要向右移位。这样,会使加数或结果的尾数会被丢掉,造成一定误差。因此,要进行舍入处理。 常用两种舍入处理方法: 结果的溢出判断 例题:设 x =

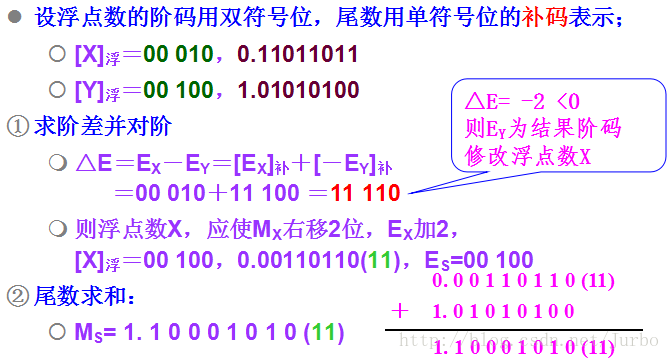

2010×0.11011011

,y =

2100×(−0.10101100)

,求 x + y 解: 设有两个浮点数 x 和 y,它们分别为 x =

2Ex

·

Mx

其中,

Ex

和

Ey

分别为数 x 和 y 的阶码,

Mx

和

My

为数 x 和 y 的尾数。 浮点数乘除运算的步骤

=

[x+y]补

+

[x−y]补

-

[x]补

-

[x]补

=

[x+y+x−y]补

-

[x]补

-

[x]补

=

[x+x]补

-

[x]补

-

[x]补

= 0

=

[x]补

+

[−y]补

= 0 1101 +1 1010

= 10 0111

= 0 0111(符号位产生的进位舍去)溢出概念与检测方法

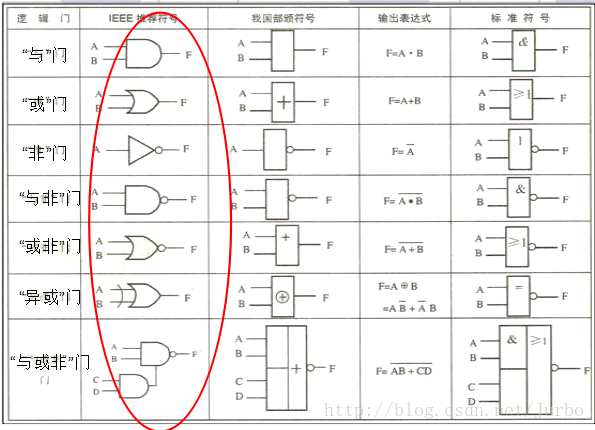

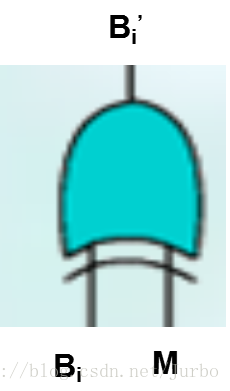

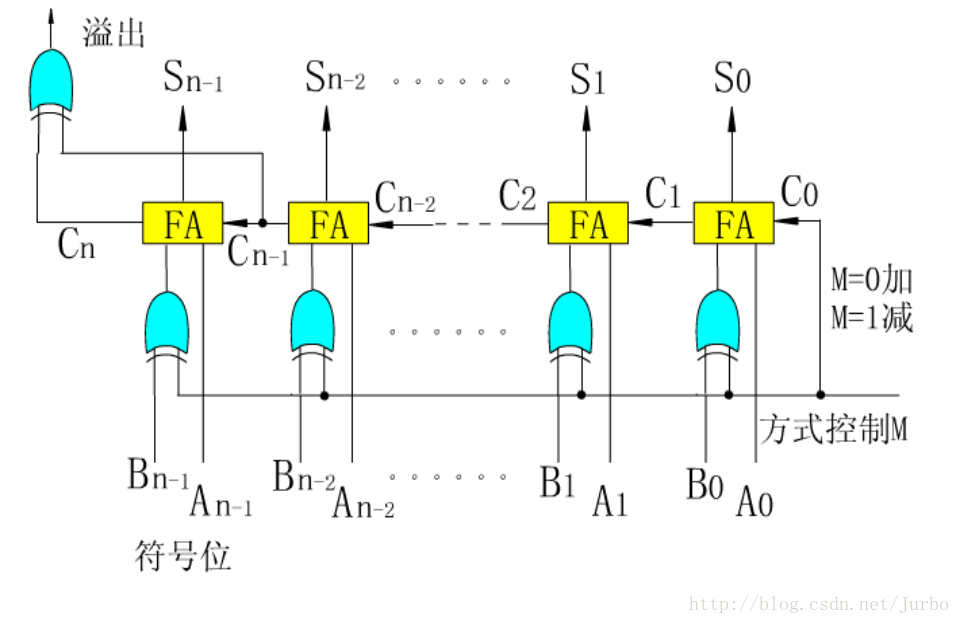

回顾逻辑门符号

基本的二进制加法/减法器

当 M=0 时,

Bi′

=

Bi

;

当 M=1时,

Bi′

=

Bi¯¯¯¯

定点乘法

原码并行乘法

不带符号的阵列乘法器 (即 两个无符号数据的并行乘法电路)

=

∑m−1i=0∑n−1j=0(aibj)2i+j

=

∑m+n−1k=0pk2k

带符号的阵列乘法器 (即 间接补码乘法电路)

直接补码并行乘法

定点运算器

逻辑运算

多功能算术/逻辑运算单元(ALU)

内部总线

定点运算器的基本结构

浮点运算

浮点加法、减法

y =

2Ey

·

My

浮点乘法、除法

y =

2Ey

·

My

1502

1502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?