转载:http://blog.sina.com.cn/s/blog_624c09450100hojw.html

转载:http://blog.csdn.net/ruixj/article/details/4084701

SPI

接口的全称是

"Serial Peripheral Interface",

意为串行外围接口

,

是

Motorola

首先在其

MC68HCXX

系列处理器上定义的。

SPI

接口主要应用在

EEPROM,FLASH,

实时时钟

,AD

转换器

,

还有数字信号处理器和数字信号解码器之间。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度最高可达到5Mbps。

(1)MOSI– 主器件数据输出,从器件数据输入

(2)MISO– 主器件数据输入,从器件数据输出

(3)SCLK– 时钟信号,由主器件产生

(4)/SS

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度最高可达到5Mbps。

(1)MOSI– 主器件数据输出,从器件数据输入

(2)MISO– 主器件数据输入,从器件数据输出

(3)SCLK– 时钟信号,由主器件产生

(4)/SS

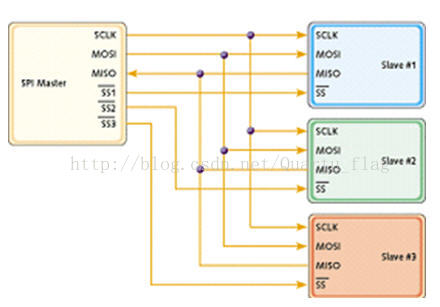

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

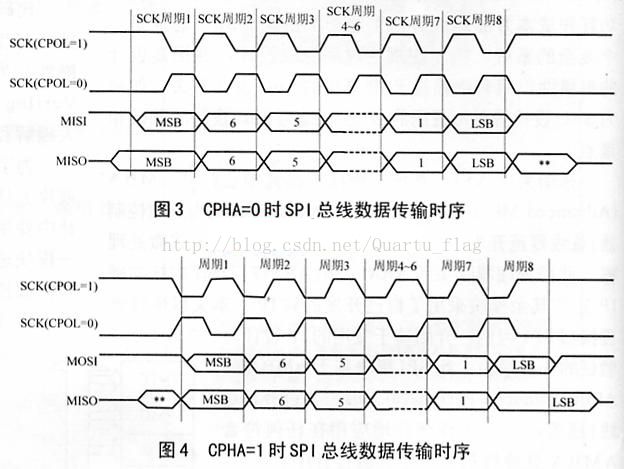

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。 如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。 时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设备时钟相位和极性应该一致。SPI主模块和与之通信的外设备时钟相位和极性应该一致。个人理解这句话有2层意思: 其一,主设备SPI时钟和极性的配置应该由外设来决定;其二,二者的配置应该保持一致,即主设备的SDO同从设备的SDO配置一致,主设备的SDI同从设备的SDI配置一致。因为主从设备是在SCLK的控制下,同时发送和接收数据,并通过2个双向移位寄存器来交换数据。SPI接口时序如图3、图4所示。

最后

,SPI

接口的一个缺点:没有指定的流控制

,

没有应答机制确认是否接收到数据。

4种模式为 4种时钟设置,一个设置是时钟空闲时在高或者低的状态,另一个设置数据是在时钟的上升沿或下降沿锁存;

4种模式为 4种时钟设置,一个设置是时钟空闲时在高或者低的状态,另一个设置数据是在时钟的上升沿或下降沿锁存;

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?