实验要求..在下面这个链接里:

完整的实验报告:

1. 电子锁功能要求

l 2种工作模式,可以设置和校验密码

l 密码长度为8位,内容为数字1-9,分别对应9个微动开关

l 8个数码管实时显示当前输入的密码值

l 密码校验正确则点阵显示为绿色的”OK”,同时播放一种音乐

l 密码校验错误则点阵显示为红色的”NO”,同时播放另一种音乐

2. 需求分析与系统设计

l 密码有8位,且每位的内容为数字1-9

l 需要一个4位的寄存器来存储一个密码位的值,总共需要8个寄存器来存储一个密码.

l 再有一个比较模块来比较2个存储模块中存储的密码是否相同.

l 点阵与蜂鸣器根据比较结果来做出相应的输出

l 数码管实时显示当前存储器中的各位密码值

3. 各模块具体设计

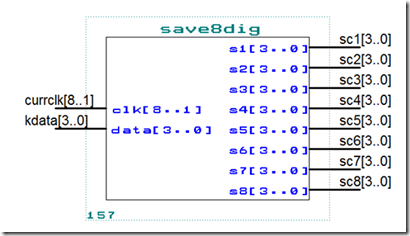

1) 密码存储模块

Data[3..0]为一位密码的输入端口,由clk[8..1]中的有效位来控制将该位密码存入某个寄存器中,s1[3..0]~s8[3..0]为各位寄存器的状态输出端口,可用来获得各位密码的值.

在本系统中总共需要2个这样的寄存模块,一个用来存放设置的原密码,另一个用来存放用户验证时输入的密码.然后只要比较这两个寄存模块的值就可确定密码是否输入正确了.

2) 获得键盘值模块

根据9个针脚上连接的按键的响应情况来转码输出对应的密码值

3) 主要逻辑控制模块

• 根据拨码开关状态来控制设置或者校验密码这2种工作方式

• 将按键输入的各个密码值送到各自的存储器中存储

• 发出密码输入完毕开始校验的状态

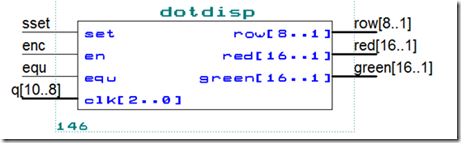

4) 点阵显示模块

根据main的指令来控制点阵显示相应的内容.

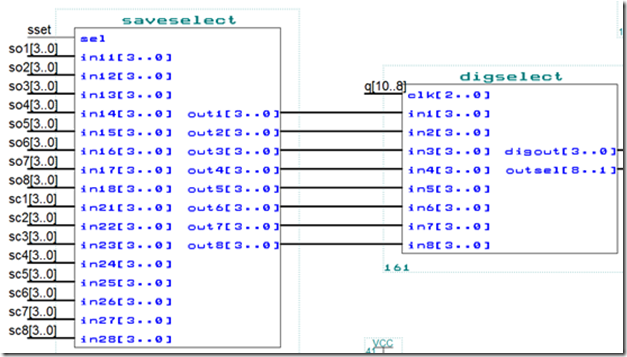

5) 数码管显示模块

根据main指令选择不同的存储器,实时显示密码值到数码管上.

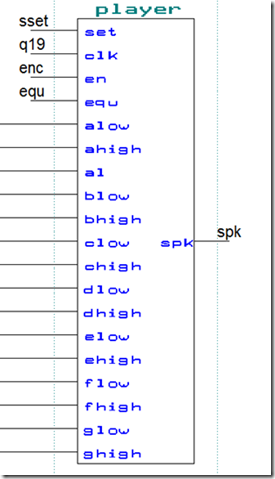

6) 音频播放模块

将验证的结果的正确与否使用不同的曲子来表示

若结果正确,播放一段升音阶的旋律

若不正确,播放一段降音阶的旋律

7) 其他模块

有了上述这6个主要的功能模块后,还需要配合一些基本的小模块来完成实验.比如需要一个按键消抖的模块来准确的获得按键值.需要一个七段数码管模块来输出显示信号.需要一个22位的计数器来进行分频等.

4. 系统顶层图

5. 实验中碰到的问题及解决方案

l 点阵与led的显示出现非预设的结果.原因是clk频率太高,由于人的视觉残留等原因造成错觉.降低了显示的刷新频率后解决

l 按键的消抖做的不好,还是有误按.逐步调试,慢慢降低了键盘检测的频率(等于是使键盘响应变迟钝)后解决.目前高速击键都可以被正常识别,没有错误现象了

6. 实验心得

这个实验应该是综合率比较高的了.把2种按键输入,点阵,数码管和蜂鸣器这3种输出以及存储器的读写功能都实现了.通过这个实验可以充分的学习并利用到所有的功能,感受到实验的乐趣.

7. 程序源码附录

-EOF-

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?