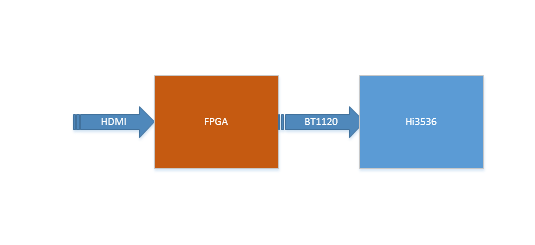

我们先看下下面的架构图,HDMI 4k@30hz,想进3536没有找到相应的芯片转为 bt1120.FPGA就充当了转化作用。 Xilinx最近出了一个Hdmi_ipcore.就想把他用起来。所以就有下面的架构图。我要做的工作其中之一就是要把 标准的视频VESA信号转为 BT1120出去.

现在我要做的就是把TTL(YCbCr 4:2:2)转为 BT1120给海思3531。我把思路说一下:

如上图所示,当收到第一个nvsync下降沿,然后 de 上升沿的时候,开始计数。这样就可以在相应的位置上填上相应的标志位和有效像素。当然需要用到状态机。

最后我附上,之前写的testbench关于1920 x 1080 @ 60hz.VESA标准。

`timescale 1 ps/1ps

module tb;

parameter H_D0 = 88;

parameter H_D1 = 44;

parameter H_D2 = 148;

parameter H_D = 1920;

parameter V_D0= 4;

parameter V_D1 = 5;

parameter V_D2 = 36;

parameter V_D = 1080;

reg clock_source;

reg clk_rd;

reg

本文介绍了使用FPGA将HDMI 4k@30hz信号转换为BT1120的过程。通过Xilinx的Hdmi_ipcore,作者设计了一个架构,其中关键任务是将TTL YCbCr 4:2:2信号转换为BT1120,以适配海思3531。转换过程中利用状态机在接收到特定同步信号时填充标志位和有效像素。

本文介绍了使用FPGA将HDMI 4k@30hz信号转换为BT1120的过程。通过Xilinx的Hdmi_ipcore,作者设计了一个架构,其中关键任务是将TTL YCbCr 4:2:2信号转换为BT1120,以适配海思3531。转换过程中利用状态机在接收到特定同步信号时填充标志位和有效像素。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

781

781

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?