指令的执行步骤(又称指令周期),是在控制单元的控制下,精确地,一步一步地完成。

哈工大的课是分成了3个步骤,不同的教材细节划分不一样。

①取指令 PC寄存器或称IP指向要取的指令,并保存在IR寄存器中

② 分析指令

③ 执行指令

而系统概论这本书分成了6个节拍:

① 取指令 PC寄存器或称IP指向要取的指令,并保存在IR寄存器中

② 译码 译码器译码

③ 地址计算

④ 取操作数

⑤ 执行

⑥ 存放结果

PC指向的是下一条指令,不要机械的认为它就是PC+1,如果指令本身只占一个字节,当然是PC+1,

可是如果一条指令占用32个字节,那每次就是PC+4。

另外在什么时候进行pc+1的工作呢?

似乎任意一个步骤的间歇都可以,不过现代的流水线型处理器要求尽可能早更新PC,所以一般在取指令完成后,就对PC进行更新。

从内存中取出指令后,在分析指令之前,需要把该指令先保存到IR寄存器。

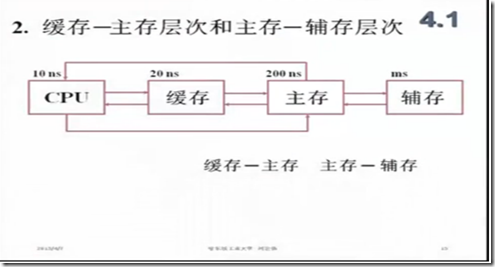

存储器分成两个大的层次,即缓存---主存层次和主存---辅存层次。

前一种层次是依靠硬件完成,后一种层次是软硬件相结合的方式完成。

普通程序员不用考虑数据在不同层次间的转移调度。

为什么会出现这样的情况呢?

人们希望存储器速度足够快,容量足够大,价格又要足够低。

想象很美好,实际上做不到,只能依靠设计的权衡取舍。

为了解决cpu与内存之间的速度差异,人们想出了cache,造就了缓存---主存层次。

为了解决主存的容量不足,人们想出了辅存,造就了主存---辅存层次。

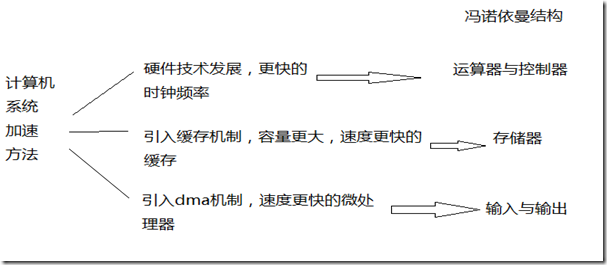

都是对经典冯诺依曼结构的改进。

主存---辅存层次引出了虚拟存储器的概念,虚地址,逻辑地址。

缓存---主存层次引出了主存储器的实地址,物理地址。

——————————————————————

现代计算机把存储器层次结构进一步扩展,更精确的说是缓存概念扩展,在主存储器,缓存,辅助存储器之间又添加更多缓存。

这样改进的优点在于:

如果cpu要和主存进行数据交换,那么实际上它主要和寄存器,高速缓存之间进行数据交换,只有当cache中没有需要的数据时,才会去访问主存。

同理,如果主存要和辅助存储器进行数据交换,那么实际上主存主要是与辅存的缓存进行交换,只有当cache中没有需要的数据时,才会去访问辅助存储器。

每一层速度更慢的存储器,在某一段时刻,都被速度更快的缓存所“替代”,所以整体加速了计算机系统。

另外一种改进在于数据交换本身,在早期的时候,数据的交换搬运是由cpu来完成的,现代通过引入dma技术,数据搬运由dma微处理器完成,减轻了cpu的工作量。

1231

1231

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?