CY7C68013A Slave FIFO 相关的寄存器说明

Slave FIFO 固件需要设置的相关寄存器

| IFCONFIG | EPxFIFOPFH/L |

| PINFLAGSAB | PORTACFG |

| PINFLAGSCD | INPKTEND |

| FIFORESET | FIFOPINPOLAR |

| EPxCFG | EPxFIFOBCH:L |

| EPxFIFOCFG | EPxAUTOINLENH:L |

| EPxBCH:L | |

| REVCTL (bits 0 and 1 must be initialized to 1 for operation as described in this chapter) |

一. CPUCS(E600)CPU控制和状态寄存器

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | PORTCSTB | CLKSPD1 | CLKSPD0 | CLKINV | CLKOE | 8051RES |

| r/w | r | r | rw | rw | rw | rw | rw | r |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

PORTCSTB:128脚或100脚的RD,WR输出使能;

CLKSPD[1:0]:8051CPU频率选择,

| CLKSPD[1:0] | 00 | 01 | 10 | 11 |

| CPU频率 | 12MHz | 24MHz | 48MHz | Reserved |

CLKINV:CLKOUT反相;

CLKOE: CLKOUT输出使能;

8051RES: 位为1来复位EZ-USB的8051 CPU。

二. REVCTL(E60B) 芯片修订版本控制

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | 0 | 0 | 0 | 0 | DYN_OUT | ENH_PKT |

| r/w | r | r | r | r | r | r | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Cypress推荐设置DYN_OUT=1和ENH_PKT=1,

DYN_OUT=1和ENH_PKT=1时,the FIFO cannot accept the OUT data;

DYN_OUT=0和ENH_PKT=0时,the FIFO cannot be reset well sometimes。

1. DYN_OUT:Disable Auto-Arming EPx at the 0-1 transition of AUTOOUT

DYN_OUT=0,the core automatically arms the endpoints when AUTOOUT is switched from 0 to 1

DYN_OUT=1,the core disables auto-arming of the endpoints when AUTOOUT transitions from 0 to 1. This feature allows CPU intervention when switching between AUTO and Manual mode without having to reset the endpoint.

2. ENH_PKT: CPU处理数据包的能力

ENH_PKT=0时,CPU可对OUT数据包和IN数据包的操作

| ENH_PKT=0 | Skip | Commit | Edit/Source |

| Out packets | 1 | 1 | 0 |

| In packets | 0 | 1 | 1 |

ENH_PKT=1时,CPU可对OUT数据包和IN数据包的操作

| ENH_PKT=1 | Skip | Commit | Edit/Source |

| Out packets | 1 | 1 | 1 |

| In packets | 1 | 1 | 1 |

ENH_PKT=1时, EPxBCH和 EPxBCL=0x80不能用于清空OUT端点缓冲区,只能用OUTPKTEND寄存器清空 OUT端点缓冲区。

三. IFCONFIG(E601):接口配置寄存器

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | IFCLKSCR | 30/40MHz | IFCLKOE | IFCLKPOL | ASYNC | GSTATE | IFCFG1 | IFCFG0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

IFCLKSRC:FIFO时钟内部/外部时钟源选择,0--外部时钟源,1--内部时钟源。

30/48MHZ:当IFCLKSRC=1时,选择30MHz/48MHz内部时钟频率,0--IFCLK 30MHz,1--IFCLK 48MHz。

IFCLKOE:当IFCLKSRC=1时,IFCLK时钟输出使能,0--关闭,1--打开。

IFCLKPOL:IFCLK输出反转使能,0--正常,1--反转。

ASYNC:Slave FIFO同步/异步工作方式选择,0同步,1异步。

GSTATE:选择是否将GSTATE[2:0]在PORTE[2:0]输出,0关闭,1使能。

IFCFG1:0:FX2 I/O端口模式选择,也既是上面所说的FX2与外部逻辑传输方式的选择。

| IFCFG1 | IFCFG0 | Configuration |

| 0 | 0 | I/O Port |

| 0 | 1 | Reserved |

| 1 | 0 | GPIF |

| 1 | 1 | Slave FIFO |

四. EPxCFG(E612:E615):端点EP2,EP4,EP6,EP8配置

1.EP2CFG(E612),端点EP2配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | VALID | DIR | TYPE1 | TYPE0 | SIZE | 0 | BUF1 | BUF0 |

| r/w | rw | rw | rw | rw | rw | r | rw | rw |

| default | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

2.EP4CFG(E613),端点EP4配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | VALID | DIR | TYPE1 | TYPE0 | 0 | 0 | 0 | 0 |

| r/w | rw | rw | rw | rw | r | r | r | r |

| default | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

3.EP6CFG(E614),端点EP6配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | VALID | DIR | TYPE1 | TYPE0 | SIZE | 0 | BUF1 | BUF0 |

| r/w | rw | rw | rw | rw | rw | r | rw | rw |

| default | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 |

4.EP8CFG(E615),端点EP8配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | VALID | DIR | TYPE1 | TYPE0 | 0 | 0 | 0 | 0 |

| r/w | rw | rw | rw | rw | r | r | r | r |

| default | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

VALID:0端点无效,1端点有效;

DIR:端点方向,0=OUT方向,1=IN方向,默认端点2,4为IN,端点6,8为OUT

TYPE1,TYPE0:端点类型

| TYPE1 | TYPE0 | Endpoint type |

| 0 | 0 | Invalid |

| 0 | 1 | ISOCHRONOUS |

| 1 | 0 | BULK(default) |

| 1 | 1 | INTERRUPT |

SIZE:缓冲区大小(仅端点2和端点),0=512字节,1=1024字节

BUF1,BUF0:端点缓冲区个数(仅端点2和端点6)

| BUF1 | BUF0 | Buffering |

| 0 | 0 | Quad |

| 0 | 1 | Invalid |

| 1 | 0 | Double |

| 1 | 1 | Triple |

五.OUTPKTEND(E649):强制OUT数据包结束(当ENH_PKT(REVCTL.0)=1时该寄存器有效)

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | skip | 0 | 0 | 0 | EP3 | EP2 | EP1 | EP0 |

| r/w | w | w | w | w | w | w | w | w |

| default | x | x | x | x | x | x | x | x |

skip: skip=1表示将跳过一个OUT数据包(当ENH_PKT(REVCTL.0)=1时);

skip=0 automatically ‘dispatches’ an OUT buffer。

EP[3:0]表示端点序号,EP[3:0]=8、6、4、2对应端点EP8,EP6,EP4,EP2。

取代EPxBCL.7(skip)=1(PKTEND)引脚功能,软件强行结束OUT端点(EP8,EP6,EP4,EP2)数据传输,。

六. INPKTEND(E648):强制IN数据包结束,然后 “arming” the IN transfer。

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | skip | 0 | 0 | 0 | EP3 | EP2 | EP1 | EP0 |

| r/w | w | w | w | w | w | w | w | w |

| default | x | x | x | x | x | x | x | x |

skip: skip=1 表示将跳过一个IN数据包(当ENH_PKT(REVCTL.0)=1时);

skip=0 automatically ‘dispatches’ an IN buffer。

替代EPxBCL.7=1(PKTEND)引脚功能(当ENH_PKT(REVCTL.0)=1时,EPxBCL寄存器无效),软件强行结束IN端点(EP8,EP6,EP4,EP2)数据传输,

EP[3:0]表示端点序号,EP[3:0]=8、6、4、2对应端点EP8,EP6,EP4,EP2。

By writing the desired endpoint number (2, 4, 6 or 8), FX2 logic automatically ‘dispatches’ an

IN buffer, for example, it commits the packet to the USB logic, and writes the accumulated

byte count to the endpoint’s byte count register, thus “arming” the IN transfer

七. EPxFIFOCFG(E618:E61B):端点FIFO配置寄存器

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | INFM1 | OEP1 | AUTOOUT | AUTOIN | ZEROLENIN | 0 | WORDWIDE |

| r/w | r | rw | rw | rw | rw | rw | r | rw |

| default | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

INFM1:FIFO状态标志是否提前一个字节有效选择,IN端点缓冲区满-1,1使能,0非使能。

OEP1:FIFO状态标志是否提前一个字节有效选择,OUT端点缓冲区空+1,1使能,0非使能。

AUTOOUT: Slave FIFO方式下的数据传输过程, FX2固件的一般不参与,也可以参与。

AUTOOUT=1, FX2固件只需要完成初始化工作,真正的数据传输是不需要FX2固件的参与,具体的说,当FX2从主机收到一包数据时,外部逻辑即可看到FIFO端点缓冲区状态的改变,然后从中取数;

AUTOOUT=0,则数据传输过程就需要FX2参与了,此时当FX2从主机收到一包数据时,FIFO端点缓冲区状态的改变并不会立刻在端口显现,而是固件先看到FIFO端点状态的改变,此时,FX2固件可以传输、丢弃或修改包数据。

a.向OUTPKTEND中的SKIP位写0,使FIFO端点状态的改变在端口显现,从而使外部逻辑可以从FIFO端点中读取数据;

b.向OUTPKTEND中的SKIP位写1,丢掉这包数据,这样就相当于主机从来就没有发送这一包数据,外部逻辑当然也不能从FIFO端点中读到这一包数据了;

c.从新编辑这一包数据,设置完全重写整个包的数据,再写EPxBC寄存器的SKIP=0,把数据传给外部逻辑。

在FX2复位之后,如果其OUT端点缓冲区内有一包数据未处理,这包数据并不会自动传给外部逻辑。所以,为保证OUT端点缓冲区内没有未处理数据,在reset FX2后,要清空一下OUT端点缓冲区,具体做法就是向SKIP位写1(OUT端点缓冲区有几个缓冲区就写几次)。

AUTOIN:AUTO IN和AUTOOUT有一点不同,在AUTOOUT里,包的大小只能是512或1024,而在Auto IN里,包的大小可以任意设定,甚至可以是0字节,这可以通过EPxAUTOINLENTH/L设置。

类似于AUTOOUT,当设置AUTOIN= 0时,FX2固件可以传输、丢弃或修改外部逻辑传过来的数据,这通过向INPTKEND寄存器的SKIP写不同的值实现。

ZEROLENIN:是否允许传输0字节,1使能,0非使能。

WORDWIDE:8位、16位数据传输。WORDWIDE=0--8位数据传输,Port B将是FD[7:0];WORDWIDE=1--16位数据传输,Port B将是FD[7:0],Port D将是FD[15:8]。

八. FIFOPINPOLAR(E609):控制引脚极性设置寄存器

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | PTKEND | SLOE | SLRD | SLWR | EF | FF |

| r/w | r | r | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Slave FIFO引脚极性设置:0低有效,1高有效。

提示:PF极性没有提供寄存器设置,为高有效。

九. FIFORESET(E604): 端点复位寄存器(复位后要re-arming OUT EP、IN EP)

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | NAKALL | 0 | 0 | 0 | EP3 | EP2 | EP1 | EP0 |

| r/w | w | w | w | w | w | w | w | w |

| default | x | x | x | x | x | x | x | x |

将FIFO复位到默认状态(即FIFO flags、byte counts)。具体过程是,写0x80到此寄存器,NAK所有主机请求;写0x02,0x04,0x06,0x08分别复位各个端点;写0x00,结束复位过程。

一般,在每一次开始进行slave FIFO或GPIF传输之前,先复位端点,再清空端点,然后即可进行数据传输。。

NAKALL-0关闭NAK功能,1用NAK响应主控器请求,例如在复位端点FIFO时,为了保证复位正常,防止主控器请求的干扰,先写入0x80,然后复位端点,最后写入0x00,使能请求响应。

EP[3:0]表示端点序号,EP[3:0]=8、6、4、2对应端点EP8,EP6,EP4,EP2。

You also need to ensure after performing a FIFORESET that you are re-arming the OUT endpoints. For OUT endpoints, you need to arm the buffers to let the SIE take control of them, and accept data from the host.

十. PINFLAGSAB/CD(E602:E603):FLAGx(FLAGA、FLAGB、FLAGC、FLAGD)引脚配置寄存器

PINFLAGSAB寄存器,Slave FIFO FLAGA和FLAGB引脚配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | FLAGB3 | FLAGB2 | FLAGB1 | FLAGB0 | FLAGA3 | FLAGA2 | FLAGA1 | FLAGA0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

PINFLAGSCD寄存器,Slave FIFO FLAGC和FLAGD引脚配置

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | FLAGD3 | FLAGD2 | FLAGD1 | FLAGD0 | FLAGC3 | FLAGC2 | FLAGC1 | FLAGC0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

FLAGA,FLAGB,FLAGC,FLAGD反映FIFO状态选择。每个脚有索引/固定两种模式:如设为编址模式,则它们都反映FIFOADR[1:0]脚当前所指端点的状态,其中,FLAGA反映“可编程极限”,FLAGB反映“满”标志,FLAGC反映“空”标志,FLAGD不存在;如设为固定模式,它们均可任意设置成反映任意端点的任意标志,而不受限于FIFOADR[1:0]脚当前所指端点的状态。

Slave fifo模式中,用引脚FLAGA~FLAGD来定义用端点FIFO的状态,并可灵活编程来实现FLAGx设置。

| FLAGx3 | FLAGx2 | FLAGx1 | FLAGx0 | Pin Function |

| 0 | 0 | 0 | 0 | FLAGA=PF, FLAGB=FF, FLAGC=EF, FLAGD=EP2PF (Actual FIFO is selected by FIFOADR[1:0] pins) |

| 0 | 0 | 0 | 1 | Reserved |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | EP2 PF |

| 0 | 1 | 0 | 1 | EP4 PF |

| 0 | 1 | 1 | 0 | EP6 PF |

| 0 | 1 | 1 | 1 | EP8 PF |

| 1 | 0 | 0 | 0 | EP2 EF |

| 1 | 0 | 0 | 1 | EP4 EF |

| 1 | 0 | 1 | 0 | EP6 EF |

| 1 | 0 | 1 | 1 | EP8 EF |

| 1 | 1 | 0 | 0 | EP2 FF |

| 1 | 1 | 0 | 1 | EP4 FF |

| 1 | 1 | 1 | 0 | EP6 FF |

| 1 | 1 | 1 | 1 | EP8 FF |

说明:

- 1.PF表示FIFO编程状态,EF表示FIFO已空,FF表示FIFO已满;

- 2.0000为索引模式,其它为固定模式。

十一. PORTACFG:端口A引脚功能配置

端口A引脚功能由3个寄存器决定:PORTACFG、IFCONFIG和WAKEUPCS

| | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| PORTACFG | FLAGD | SLCS | 0 | 0 | 0 | 0 | INT1 | INT0 |

| IFCONFIG | IFCLKSRC | 3048MHZ | IFCLKOE | IFCLKPOL | ASYNC | GSTATE | IFCFG1 | IFCFG0 |

| WAKEUPCS | WU2 | WU | WU2POL | WUPOL | 0 | DPEN | WU2EN | WUEN |

| Port A Pin | 备用功能 | 条件 |

| PA.0 | INT0 | PORTACFG.0=1 |

| PA.1 | INT1 | PORTACFG.1=1 |

| PA.2 | SLOE | IFCFG1:0=11 |

| PA.3 | WU2 | WU2EN=1 |

| PA.4 | FIFOADR0 | IFCFG1:0=11 |

| PA.5 | FIFOADR1 | IFCFG1:0=11 |

| PA.6 | PKTEND | IFCFG1:0=11 |

| PA.7 | FLAGD | PORTACFG.7 = 1 |

| SLCS | PORTACFG.6 = 1 and IFCFG1:0 = 11 |

Note 1: When PA.3 is configured for alternate function WU2, it continues to function as a general-purpose input pin

as well. See Section 6.4.1, "WU2 Pin" for more information.

Note 2: Although PA.7’s alternate function FLAGD is selected via the PORTACFG register, the state of the FLAGD

output is undefined unless IFCFG1:0 = 11.

Note 3: FLAGD takes priority over SLCS if PORTACFG.6 and PORTACFG.7 are both set to 1.

十二.EPxAUTOINLENH/L(E620:E627):EP2,EP4,EP6,EP8 AUTOIN长度设置(仅IN端点有效)

设置AUTOIN时自动传输的包大小(注意,不能大于IN端点的缓冲区的大小)。

EPxAUTOINLENH包长度高字节

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | 0 | 0 | 0 | PL10 | PL9 | PL8 |

| r/w | r | r | r | r | r | rw | rw | rw |

| default | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

EPxAUTOINLENL包长度低字节

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | PL7 | PL6 | PL5 | PL4 | PL3 | PL2 | PL1 | PL0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

说明:PL10仅EP2和EP6有效

十三.EPxFIFOPFH/L(E630:E637):EPx Slave FIFO可编程标志H/L

13.1.1 EP2FIFOPFH [HIGH SPEED (480 Mbit/Sec) Mode and FULL-SPEED (12 Mbit/Sec) Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | IN: PKTS[2] OUT:PFC12 | IN: PKTS[1] OUT:PFC11 | IN: PKTS[0] OUT:PFC10 | 0 | PFC9 | PFC8 |

| r/w | rw | rw | rw | rw | rw | r | rw | rw |

| default | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.1.2 EP2FIFOPFH [FULL SPEED (12 Mbit/Sec) Non-Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | OUT:PFC12 | OUT:PFC11 | OUT:PFC10 | 0 | PFC9 | IN:PKTS[2]] OUT:PFC8 |

| r/w | rw | rw | rw | rw | rw | r | rw | rw |

| default | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.2.1 EP4FIFOPFH [HIGH SPEED (480 Mbit/Sec) Mode and FULL-SPEED (12 Mbit/Sec) Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | 0 | IN: PKTS[1] OUT:PFC10 | IN: PKTS[0] OUT:PFC9 | 0 | 0 | PFC8 |

| r/w | rw | rw | r | rw | rw | r | r | rw |

| default | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.2.2 EP4FIFOPFH [FULL SPEED (12 Mbit/Sec) Non-Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | 0 | OUT:PFC10 | OUT:PFC9 | 0 | 0 | PFC8 |

| r/w | rw | rw | r | rw | rw | r | r | rw |

| default | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.3.1 EP6FIFOPFH [HIGH SPEED (480 Mbit/Sec) Mode and FULL-SPEED (12 Mbit/Sec) Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | IN:PKTS[2] OUT:PFC12 | IN: PKTS[1] OUT:PFC11 | IN: PKTS[0] OUT:PFC10 | 0 | PFC9 | PFC8 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.3.2 EP6FIFOPFH [FULL SPEED (12 Mbit/Sec) Non-Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | OUT:PFC12 | OUT:PFC11 | OUT:PFC10 | 0 | PFC9 | IN:PKTS[2] OUT:PFC8 |

| r/w | rw | rw | rw | rw | rw | r | rw | rw |

| default | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.4.1 EP8FIFOPFH [HIGH SPEED (480 Mbit/Sec) Mode and FULL-SPEED (12 Mbit/Sec) Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | 0 | IN: PKTS[1] OUT:PFC10 | IN: PKTS[0] OUT:PFC9 | 0 | 0 | PFC8 |

| r/w | rw | rw | r | rw | rw | r | r | rw |

| default | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.4.2 EP8FIFOPFH [FULL SPEED (12 Mbit/Sec) Non-Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | DECIS | PKTSTAT | 0 | OUT:PFC10 | OUT:PFC9 | 0 | 0 | PFC8 |

| r/w | rw | rw | r | rw | rw | r | r | rw |

| default | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

13.5 EPxFIFOPFL [HIGH SPEED (480 Mbit/Sec) Mode and FULL-SPEED (12 Mbit/Sec) Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | PFC7 | PFC6 | PFC5 | PFC4 | PFC3 | PFC2 | PFC1 | PFC0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

13.6 EPxFIFOPFL [FULL SPEED (12 Mbit/Sec) Non-Iso Mode]

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | IN:PKTS[1] OUT:PFC7 | IN:PKTS[0] OUT:PFC6 | PFC5 | PFC4 | PFC3 | PFC2 | PFC1 | PFC0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

DECIS-0小于等于门限值PF有效,1大于等于门限值PF有效

PKSTAT-

- 1.OUT端点FIFO:门限值为PFC12:0设置,当FIFO长度小于等于门限值(DECIS=0),或者FIFO长度大于等于门限值(DECIS=1),则PF有效。

- 2.IN端点FIFO,且PKTSTAT=1:门限值为PFC9:0

- 3.IN端点FIFO,且PKTSTAT=0:门限值由两部分组成:PKTS2:0(数据包)再加上PFC9:0(当前数据长度)。

对于OUT包,极限存储在PFC[12:0]中,在整个FIFO缓冲区中的数据数目少于等于(DECIS=0)或大于等于(DECIS=1)这个极限时,PF将有效。

对于IN包,当PKTSTAT=1时,极限存储在两部分:PKTS[2:0]存储极限包数(已经交给SIE但未传给主机的包数),PFC[9:0]存储极限字节数(正在编辑的包里的字节数)。在整个FIFO缓冲区中的数据数目少于等于(DECIS=0)或大于等于(DECIS=1)这个极限时,PF将有效。

十四. EPxBCL Low byte count for Endpoints 2、4、6、8

EP2BCL,EP4BCL,EP6BCL,EP8BCL

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | BC7/SKIP | BC6 | BC5 | BC4 | BC3 | BC2 | BC1 | BC0 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | x | x | x | x | x | x | x | x |

当REVCTL.0(ENH_PKT)=0时,EPxBCL.7复用为SKIP。

十五. EPxBCH High byte count for Endpoints 2、4、6、8

15.1 EP2BCH,EP6BCH

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | 0 | 0 | 0 | BC10 | BC9 | BC8 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | x | x | x |

15.2 EP4BCH,EP8BCH

| bit | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| name | 0 | 0 | 0 | 0 | 0 | 0 | BC9 | BC8 |

| r/w | rw | rw | rw | rw | rw | rw | rw | rw |

| default | 0 | 0 | 0 | 0 | 0 | 0 | x | x |

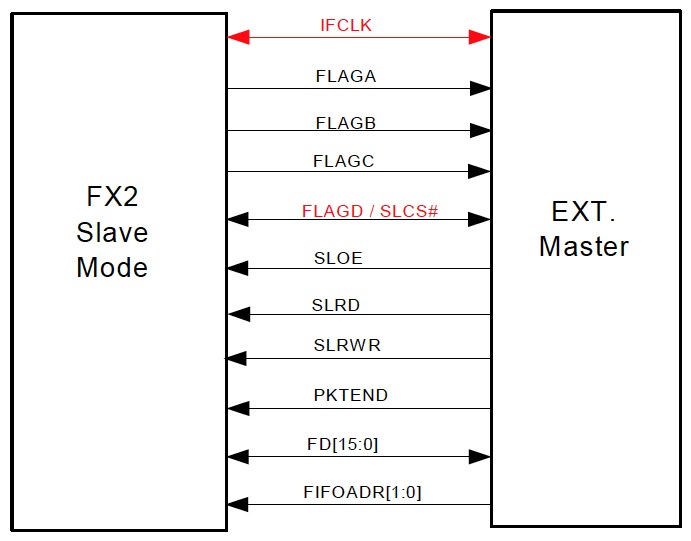

十六. FIFO 相关的引脚

16.1 控制引脚(SLOE、 SLRD、 SLWR、PKTEND、FIFOADR[1:0])

SLOE:FIFO输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据;

SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效—无效的跳变沿时递增;

SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效—无效的跳变沿时数据被写入,FIFO写指针递增;

PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;

FIFOADR[1:0]:选择四个FIFO端点的地址线,外部逻辑控制。

| FIFOADR1 pin | FIFOADR0 pin | Selected FIFO |

| 0 | 0 | EP2 |

| 0 | 1 | EP4 |

| 1 | 0 | EP6 |

| 1 | 1 | EP8 |

16.2 Slave FIFO 片选引脚 (SLCS)

SLCS:Slave FIFO的片选功能,为PA7的复用功能引脚,

可以通过设置PORTACFG.6 = 1 and IFCFG1:0 = 11来实现PA7引脚的SLCS功能。

当SLCS被外部拉高时,对Slave FIFO读写无效。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?