基于FPGA的cy7c68013a双向通信实验

本实验是基于FPGA的cy7c68013a的USB双向通信实验,以前折腾过一段时间cy7c68013a,没有入门时感觉好难,入门了就会感觉很简单。本教程主要内容:

1.cy7c68013a的固件编写,以及生成iic固件和下载固件。

2.cy7c68013a的slave模式,以及他的读写时序

3.cy7c68013a的FPGA的上板测试,包括发送和接受两部分

一、驱动

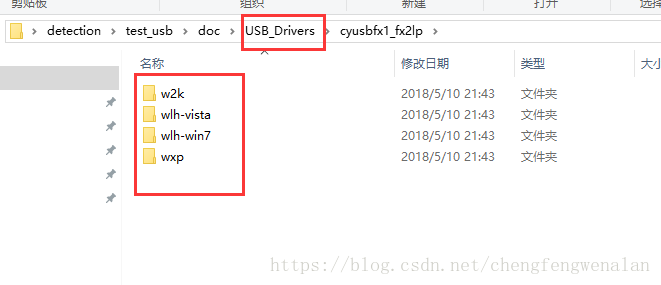

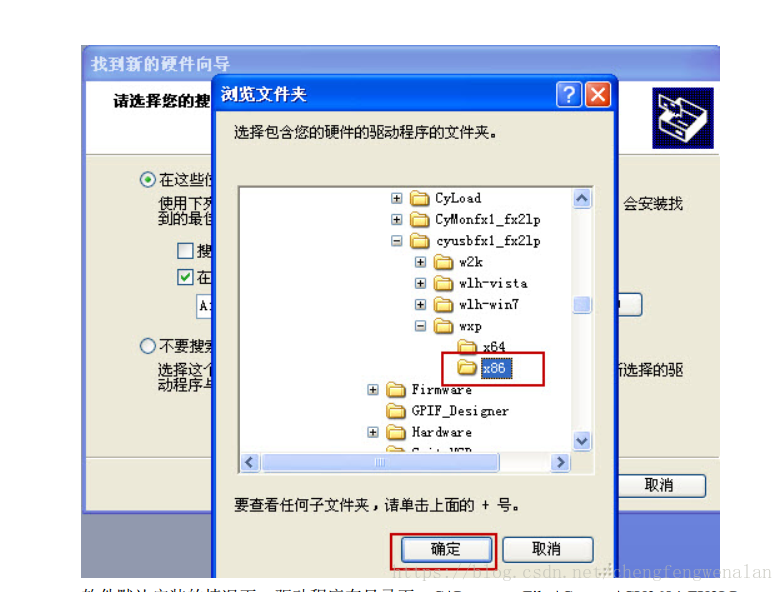

在进行试验前要先安装好cypress提供的usb驱动,插上usb后,电脑就会检测到未识别的设备,这时打开设备管理器,右键未识别的usb,然后手动选择驱动,驱动会在本教程最后的链接中给出

二、固件

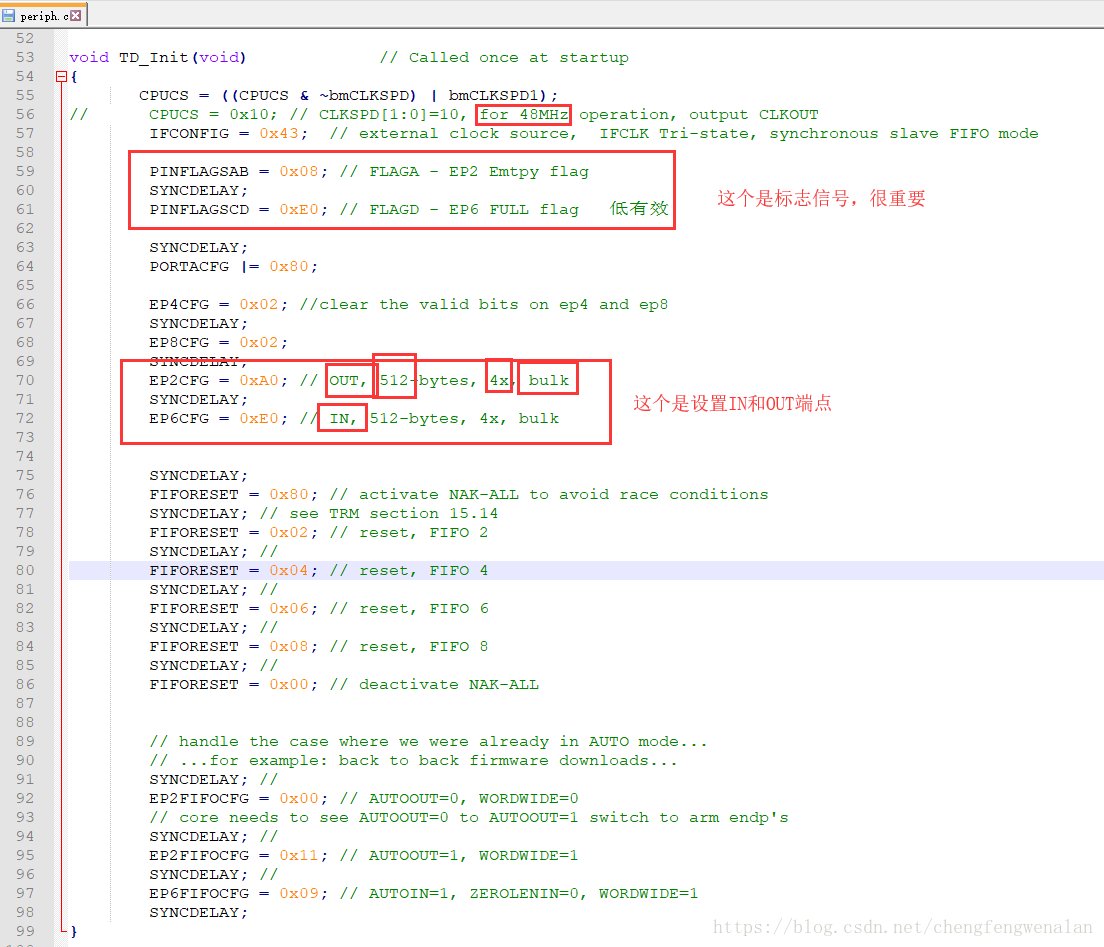

cy7c68013a想要正常工作,就得给他编写好相应的固件,然后再固化到其内部,当然PC也是需要安装相应的驱动的,固件的编写主要是确定IN和OUT端点,以及一些标志信号。

固件只需要改这些参数,这里我都写好了,大家就不需要再改了,很容易看出我设置的时钟是48MHz,,然后设置

EP2为OUT端点,512字节,4缓冲,bulk (注意OUT,IN都是相对PC来说的,OUT表示PC--->cy7c68013a,IN则相反)

EP6为IN端点,512字节,4缓冲,bulk

flag_a 为EP2的EF,也就是空标志信号,为低时表示空,也就是没有数据过来,为高则表示有数据来了

flag_d 为EP6的FF,也就是满标志信号,为低时表示写满了,这时再去写就是无效写了,为高则表示没有写满,可以继续写。

我写好的固件所在文件夹:固件源码什么的都在Firmware文件中

三、slave的写时序

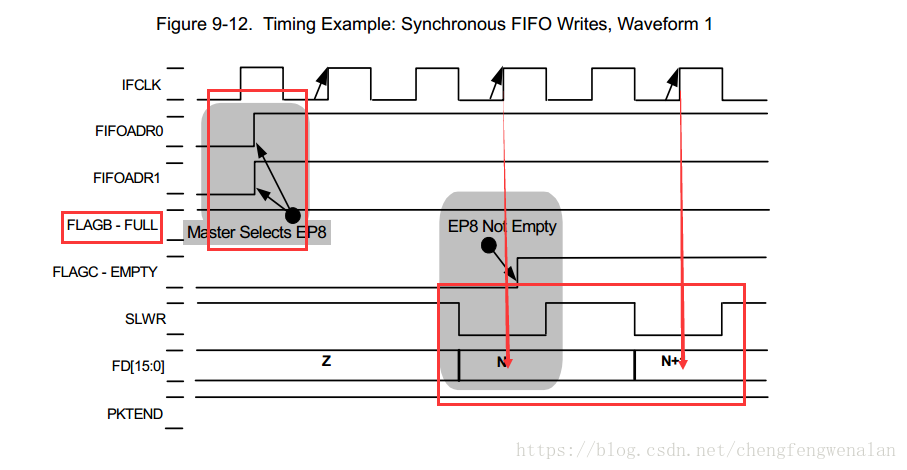

有图很容易看出,再写之前要先把FIFOADR确认好,这个决定了你写的对象是谁

然后在该fifo非满时(相应的FF标志位高),才可以进行写操作,这个时序很简单,就是拉低slwr信号就可以了,注意FD要与slwr对齐。

注意:写操作时,slwr与FD的数据都是FPGA来控制的,为了让cy7c68013a更好的采样,ifclk与clk反向之后再发送给cy7c68013a.

四、slave读操作

读时序跟写也是类似的,再读之前先确定FIFOADR,然后拉低sloe,这时FD总线就会出现第一个数据,然后检测到slrd为低时,FD就会显示下一个数据。

五、FPGA与cy7c68013a通信

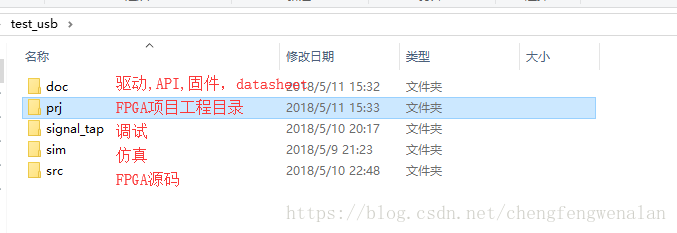

前面主要是一些准备工作,现在开始进入正式的通信过程,项目工程如下:

具体代码都已经有了详细注释了,自己去看看代码就知道了,这里就不详细说了

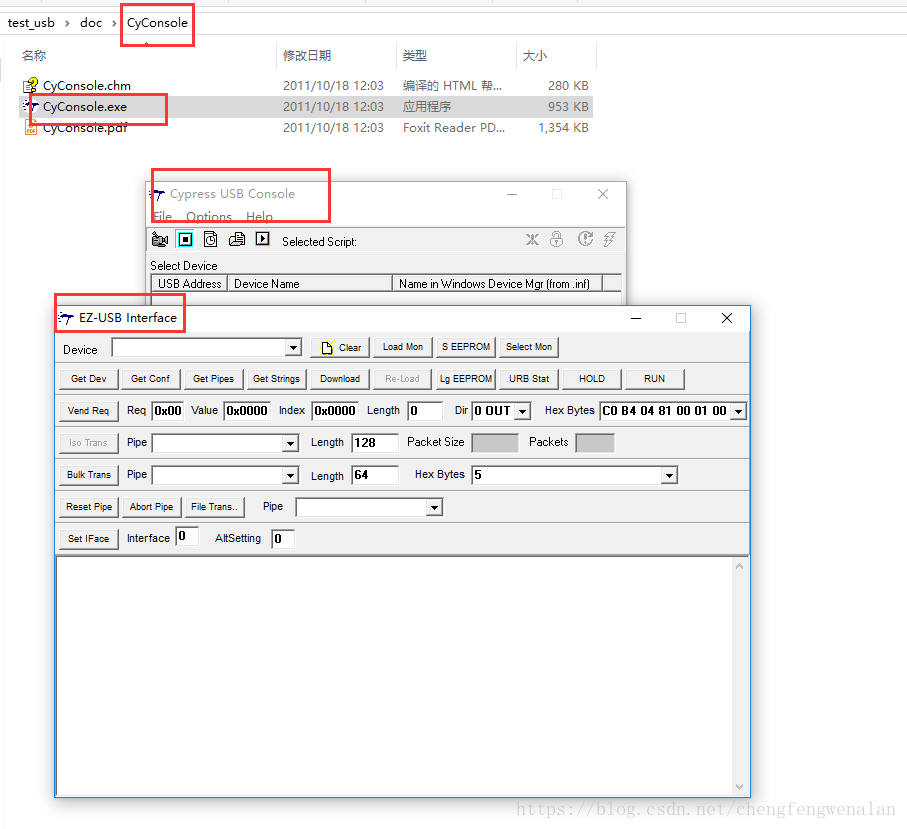

本教程所用的调试工具是官方的工具

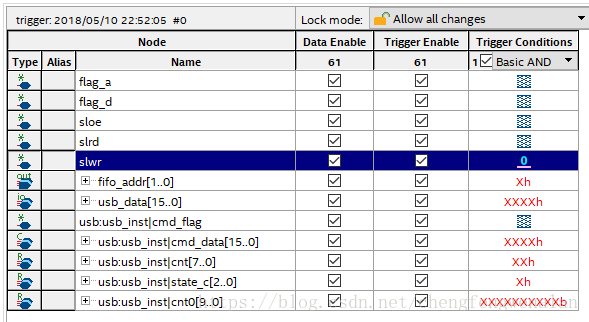

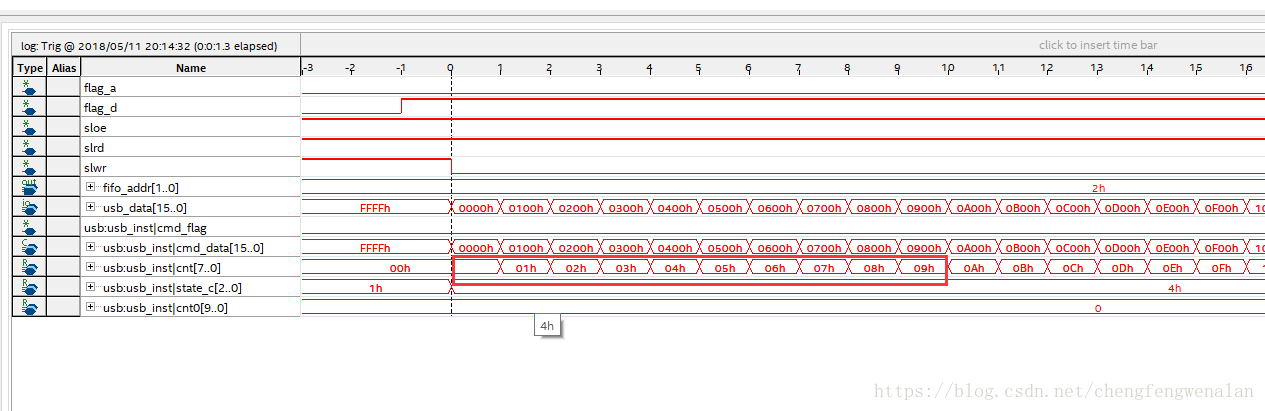

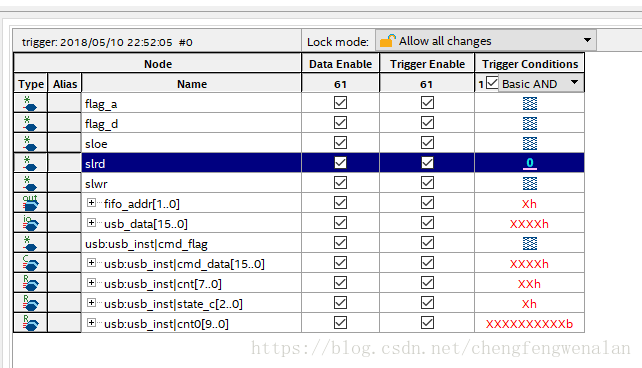

下面给出写的signal tap 的调试截图

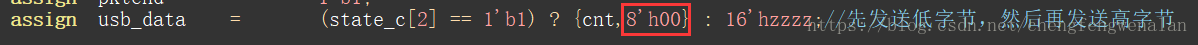

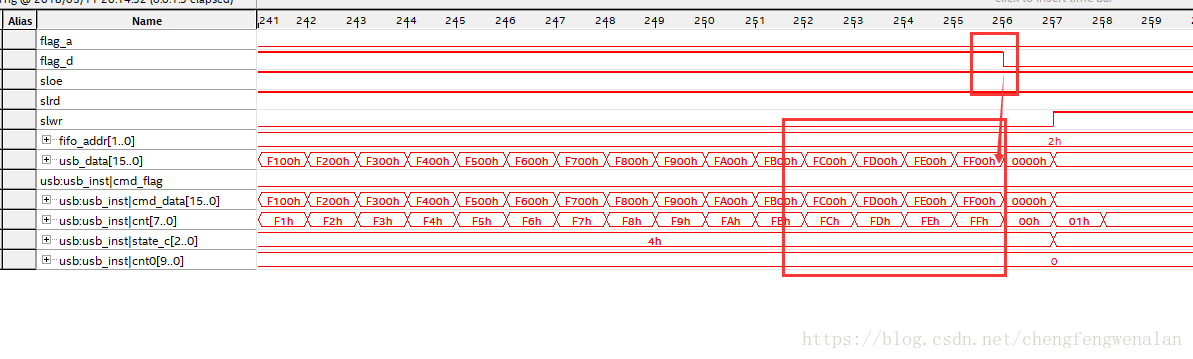

写是一次写512个字节数据,0-255,注意usb的fifo是一次发送16位的,也就是2个字节。先发送低字节,然后再发送高字节,这我直接把低字节给赋值为0了

前面局部放大图

后面局部放大图,注意只有在flag_d为高时,slwr为低才是有效写,否则就是无效写,因为当flag_d为低时,表示写满了,这时fifo就会弃之后的写数据了(因为已经写满了,也装不下了是吧,总不能硬塞是吧,哈哈~)

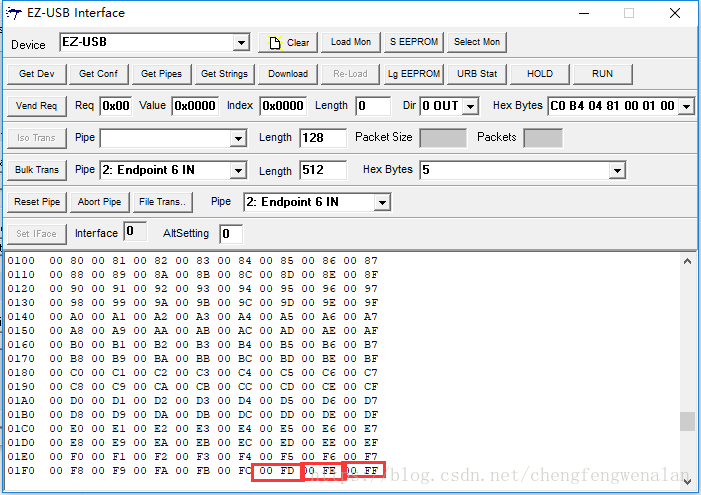

PC端接受到的数据要2个字节一起读,因为usb是16位发送的,可以看出接受到的数据的确是0000-00FF

注意:pc接受数据按我标的编码顺序执行

---------------------------------------------~~~我是分割线~~~---------------------------------------------------------------

下面轮到“读”出场了

pc发送数据按1-->2-->3的步骤,可以看出我们发送了12 34 56 78 这4个字节

注意这里我是设置了cmd_flag标志信号的,只有cmd_flag为高时的cmd_data的数据才是有效的,也就是pc发送过来的数据。

这里顺带插一嘴:

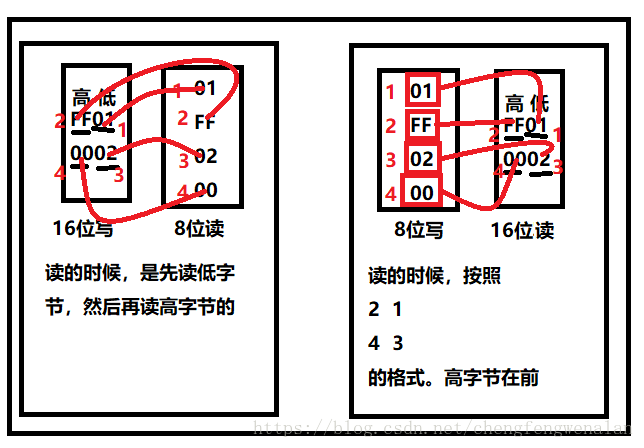

alter 的fifo ip 是可以读写位宽不一致的,具体看下面的图

由上图可以看出这个和usb是一样的格式,都是先发低字节,然后再发高字节。或者说先接受低字节,然后再接受高字节

至此本教程就全部介绍完了,讲的虽然有点简陋,但是基本的流程都已经讲到了,比起网上其他的教程还是要好不少的哈(自我陶醉一下),具体的看我的源代码。可以看出,使用cypress的usb还是比较简单的,因为usb协议什么的,他们都已经做好了,我们不需要考虑这些,要不然那一堆协议就看着头疼,具体的看我给的下载链接,我会把本教程所用到的工具,代码全部分享出来,也欢迎大家评论提问,不足之处还望指正~

六、福利

为了能及时回复大家,现在获取源码方式如下:

微信扫描下面的二维码关注【春哥笔记】公众号,回复“usb2”即可Get源码的获取方式:

8393

8393

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?