DMA 控制器允许 Blackfin 或者外设指定数据传送操作,然后返回正常操作中。 DMA 控制器传送数据的过程独立于处理器的活动 。

DMA 控制器传送数据的方式有下面几种:

l 存储器 <-> 存储器 ( MemDMA );

l 存储器 <-> 串行外设接口;

l 存储器 <-> 串行接口;

l 存储器 <-> UART 口;

l 存储器 <-> USB 口;

DMA 系统有包括 DMA 控制器( MemDMA )在内的 8 个 DMA 兼容外设,图 5.1 是 12 个通道和总线控制器,其中 DMA 传送可以使基于描述符 的,也可以是基于自动缓冲 的。

|

DAB, DCB, DEB Master |

默认仲裁优先级 |

|

PPI |

0-highest |

|

SPORT0 RCV DMA Controller |

1 |

|

SPORT1 RCV DMA Controller |

3 |

|

SPORT0 XMT DMA Controller |

2 |

|

SPORT1 XMT DMA Controller |

4 |

|

SPI DMA Controller |

5 |

|

UART RCV Controller |

6 |

|

UART XMT Controller |

7 |

|

Memory DMA0(dest) Controller |

8 |

|

Memory DMA0(source) Controller |

9 |

|

Memory DMA1(dest) Controller |

10 |

|

Memory DMA1(source) Controller |

11-lowest |

图 5.1 12 个通道和总线控制器

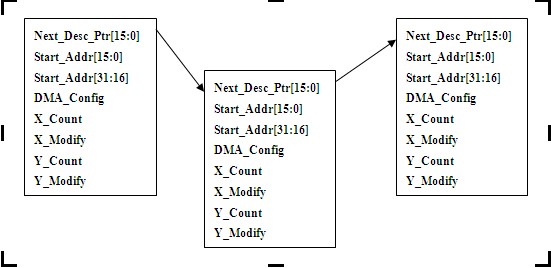

1 基于描述符的 DMA 传送

基于描述符的 DMA 传送是 Blackfin 控制 DMA 最普通的方法。使用该方法时, DMA 通道需要一组称为 DMA 描述符的参数,该参数存储在存储器中。每个描述符包含特定 DMA 传送序列所需要的所有信息,其组成结构如下:

(1) 要传送数据块的 32 位起始地址;

(2) 要传送的数据量

(3) 其他各种控制信息——如该 DMA 做什么,传送何时完成等配置信息;

(4) 指向下一个描述符的指针。

下面步骤是设置基于描述符的 DMA 的典型时序。在进行这些步骤之前,必须将描述符基地址( BASE+0 )的高 16 位设置到 DMA 描述符的基址指针寄存器( DMADBP )中。

(1) 将 DMA 配置字(其 15 位置为 1 ), DMA 传送计数, DMA 起始地址( 15:0 ), DMA 起始地址( 31:16 )以及下一个描述符指针( 15:0 ),写入描述符存储器地址 BASE+0~BASE+8 中。如果描述符是链表中的最后一个元素,或者是链表中的唯一元素,那么该描述符中的下一个描述符指针应该指向下一个存储单元,该存储单元的 15 位必全为零。基于上述要求,下一个描述符指针可以指向当前描述符的基地址 BASE+0 。在 DMA 传送序列完成之后, DMA 配置字的位 15 被清零。控制器返回给处理器。

(2) 将描述符基地址( BASE+0 )的低 16 位写到相应外设的下一个描述符寄存器中。

(3) 设置相应外设的 DMA 配置寄存器中 DMA 使能位。

(4) 仅在单个 DMA 传送序列或链表中的第一个 DMA 传送序列需要进行写操作。

图 5-2 设置基于描述符的 DMA 的典型时序

2 基于自动缓冲的 DMA 传送

基于自动缓冲的 DMA 操作,除了不需要存储器中的描述符外,与基于描述符的 DMA 相同。在自动缓冲模式中, DMA 控制器是可写的,并且可以被处理器直接编程以发起一个 DMA 传送过程。一旦传送完成,控制寄存器被他们的原始设置值重载,以备下一次传送。这将产生一个循环缓冲区,并且不断地传送数据,直到通过将外设 DMA 配置寄存器的 DMA 使能位清零,才被禁止。如果允许中断,在传送过程进行一半 和完成 时,将产生中断。

下面是设置基于自动缓冲 DMA 的典型步骤:

(1) 将 DMA 配置寄存器中的自动缓冲使能位置 1 ;

(2) 初始化 DMA 传送计数器, DMA 起始地址高位寄存器, DMA 起始地址低位寄存器;

(3) 写 DMA 配置寄存器,对 DMA 传送进行设置,并将 DMA 使能位置 1. 这一部将启动基于自动缓冲的 DMA 的传送过程。

(4) 要停止 DMA 的传送,需要将寄存器中的 DMA 使能位清零,正在传送期间将位清零,不会像基于描述符的 DMA 那样引起 DMA 错误结束,一旦检测到 DMA 使能位被清零, DMA 传送寄存器 可以用来监视 DMA 传送状态。

3 存储器 DMA

存储器 DMA ( MemeDMA )控制器提供在 Blackfin 存储空间中存储器对存储器的 DMA 数据传送。这些存储空间包括外设组件互连( PCI )地址空间、 L1 、 L2 以及外部的同步 & 异步存储器。

MemDMA 控制器由两个通道组成。一个是源通道,用于读存储器,另一个是目的通道,用于写存储器。两个通道共享 一个可以存放 16 条记录的 32 位 FIFO 。源 DMA 通道写 FIFO ,目的 DMA 通道读 FIFO 。 FIFO 深度大大改善了内部与外部存储器之间的数据传送流量。 FIFO 支持 8 位、 16 位和 32 位的传送。但是,在 8 位和 16 位传送中,仅使用 32 位数据总线的一部分,因此,这两种传送的流量要比 32 位的 DMA 操作低。

MemDMA 控制器不支持基于自动缓冲的 DMA ,使用 MemDMA 控制器的传送必须是基于描述符的 DMA 。而且要有两个独立的描述符列链表,一个用于源 DMA 通道,另一个用于目的 DMA 通道。

因为源 DMA 和目的 DMA 通道共享一个 FIFO 缓冲,两个描述符中的传送计数必须设置为相同值,数据尺寸也设置为相同值。

4 二维 DMA

Blackfin-533 支持二维 DMA 的传送操作,其相关寄存器和功能如下:

(1) 配置寄存器( DMAx-CONFIG_yy_CONFIG )

设置二维 DMA 方式使能,中断产生的方式,其中中断可以在一行结束时产生,也可以在整个 DMA 结束时产生。

(2) 内层循环计数寄存器( DMAx_X_COUNT/MDMA-yy_X_COUNT )

在二维 DMA 时保存二维 DMA 内层循环的数目(行数)必须大于等于 2

(3) 内层循环地址增量寄存器( DMAx_X_MODIFY/MDMA_yy_X_MODIFY )

在二维 DMA 时保存每一次内层循环计数器加 1 后 DMA 操作(读或者写)地址在内存中的增量,此增量应该是二维 DMA 操作的数据单元长度的整数倍,比如二维 DMA 进行 16 位读 / 写,则此增量必须是 2 的 N 倍。

(4) 外层循环计数寄存器( DMAx_Y_COUNT/MDMA-yy_Y_COUNT )

在二维 DMA 时保存二维 DMA 外层循环的数目(列数)。

(5) 外层循环地址增量寄存器( DMAx_Y_MODIFY/MDMA_yy_Y_MODFIY )

在二维 DMA 时,保存每一外层循环计数器加 1 后 DMA 操作(读或者写)地址在内存中的增量,可以使负值,此增量应该是二维 DMA 操作的数据单元长度的整数倍。

参考书籍:《 ADI Blackfin 系列 DSP 处理器试验指导书》

本文详细介绍了DMA控制器的功能及其在Blackfin处理器中的应用。包括基于描述符和自动缓冲的DMA传送方式,存储器DMA(MemDMA)操作及二维DMA的配置与使用。

本文详细介绍了DMA控制器的功能及其在Blackfin处理器中的应用。包括基于描述符和自动缓冲的DMA传送方式,存储器DMA(MemDMA)操作及二维DMA的配置与使用。

1461

1461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?