#Direct I/O 操作

##框架流程

-

direct I/O(加载/存储)模块是所有传出的**direct I/O packets(direct I/O 包)**的来源。

-

通过direct I/O包,Rapid I/O包包含了目标设备上数据的存储地址和读取地址。

-

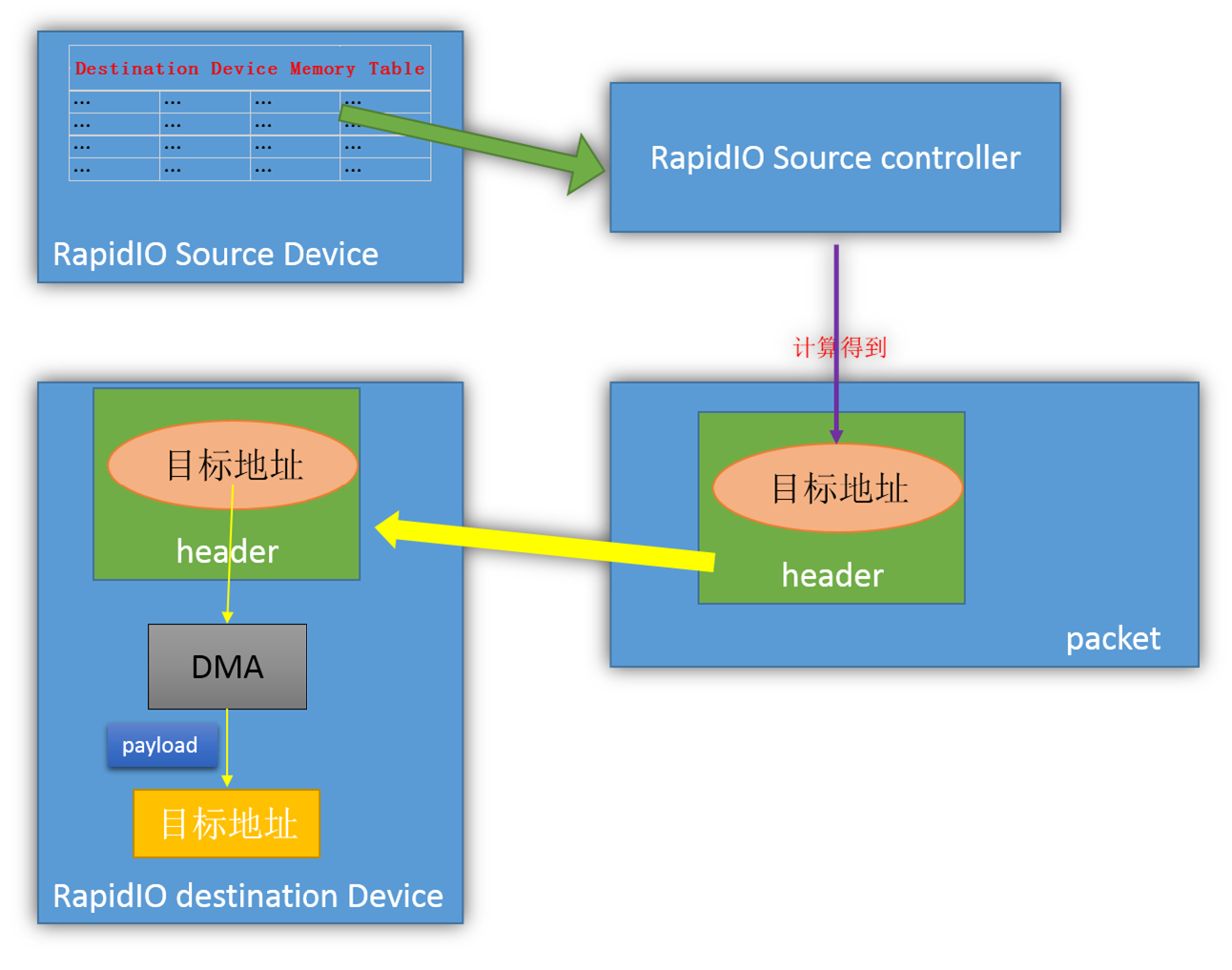

direct I/O 需要RapidIO源设备包含目标设备的本地存储器地址列表。

-

一旦地址列表建立,RapidIO源控制器就利用这些数据来计算目标地址,并将其插入到包header里。RapidIO目标外设从接收到的包header中提取目标地址,并通过DMA把包的payload传递给存储设备。

为方便读者理解,笔者作了示意图如下:

当CPU想把存储空间中的数据发送到外部处理单元(processing element (PE)),或者当CPU想从外部处理单元读取数据时,CPU提供RapidIO外设必须的各种信息,如DSP存储地址,目标设备ID,目标设备地址,包的优先级等。

payload是包的序列号,大家可以理解为包的指针。注意包一般都会有数据部分(data),header部分和payload部分。

一般来说,必须存在一种填满所有RapidIO包的header的所有区域的方法,Load/Store 模型提供了一种方法来处理这种信息交换。这种方法所依赖的是一系列的MMR(Memory Mapped Register 存储器映射寄存器),将这些寄存器作为传输描述符进行信息交换。CPU可以通过配置总线寻址这些寄存器。

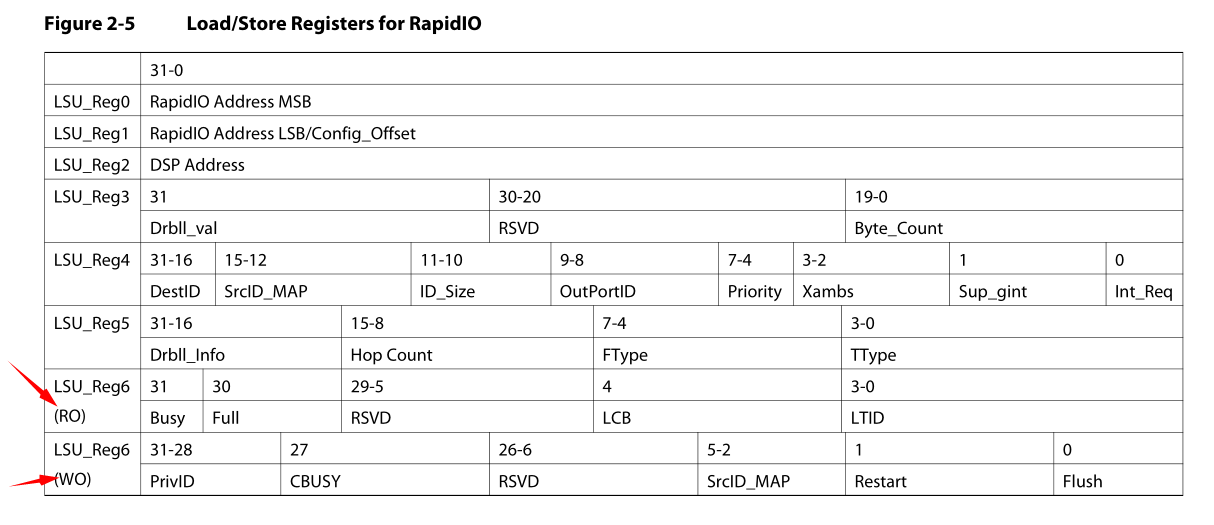

一共有8个LSU(Load/Store Unit),每个LSU都有自己的七个寄存器,即LSU_REG0-LSU_REG6,REG0-REG4用来存储控制信息,REG5、REG6用来存储命令和状态信息。除了REG6,其它寄存器都是可读可写的,只有REG6有只读和只写两种模式。

配置完LSU_REG6之后,传输就开始。有些必须的例如传输目标,传输源,都不需要人为配置,是硬件配置好的。

Figure2-5是每个LSU所拥有的寄存器。注意途中两个红色箭头指向的是REG6的两种模式。

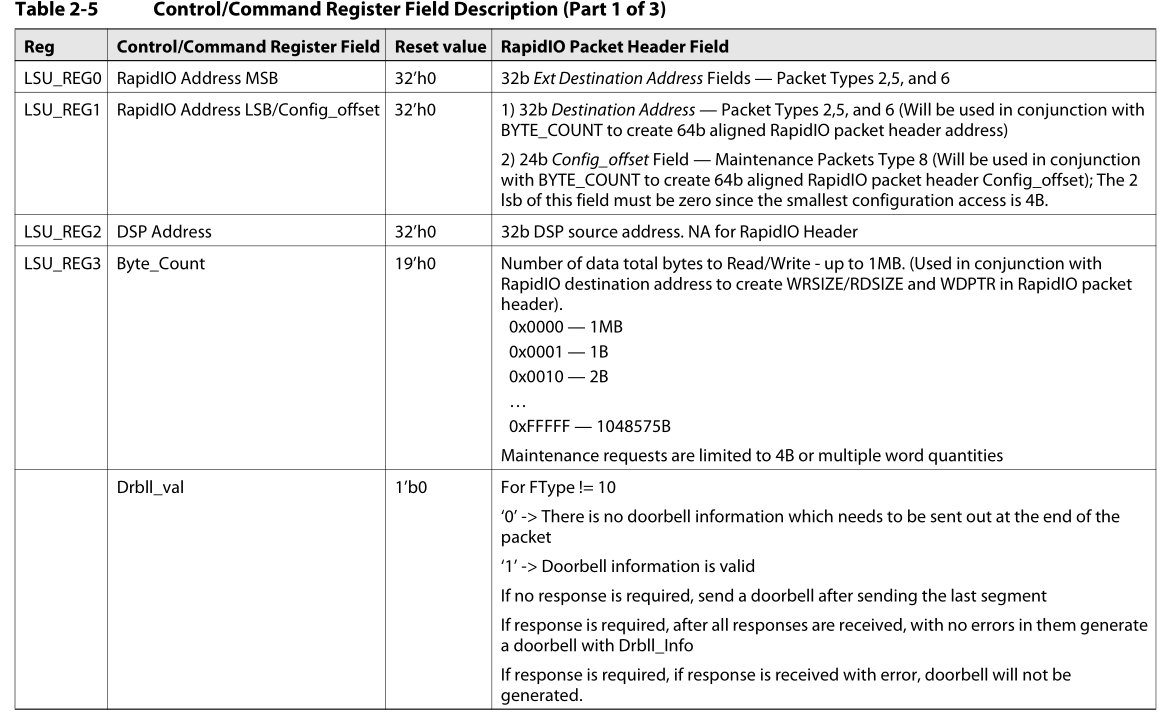

LSU的寄存器的域到RapidIO的包header的映射,在Table2-5中解释。

REG0中的内容代表RapidIO的地址高位,映射到RapidIO包header域中就是包要发送的扩展(这里原文档写的是Ext Destination Adress Fields,我理解为扩展地址,即如果地址位数过长可以使用这一位,也有可能是外部目标地址,具体在如何理解这个Ext)目标地址(只适用于包类型2,5,6)。

REG1中的内容代表RapidIO的地址低位,或者代表配置补偿(Config_offset),到底代表这两者中的哪一个还是

本文介绍了Direct I/O操作中的Load/Store Unit(LSU)框架,详细阐述了LSU的寄存器配置,包括其在Rapid I/O包header中的映射,以及在Direct I/O传输中的作用。通过配置LSU的寄存器,CPU能够发起数据传输到外部处理单元,同时讲解了LSU的控制、状态寄存器及其在传输过程中的交互机制。此外,还讨论了LSU的影存器管理和锁机制,以确保多个CPU安全地共享资源。

本文介绍了Direct I/O操作中的Load/Store Unit(LSU)框架,详细阐述了LSU的寄存器配置,包括其在Rapid I/O包header中的映射,以及在Direct I/O传输中的作用。通过配置LSU的寄存器,CPU能够发起数据传输到外部处理单元,同时讲解了LSU的控制、状态寄存器及其在传输过程中的交互机制。此外,还讨论了LSU的影存器管理和锁机制,以确保多个CPU安全地共享资源。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?