http://blog.csdn.net/hgf1011/article/details/5897729

C-state

1. Overview

插播:

s3: disable timer as wake source,

app not run,

suspend driver,

save device status

rtc精确到ms( 取决于晶振),靠这个同步时间,同时 rtc 是唤醒源。

s0i3: kernel timer active

app are running

AOAC: always online always connect

用户和中断等都可以唤醒

c6时:

电压很低

core clock off

L1 cache off

L2 cache off

wakeup time <100s

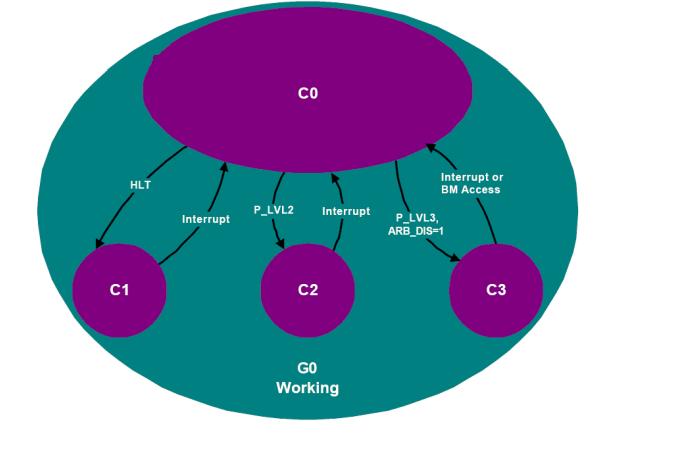

C-state是ACPI spec定义的CPU工作在G0时的power states,这些状态包括C0,C1,C2,C3…Cn.其中C0被称为Active状态,也只有C0的时候CPU才会执行指令;其余的状态则被称为sleeping,这时CPU是不执行指令的,也因而会节省更多的功耗。系统在运行时会根据loading状况在各个C-state之间切换 降低功耗,图1是C-state切换的一个简单的当CPU在进出sleeping state时会有一定的延时,通常延迟越大功耗对应的C-state的功耗就越低。APCI规定C0 C1 C2需要保持cache的一致性(要保证CPU cache中的数据一定要是最新的数据),C3以及后续的state就没有这个要求了,也就是说如果系统还要memory request,OS就不会进入C3以及之后的state。从信号上来看 比较旧的CPU架构上,C-state的切换是通过STPCLK#,SLP#,DPSLP#这几个信号实现的,在新的架构引入了QPI bus,切换C state的动作都会透过QPI Request Msg达成,上述信号在新的平台上都被remove掉了。

图 1

2. C-state Control

1) Detect & Enable C-state

BIOS可以通过CPUID function 5 check CPU是否支持C-state,以及支持哪些C-state(C1 C1E C3 C6 C7),支持的最大的C-state也可以通过MSR去设定,默认情况下增强型C-state以及IO MWAIT Redirection是不支持的,BIOS要根据系统的需求决定是否开启支持该功能的register,对于多核的系统就需要对每颗核都要单独去配置它的C-state的支持。

2) C-state Basic Configuration

通常情况下PPM code会根据MWAIT以及AC/BAT是否存在给出不同的配置方案如:a.当MWAIT支持的时候通常的做法是将CPU 的MWAIT(C1) 映射为ACPI C1,CPU MWAIT(C3)映射为ACPI C2, CPU MWAIT(C7)映射为ACPI C3,当AC存在时为了系统获得更高的性能通常会将MWAIT(C7)不再映射为ACPI C3,也就是支持ACPI C1 C2 两级C-state。b.当MWAIT不支持的时候就需要使用传统的读P_LVLX的做法,将HLT当做ACPI C1,P_LVL2当做ACPI C2,PL_LV4当做ACPI C3,同样在AC存在的状况下ACPI C3就不会被export出来了(以上做法的假设该CPU支持C6 C7,如果不支持的话就remove相关的support的code)。

3) ACPI Structure For C-state

l _OSC & _PDC

_0SC(Operating System Details) & _PDC(Processor Driver Capabilities)在功能上比较接近,基本上供OSPM调用和BIOS传递一些关于C-state P-state T-state是否支持,以及支持的程度和实现方式的一些设定,BIOS可以依据OSPM的参数回报相应的ACPI Structures。

l _CST

_CST是通过ACPI ASL code 汇报给OSPM的有关该平台CPU所支持的C-state的信息。它的格式如下所示:

CSTPackage : Package ( Count , CState ,…, CState )

其中Count表示所支持的C-state的个数

CState: Package ( Register , Type , Latency , Power )

Register表示OSPM调整C-state的方式,

Type表示C State的类型(1=C1, 2=C2, 3=C3)。

Latency表示进入该C-state的最大的延迟,

Power表示在该C-state时的功耗(单位是毫瓦)。

下述是一个sample code,注释部分已经讲的很明白了CPU0支持4个C-state,

其中

C1使用FFixedHW的方式访问,

其它3个C-state都是通过P_LVL方式切入,

第三和第四个Cstate都被映射到ACPI C3。

Name(_CST, Package()

{

4, // There are four C-states defined here with three semantics

// The third and fourth C-states defined have the same C3 entry semantics

Package(){ResourceTemplate(){Register(FFixedHW, 0, 0, 0)}, 1, 20, 1000},

Package(){ResourceTemplate(){Register(SystemIO, 8, 0, 0x161)}, 2, 40, 750},

Package(){ResourceTemplate(){Register(SystemIO, 8, 0, 0x162)}, 3, 60, 500},

Package(){ResourceTemplate(){Register(SystemIO, 8, 0, 0x163)}, 3, 100, 250}

})

l _CSD

C-State Dependency 用于向OSPM提供多个logic processor之间C-state的依赖关系。比如在一个Dual Core的平台上,每颗核可以独立运行C1但是如果其中一个核切换到C2,另一个也必须要切换到C2,这时就需要在_CSD中提供这部分信息。

3. P_LVL VS FFH

P_LVL称之为Level register,是在一些比较旧的Intel平台上用做切换C-state的一种方式比如切换到C2,就会去读LV2 然后系统就会进入一个叫做level 2 的power state(C2)。

FFH全称是Function Fixed Hardware,它是Intel特有的用于CPU power states之间进行切换的一个interface.

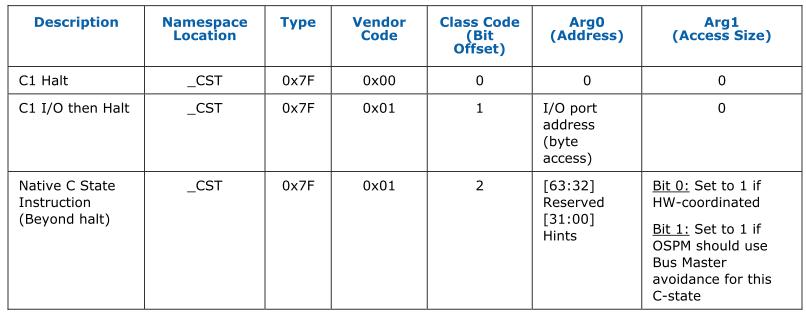

ACPI中的GAS被用于传递FFH的信息给OSPM,它有一个特定的Address_Space_ID(0x7F),这种GAS主要被用在_PCT _CST这样的ACPI Structure中。GAS在_CST中的格式如下图2所示:

图 2

OSPM解析到该_CST structure的ID是0x7F,在切换C-state时就可能就会去用Intel特定的native 指令MWAIT去切换,

其中Arg0 Arg1主要是MWAIT Extensions指令中传给ECX EAX的参数。

Intel之所以将切换C-state的方式从读取P_LVL改成MWAIT指令的方式主要应该是因为性能和时间上的影响,P_LVL的方式就通过IO read 4**地址的方式去做的,IO读取是比较慢也是比较耗时的,所以改成现在通过MWAIT的方式去做,可是现在的CPU仍然可以通过开启IO MWAIT Redirection的方式支持以前的P_LVL的做法。下面的_CST是使用FFH的一个例子:

Name(_CST, Package()

{

2, // There are four C-states defined here with three semantics

// The third and fourth C-states defined have the same C3 entry semantics

Package(){ResourceTemplate(){Register(FFixedHW, 0x01, 0x02, 0x0000000000000000,0x01)}, 0x01, 0x03, 0x000003e8},

Package(){ResourceTemplate(){Register(FFixedHW, 0x01, 0x02, 0x0000000000000010,0x03)}, 0x01, 0xf5, 0x0000015e}

})

REFF:

1. ACPI Spec 3.0

2. Intel Processor vendor-Specific ACPI

That’s all!

Peter

2010/9/20

2469

2469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?