快乐虾

http://blog.csdn.net/lights_joy/

lights@hb165.com

本文适用于

ADI bf561 DSP

uclinux-2008r1.5-rc3 (移植到vdsp5)

Visual DSP++ 5.0(update 5)

欢迎转载,但请保留作者信息

ENTRY(_real_start)

[ -- sp ] = reti;

p0.l = lo(WDOGA_CTL);

p0.h = hi(WDOGA_CTL);

r0 = 0xAD6(z);

w[p0] = r0; /* watchdog off for now */

ssync;

这个是_real_start的开始,不知为何这里要将reti入栈?此时SP仍然指向scratch pad,下面马上就要改变SP指针了。

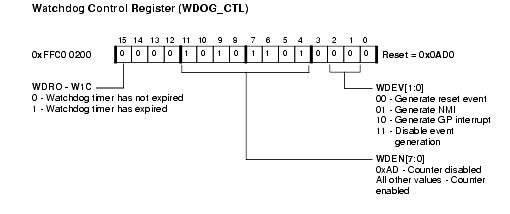

Watchdog就比较好理解了,下面是WDOGA_CTL寄存器的意义:

1 参考资料

head.s分析(1):保存u-boot传递过来的指针(2009-1-19)

head.s分析(2):SYSCFG配置(2009-1-19)

head.s分析(3):数据及指针寄存器清0(2009-1-19)

head.s分析(4):关闭CACHE(2009-01-19)

head.s分析(5):关闭串口(2009-01-19)

head.s分析(6):栈指针初始化(2009-01-19)

head.s分析(7):init_early_exception_vectors(2009-1-19)

head.s分析(8):配置PLL及SDRAM(2009-01-20)

head.s分析(9):EBIU配置(2009-01-20)

head.s分析(10):转入中断15(2009-01-20)

3611

3611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?