实验总体流程:

1编译代码或拼图

2编译仿真

3“pins”编译管脚(对照使用手册)

4“device”选择芯片和服务(EPCS4;EP3C16F484)

5再编译

6 tools->program 下载编译文件

STEP1:

本实验要求设计一个精度为1/100秒,范围0~99.99秒的计时器,四个LED数码管显示,使用2个按键控制计时的启动、暂停、清零。

1.先new一个名为led_count1的Verilog HDL file,用来编写本工程所需要的组合逻辑单元。截图如下:

组合逻辑单元代码设计

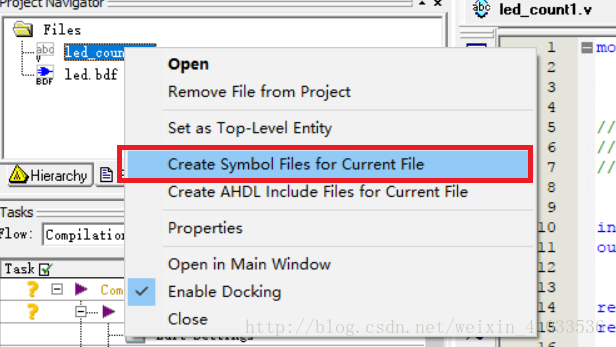

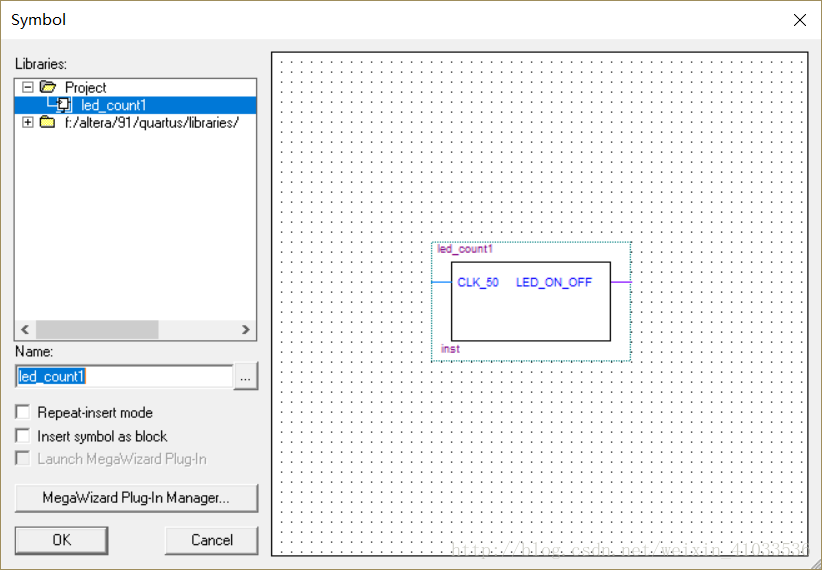

编译完成后,右击该文件将其生成symbol file,在后面的拼图过程中将用到该单元。

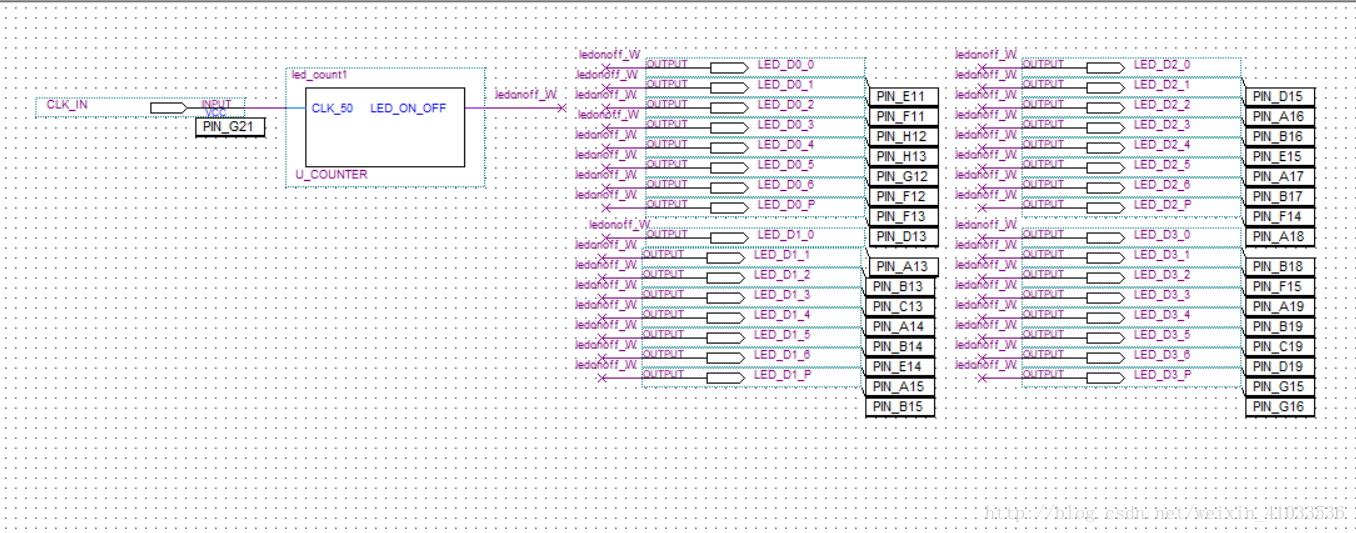

2.new一个blockdiagram file,将上文中准备好的组合逻辑单元加入进去,连接输入时钟信号与32个输出信号引脚。截图如下:

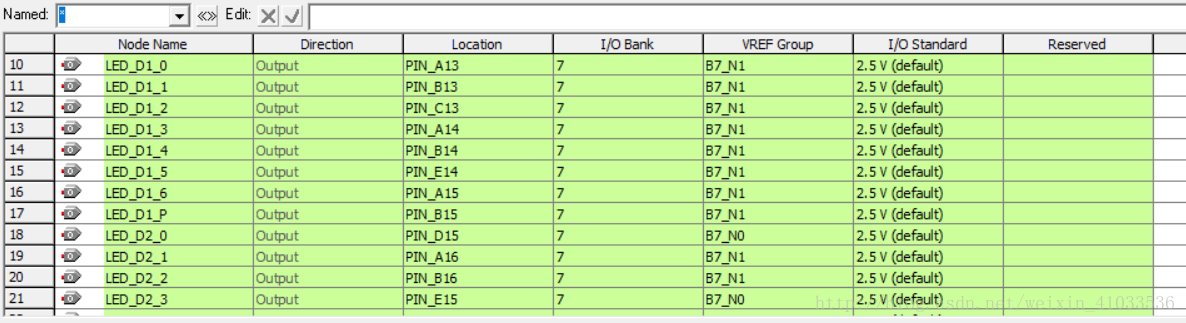

3.为32个输出信号设置引脚,点击assignments->pins,对照4个LED灯的引脚编号填写location。

填写完成后再次编译一次,可以看到每个输入信号旁出现了对应的引脚编号(如上上图所示)。

点击assignments->device->device and pin options->configuration,将useconfiguration device设为EPCS4。

4.点击tools->Programmer,将程序下载到FPGA中,点击start后等待progress达到100%,可以看见DE0的四个LED灯每秒闪烁一次,符合实验预期。

STEP2:

大体操作流程与STEP1类似,只不过由拼图改为全部电路功能由Verilog代码编译实现。依据例子实验代码进行编译可得实验结果。

STEP3:

本阶段的设计目标为设计一个可以从0.01秒计数到99.99秒的计时器电路。

分析例子实验代码,可以将本实验主体分为三个主要模块:脉冲生成器、脉冲计数器、译码显示器。

脉冲生成器gen实际上是四个脉冲生成子模块级联,下一级脉冲生成模块满十生成一个溢出信号,上一级只有在下一级的溢出信号出现时才生成本级的脉冲,每一级脉冲生成模块由脉冲计数(R)和脉冲延迟计数(dlR)两者组成。每一级脉冲溢出时还将溢出信号发送给其对应的脉冲计数器进行计数。

脉冲计数器counter实际上是两个D触发器相连,来捕捉对应脉冲生成模块发出的溢出信号,周期为10。将计数值信号输出给译码显示器显示。

译码显示器BCD实际上就是一个3-8译码器,它将输入的脉冲计数值显示成对应的LED数码管电平,点亮七段数码管中对应的数码管。

STEP4:

本阶段在阶段3的基础上,添加以下功能:上电的自动复位,上电后自动生成复位信号,把所有模块复位;添加一个暂停/继续的功能按钮,需要去抖;添加一个计数清零后暂停的功能按钮,需要去抖。

本阶段实验大体思路与STEP3一致,在其基础上增加了上电复位模块和按键去抖模块。参考例子实验可以实现上述要求。同时需要注意的是,由于按键的要求,还需要增加一个信号控制模块来控制整体的按键运行状态。

信号控制模块control实际上是一个状态机,它规定了程序三个状态及跳转条件:run状态正常计数,stop状态暂停计数,clear状态清零并暂停计数,通过输出R1S0和CZ两个信号来控制程序的运行状态。

实验作业:

实验要求设计满足以下功能的计时电路:最小显示精度为1秒,60进制,从0计时到59分59秒;使用拨码开关和按键,能够设置时间的功能,建议形式如下 * 采用4个拨码开关,任何一个开关拨到上方时,对应的数码管开始闪烁 * 闪烁的数码管应当仍能正常更新计时的显示值 * 采用“增加”和“减少”2个按键 *每按下“增加”按键一次,闪烁的数码的显示值加1,并且以0-60回绕 * 每按下“减少”按键一次,闪烁的数码的显示值减1,并且以0-60回绕;不准使用多个时钟,所有D触发器用同一个时钟工作。

本实验的大致原理如下:

将整体分为三个部分:脉冲生成器、脉冲计数器、显示器。

脉冲生成器每生成一个最小单位的脉冲(如1秒),使级联的上一层脉冲生成器生成一次脉冲(进位)、使对应的计数器计一次数。

脉冲计数器将生成的计数传到显示器中进行显示。

1. 生成59分59秒、60进制、精度为1秒的计时器(已完成):

在脉冲生成器内部多设两层级联,取1秒最为最小单位输出脉冲,同时设1秒脉冲生成器的最大值为9,10秒脉冲生成器的最大值为5,1分钟脉冲生成器的最大值为9,10分钟脉冲生成器的最大值为5。

与脉冲生成器对应的脉冲计数器的最大值也对应相同。

2. 拨码开关对应显示管闪烁(已完成):

设置四个拨码开关输入信号,每个拨码开关输入信号即为对应显示器的使能信号,只有输入1时才进行显示。

3. 按键加循环(已完成):

即每按一次对应按键,从1秒脉冲生成器中手动生成一个1秒脉冲。其他操作与正常的计时器运行操作一致。

4. 按键减循环(已完成):

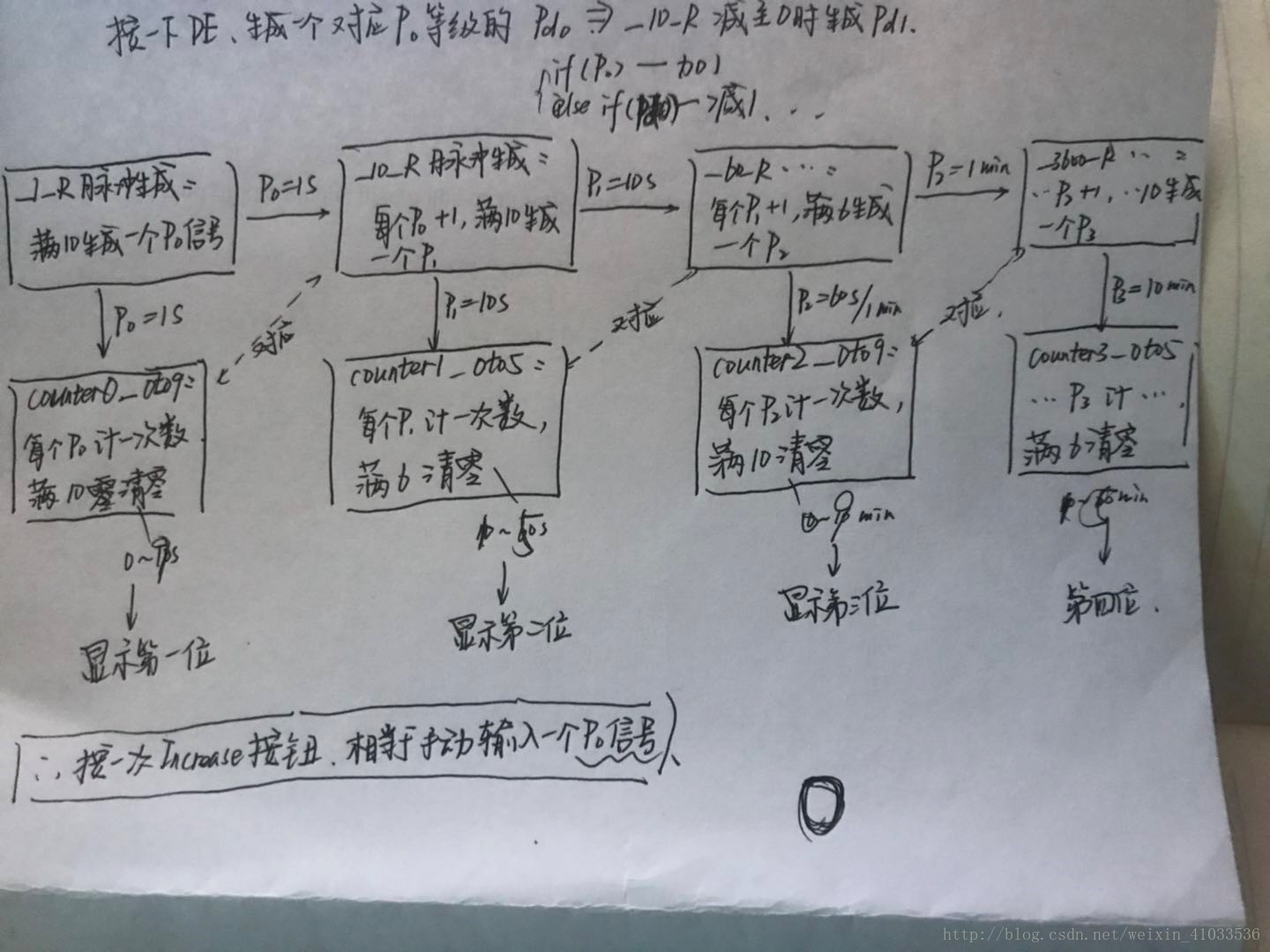

即每按一次对应按键,从1秒脉冲生成器中手动生成一个“1秒减脉冲”。该脉冲生成后使级联的上一层脉冲生成器生成一次减脉冲(借位)、使对应的计数器减一次数。而这两者内部计数应该是对应相等的,所以用一个与脉冲信号(如P0)同级的减信号(如Pd0)控制循环减。同时设1秒脉冲生成器减至0时置为9,10秒脉冲生成器减至0时置为5,1分钟脉冲生成器减至0时置为9,10分钟脉冲生成器减至0时置为5,同时向上一级脉冲生成器生成借位减信号(如Pd1、Pd2、Pd3)。

在脉冲计数器中,为Pd信号分配两个相连的D触发器(与P_IN信号的结构相同)用来捕捉跳变。

实验问题与总结:

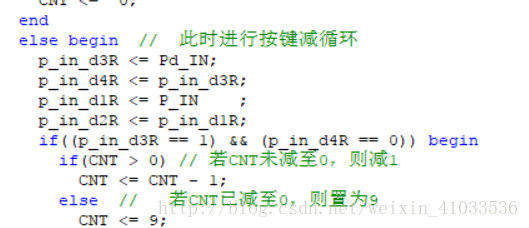

在完成按键减的过程中,一直出现错误,虽然程序并未报错,但对代码进行多次改进仍得不到预期结果。后来在仔细观察RTL视图并使用signalTap查看数据波形结果,发现是在脉冲计数器单元,由于控制变量写错(之前的if语句要求Pd_IN==1时p_in_d3R才读入Pd_IN)导致D触发器对Pd_IN信号的跳变捕获出现问题,从而影响了实验结果。

这说明由于自身由软件出身向硬件入门过程中,仍然是编程思想,思考问题仍是从代码出发而不是电路逻辑出发,经常会导致出现了逻辑问题而找不到问题的源头,在之后的学习过程中必须要更加重视观察RTL视图,使用波形仿真测试电路模块的逻辑组合正确性,以电路组合逻辑思维考虑问题。

3308

3308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?