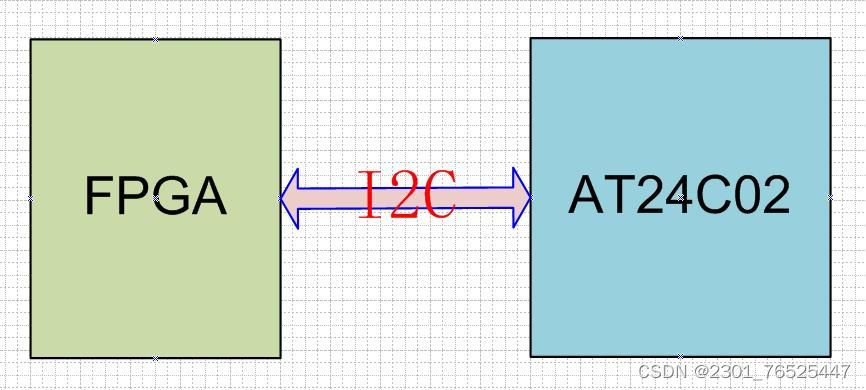

FPGA 全部verilog代码实现I2C口master端口应用场景

1、FPGA通过I2C口配置TFP410MP

2、EDID配置,FPGA通过I2C口配置AT24C02 AT24C64;

访问地址位宽支持8bit和16bit;

访问数据位宽8bit;

代码已上板测试验证,正确可靠;

ID:31100644998999376

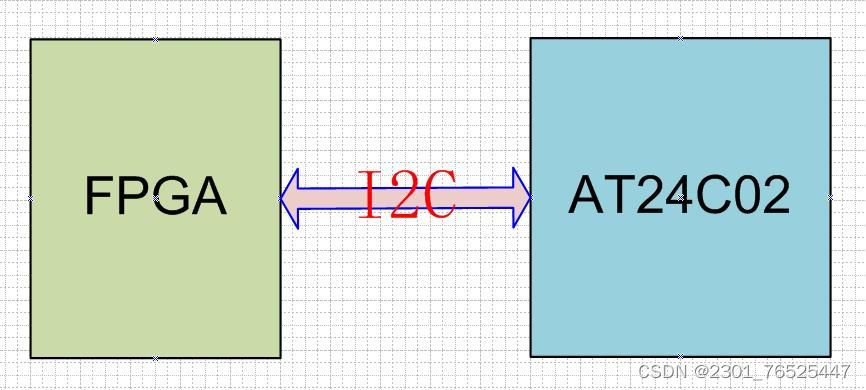

FPGA 全部verilog代码实现I2C口master端口应用场景

1、FPGA通过I2C口配置TFP410MP

2、EDID配置,FPGA通过I2C口配置AT24C02 AT24C64;

访问地址位宽支持8bit和16bit;

访问数据位宽8bit;

代码已上板测试验证,正确可靠;

ID:31100644998999376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?