文章内容来源于【中国大学MOOC 华中科技大学通信(高频)电子线路精品公开课】,此篇文章仅作为笔记分享。

目录

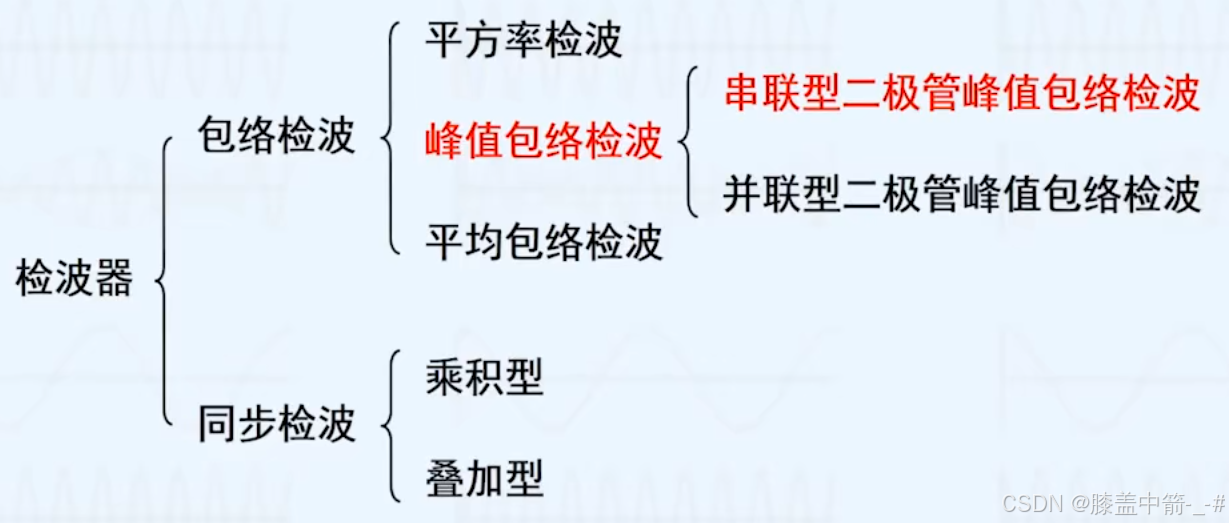

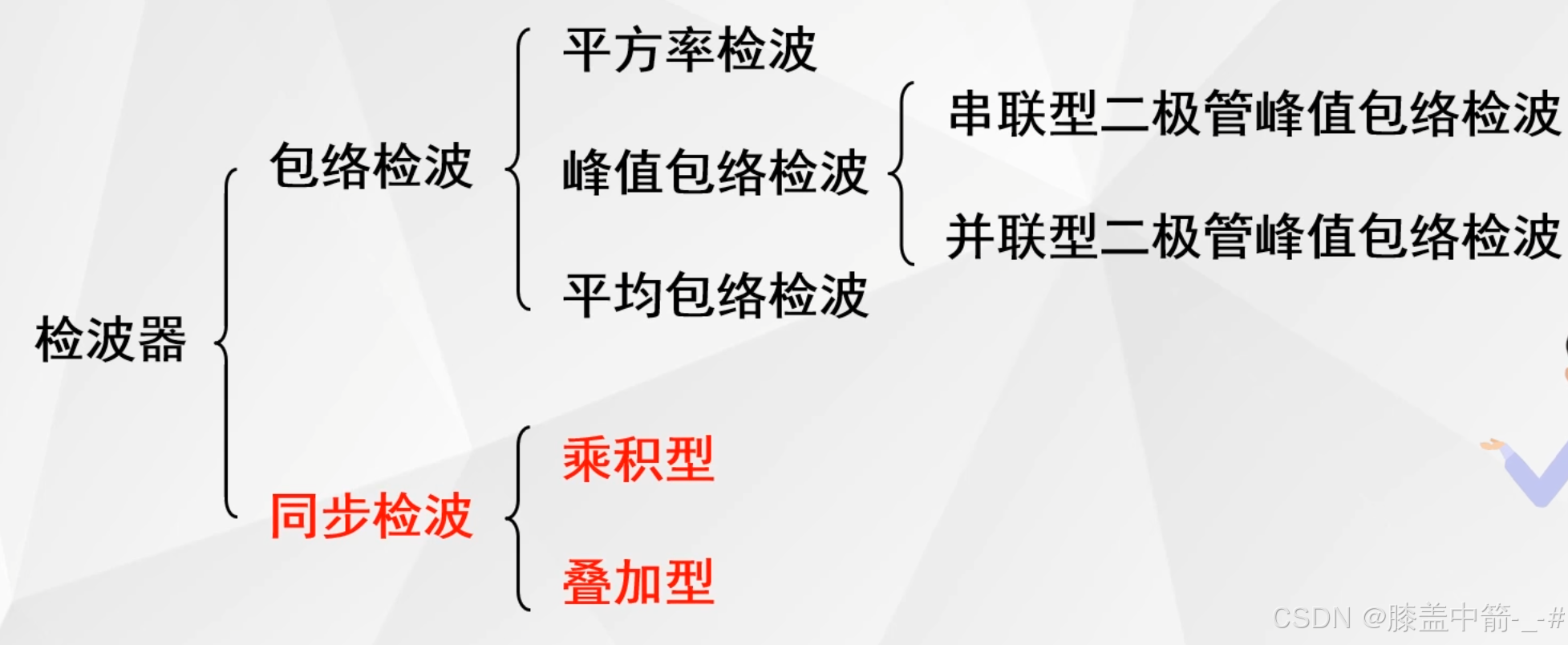

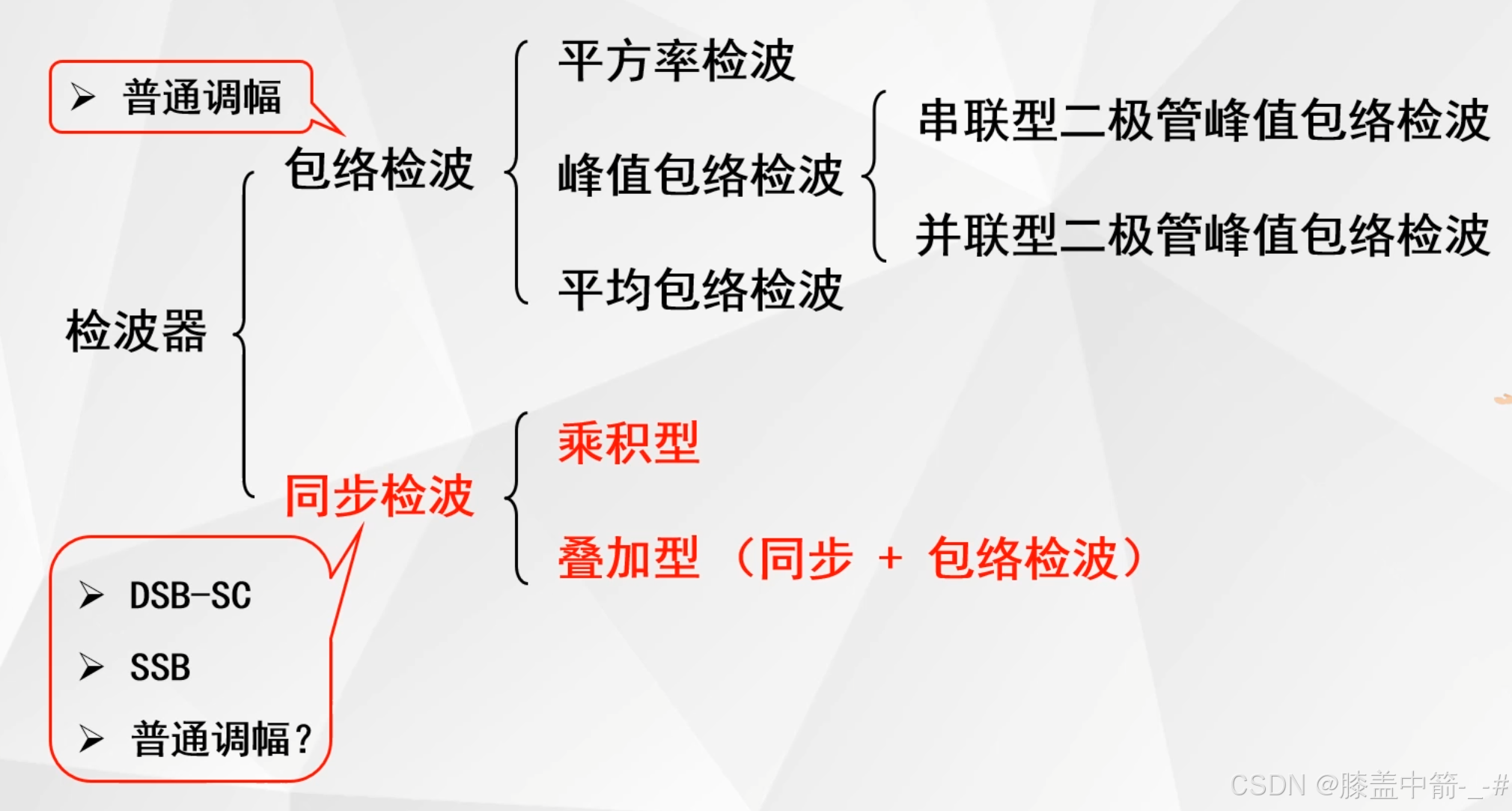

检波

峰值包络检波

包络检波时域和频域(单频调制)

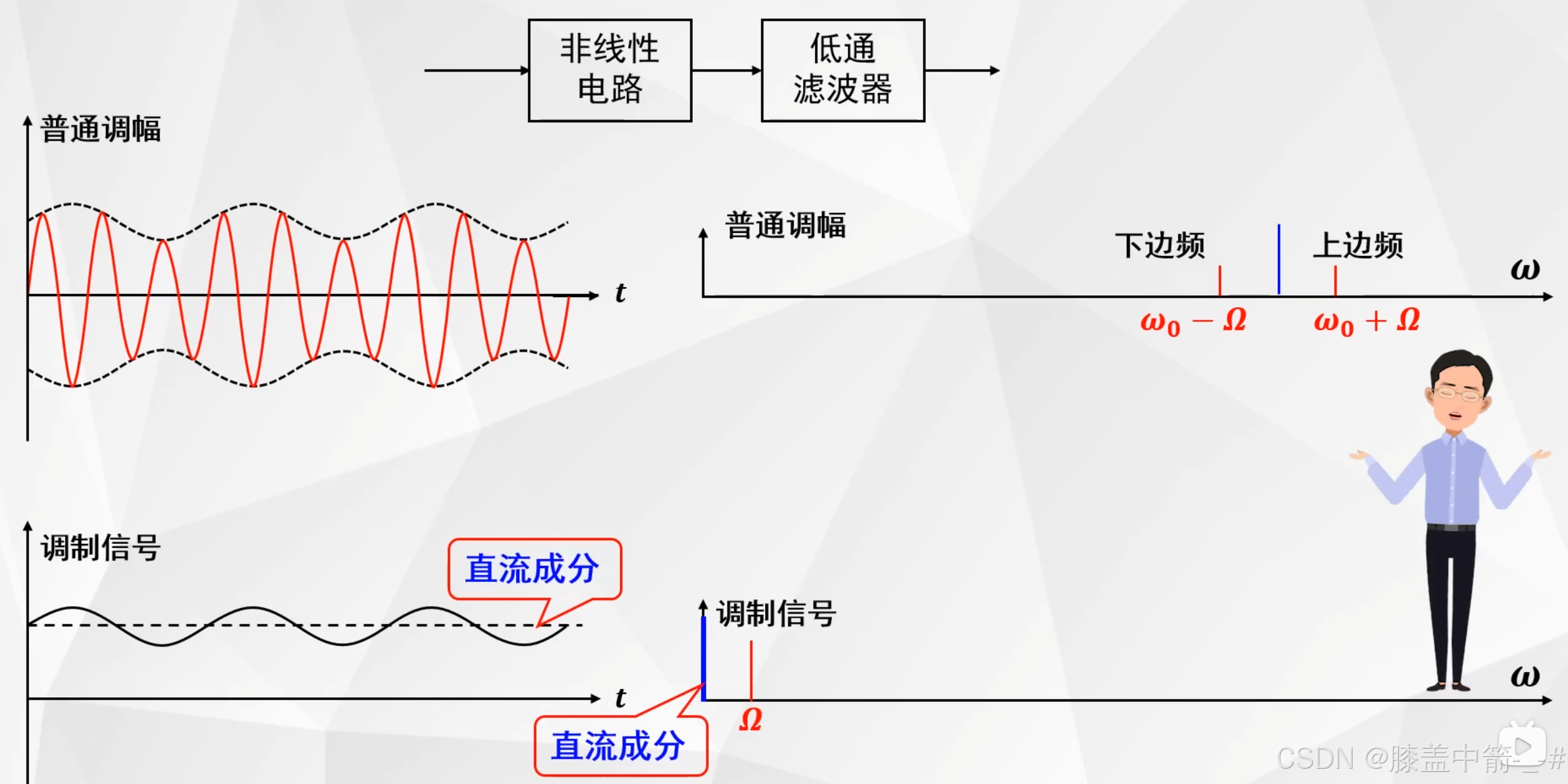

对于检波而言,本质也是频谱搬移,所以也需要去了解其时域和频域。

- 以单频调制为例,输入的信号为普通调幅信号,通过非线性电路可以产生频率变换,进行频谱搬移。在经过低通滤波器以后,就可以取得包络,这也是为什么将其叫作包络检波的原因。

- 注意包络线为虚线,解调出来的调制信号是实线。为什么虚线能够变为实线呢?

- 对于其频域而言,输入信号为普通调幅的已调制信号,包括载波和两个边频。经过频谱搬移以后,把高频的信号搬移到了低频,由于另外一个边带变为了负的,没有了物理意义,在零频域点上相当于直流成分。

串联型二极管峰值包络检波

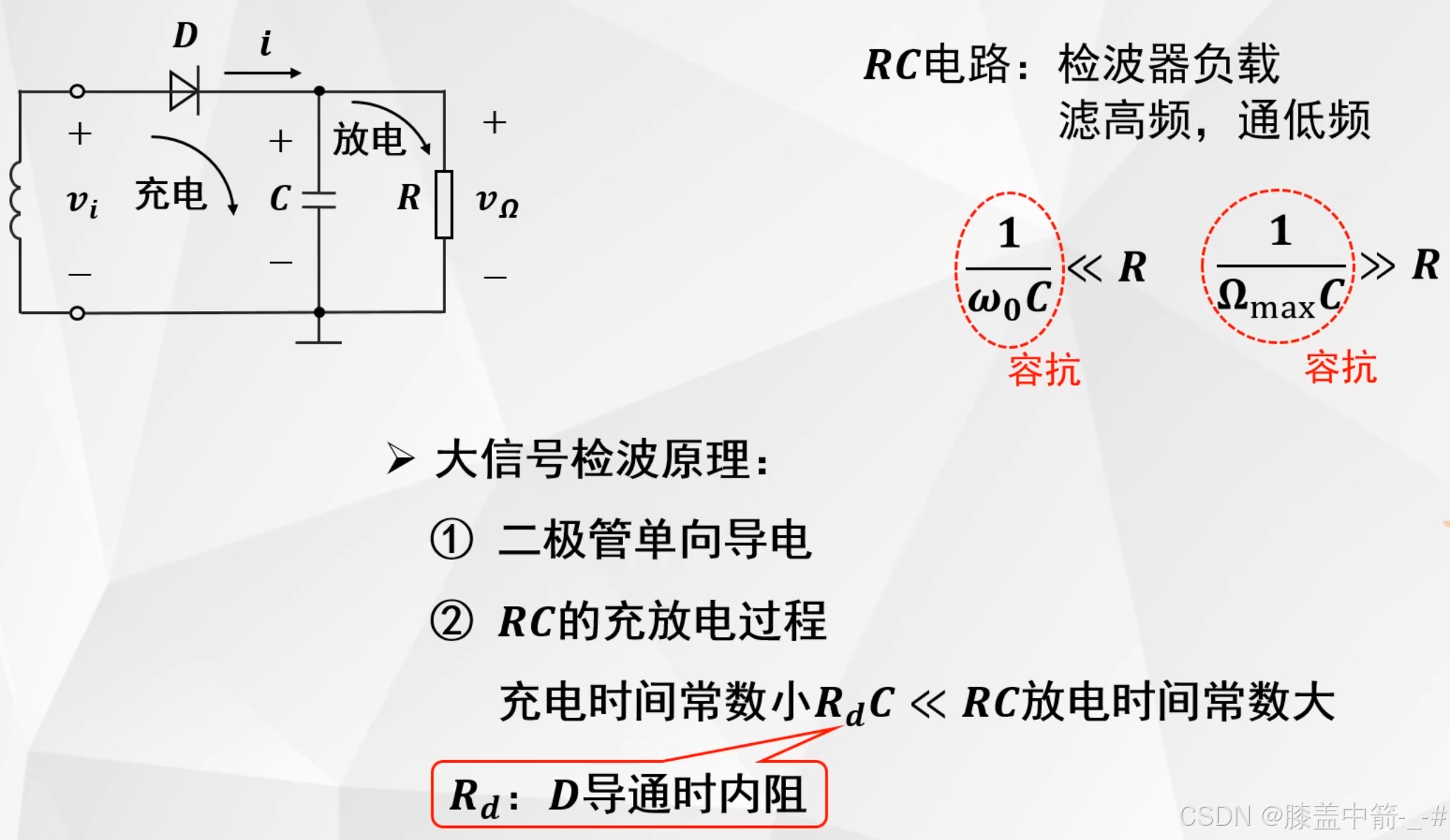

以串联型二极管峰值包络检波为例,来解释如何使虚线变为实线将信号检波出来。

- Rd:二极管正向导通的电阻,一般很小

- 二极管的特性只能一个半周期通过,对于RC电路组成检波器的负载,需要滤高频、通低频。对于高频而言,其容抗比较低,高频可以直接通过电容短路到地;对于低频而言,其容抗较大,因此不会被短路,而是通过电阻R再送到下一级。

- 对于串联型二极管峰值包络检波而言,输入信号要求大于0.5V,因此也叫作大信号的检波器。

- 充电时间常数小,充电时间短,所以电容上的电压可以迅速达到输入电压的峰值,故这样的包络检波也叫峰值包络检波;放电时间常数大,放电时间比较长,所以电容上的电压会一直保持着峰值的电压。

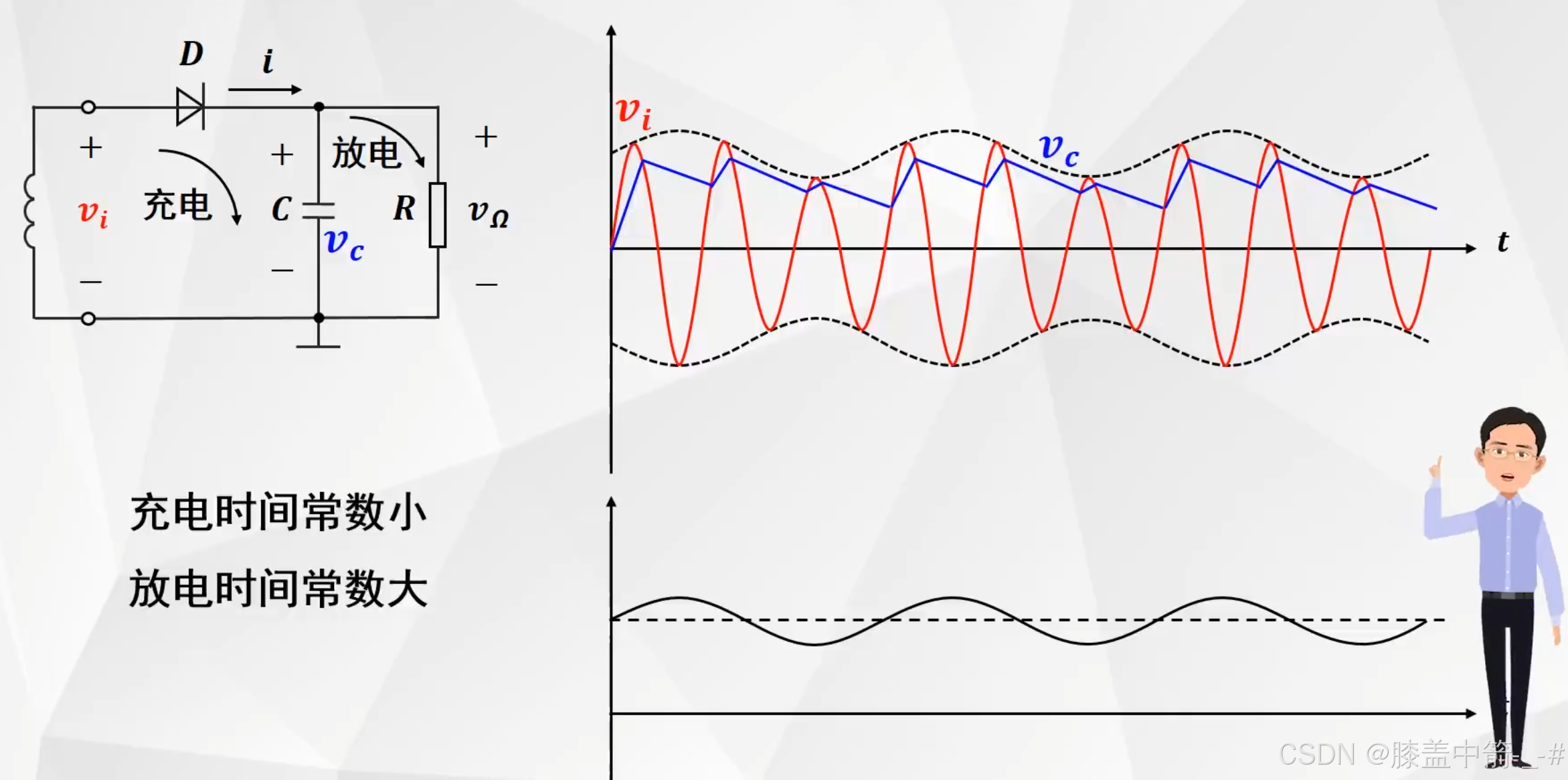

假设输入的是普通调幅的已调辐信号,输入电压为vi,根据充电时间短,放电时间长来分析。

- 当第一个正半周信号进来的时候,二极管导通,输入电压对电容进行充电。充电时间很短,很快就能达到输入信号的峰值,也是为什么叫峰值包络检波的原因。

- 达到峰值以后,输入信号小于电容电压,二极管将要截止,此时电容上的电压对电阻放电。由于放电很慢,电压下降很慢,基本维持在峰值的位置,体现可以把峰值的包络给选出来。

- 当输入信号第二个正半周到达时,而且当输入信号vi大于电容电压vc的时候,二极管再次导通,快速对电容C充电,此时电容电容C上可以快速得到输入信号的第二个正半周的峰值。

- 当输入信号又低于电容电压的时候,二极管再次截止,此时电容将对电阻R放电。放电时间很长,也基本维持着第二个正半周的峰值。

- 以此类推,每一次充电时间很快,放电时间很慢,保持的电压均为每一个输入信号的正半周的接近峰值的点。也就是选出了包络线的峰值的电压,得到的蓝色的曲线,就是接近于输入信号的包络线的,当载波频率比较高的时候,蓝色折线将很接近于红色包络线。

- 然后再通过低通滤波器滤除折线中的高频成分,即可得到光滑的调制信号,这就是峰值包络检波的基本原理,从而也解释了将虚线变成实线的一个过程,其中最关键的元器件就是电容,其充电时间短、放电时间长。

小结

包络检波失真

对角线切割失真(惰性失真)

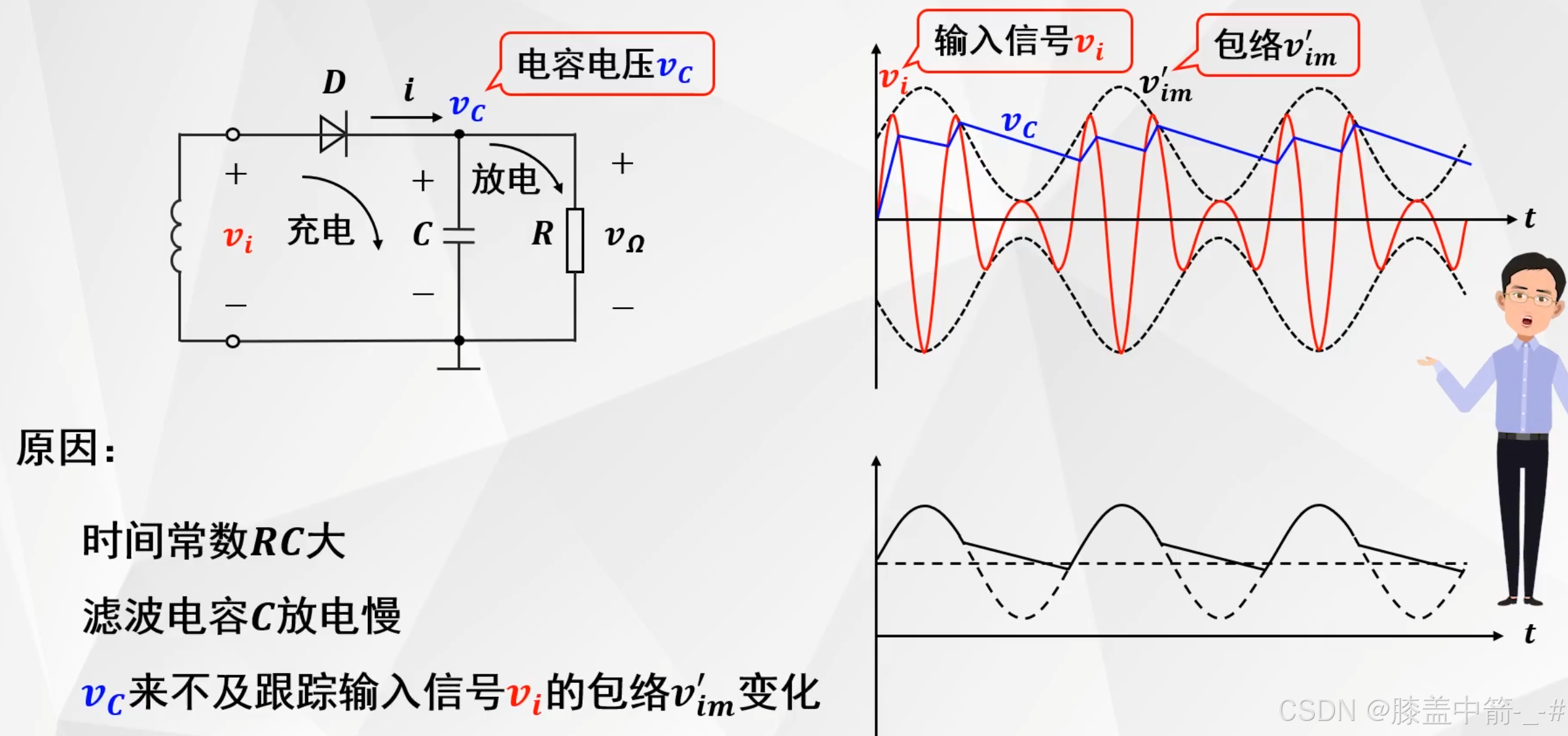

包络检波的电路,其参数的设置使得充电快,放电慢。

vi:输入的已调幅信号

v'im:包络线

对角线切割失真的原因

- 放电时间常数RC比较大,使得滤波电容C放电时间慢,可能会导致电容电压Vc来不及跟踪输入信号vi的包络v'im的变化。

- 根据峰值包络检波的原理,充电时间快,放电时间慢,因此可以保持输入信号包络的峰值。

- 充电时间快,放电时间慢,在输入信号比较小的时候可能会出现问题。由于输入信号比较小,而放电时间常数比较大,在电容C上储存的电位此时较高,所以二极管负极电位比较高,正极二极管电位比较低,导致二极管截止。

- 截止就导致了输入信号无法对电容进行充电,就是滤波电容无法得到此时输入信号的峰值,也就会丢失了包络信息。形状类似对角线,所以称其为对角线切割失真,也叫作惰性失真,因为其时间常数较大,放电比较慢,可以理解为其惰性比较大。

- 因此经过包络检波之后得到的调制信号就变成了有一部分被切割掉的形状。

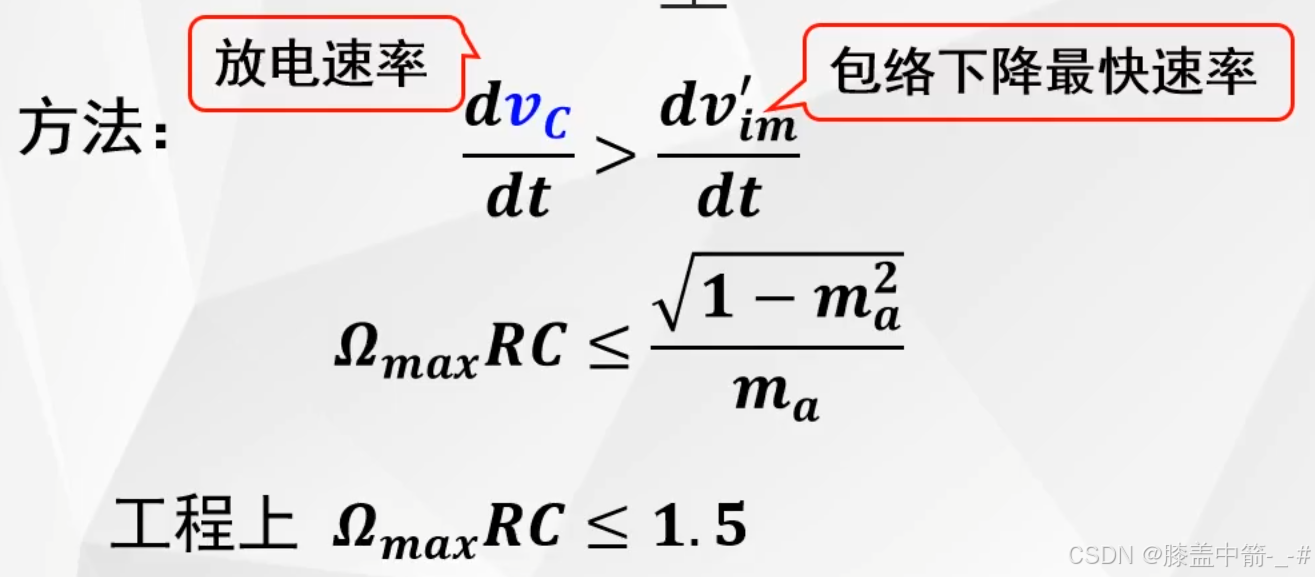

如何避免对角线切割失真

- 根据分析可以知道,主要的原因是放电太慢,所以只需要提升放电的速率,具体的使得放电速率大于输入信号包络的最快的速率即可。

- 可以得到关于调幅指数ma的选择的条件,对于工程上的使用,可以采用下面的式子。所以在选择ma的时候是有要求的,ma选择合适就可以避免对角线切割失真。

底部切割失真(负峰切割失真)

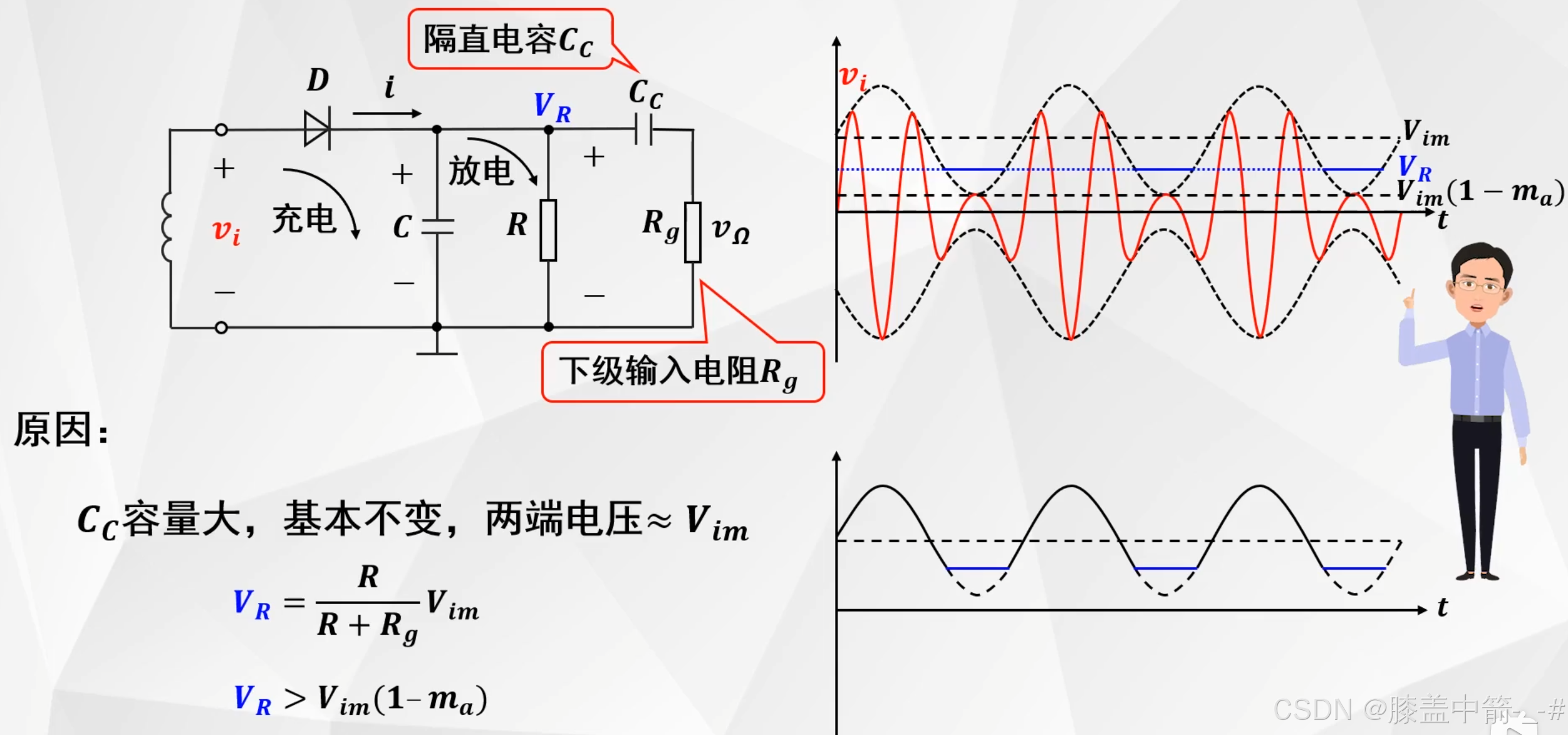

对角线切割失真,主要是考虑了电容C和电阻R。对于包络检波而言,有隔直电容Cc还有下一级的输入电阻Rg,因此还需继续考虑之后是否还会产生失真。

vi:输入的已调幅信号

Vim:包络上的电压

VR:直流电压经过两个电阻分压后在二极管负极产生的电位

底部切割失真的原因

- 由于隔直电容Cc比较大,在一个周期内电压基本不变,在稳定的时候,其两端的电压约为Vim,根据调幅指数ma可以得到最低点的电压Vim(1-ma)。

- 由于隔直电容Cc上存在一个直流电压,那么经过电阻R和下一级的输入电阻Rg分压以后,在二极管的负极就会产生一个电位记作VR,VR会对二极管的导通和截止造成影响。

- 如果VR的电压大于最低点的电压Vim(1-ma),就可能造成底部切割失真。由于图中VR的电位(蓝色)高于输入信号的电压,所以对于二极管而言,在这种情况下是截止的,二极管截止之后,包络检波器无法得到此时输入信号的峰值,丢失了包络的信息,出现了底部切割失真,正好是VR电位的位置切割出来的。

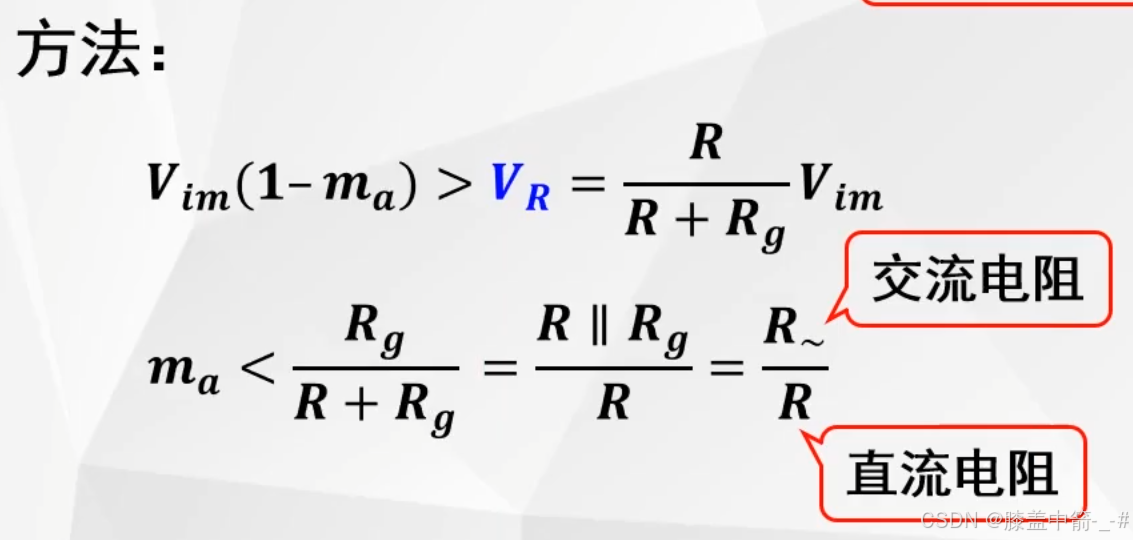

如何避免底部切割失真

- 根据分析的原理,只要让刚刚的式子不出现即可,就是只要让VR小于Vim(1-ma)的时候就可以。

- 将式子化简就可知道,在选择ma的时候有一定的要求,需要考虑到以上关系式。

- 为了使用方便继续化简,将其化为R交流和R直流。所谓的交流电阻是指交流的等效总电阻,由于在交流的情况下,隔直电容Cc短路,所以交流总的电阻是R||Rg;直流电阻就是直流的等效电阻,直流无法通过隔直电容Cc,所以直流总电阻就只有R(其中Rg<<R,就能满足R并上Rg等于Rg,R加上Rg等于R)。

- 选择调幅指数ma的时候,并不是越大越好,因为有限制条件,但是ma太小,效率就会比较低,所以ma的选择会有较多限制。

非线性失真

主要是由二极管的非线性特性引起,可以通过选择较大的负载电阻R来减小非线性失真的影响。

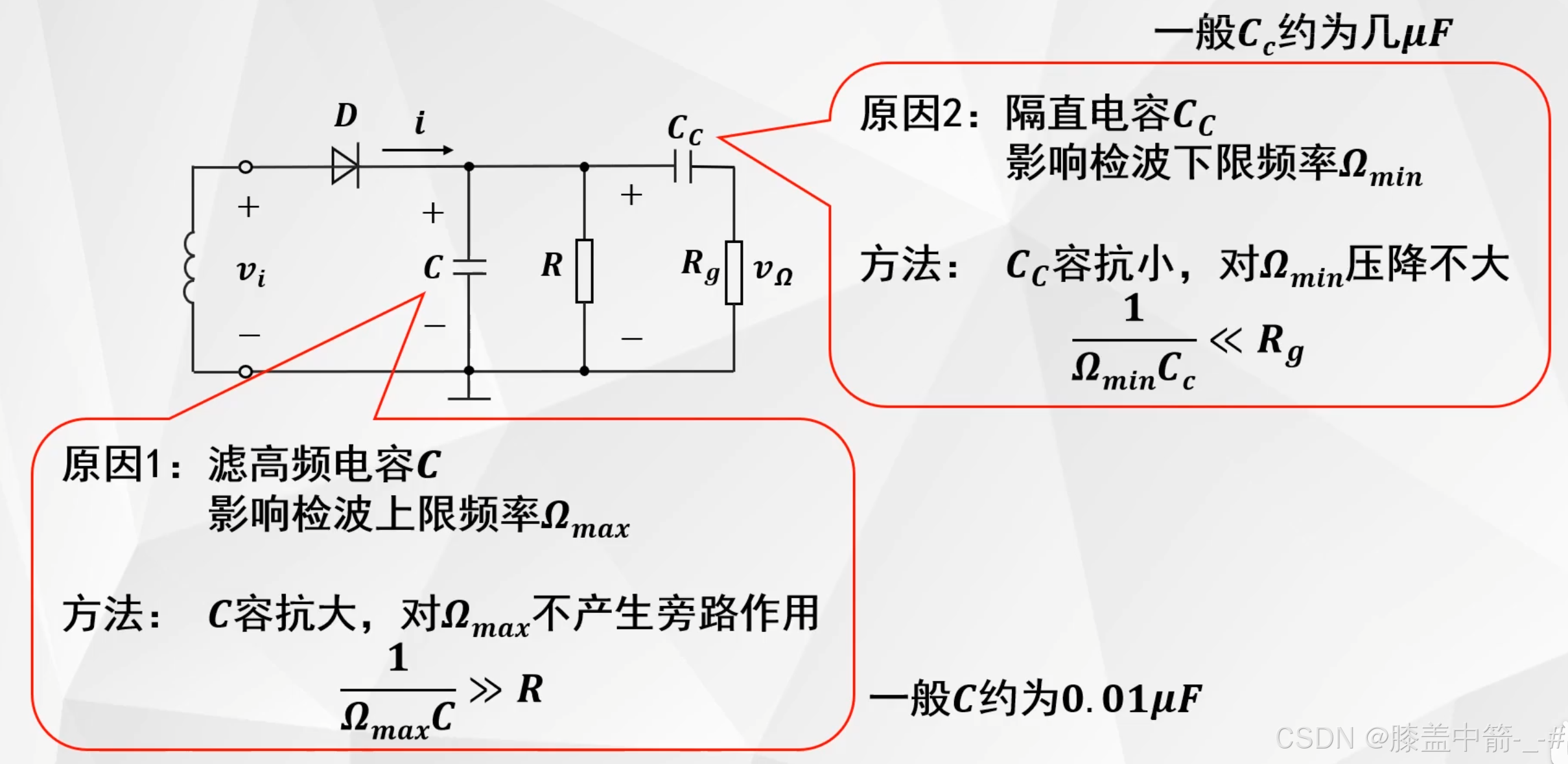

频率失真

主要是考虑两个电容:滤波电容C和隔直电容Cc。

C:滤波电容

Cc:隔直电容

Ωmax:检波后调制信号的上限频率

Ωmin:检波后调制信号的上限频率

- 滤波电容C是滤除高频的,所以可能会对检波出来的调制信号的上限频率有影响。

- 希望高频的信号频率能够通过电容,若滤波电容C的容抗远大于R,就不会短路到地,对Ωmax不产生影响。

- 隔直电容Cc可能会影响到调制频率的下限频率。

- 希望低频的信号频率能够通过电容,就是隔直电容Cc对调制信号的下限频率的容抗比较小,因此需要隔直电容在Ωmin上的容抗远小于Rg,这样就不会在Cc上有电压的损失,而更多的电压是在Rg上。

- 一般来说,滤波电容C取到0.01uF;隔直电容Cc取到几uF。

小结

- 前两者是包络检波特有的失真,共同点是二极管不能够即使的导通,使得包络的信息被切割掉了一部分。

- 对角线切割失真主要是因为滤波电容C,充电快、放电慢所引起的;底部切割失真主要是因为隔直电容Cc,使得二极管负极电位Cc大于输入信号最低点的电压Vim(1-ma)所引起的。

同步检波

包络检波的缺点主要是针对抑制载波双边带的调幅,由于抑制载波双边带调幅的波形信息有正有负。如果用包络检波来检波的话,只能取到一个半周期,这是因为二极管的原因。假设取到正半周,就是蓝色框取出来的包络线,可见其与实际的红色调制信号是有较大差距的,因此包络检波无法正确的解调抑制载波的双边带调幅,所以需要同步检波。

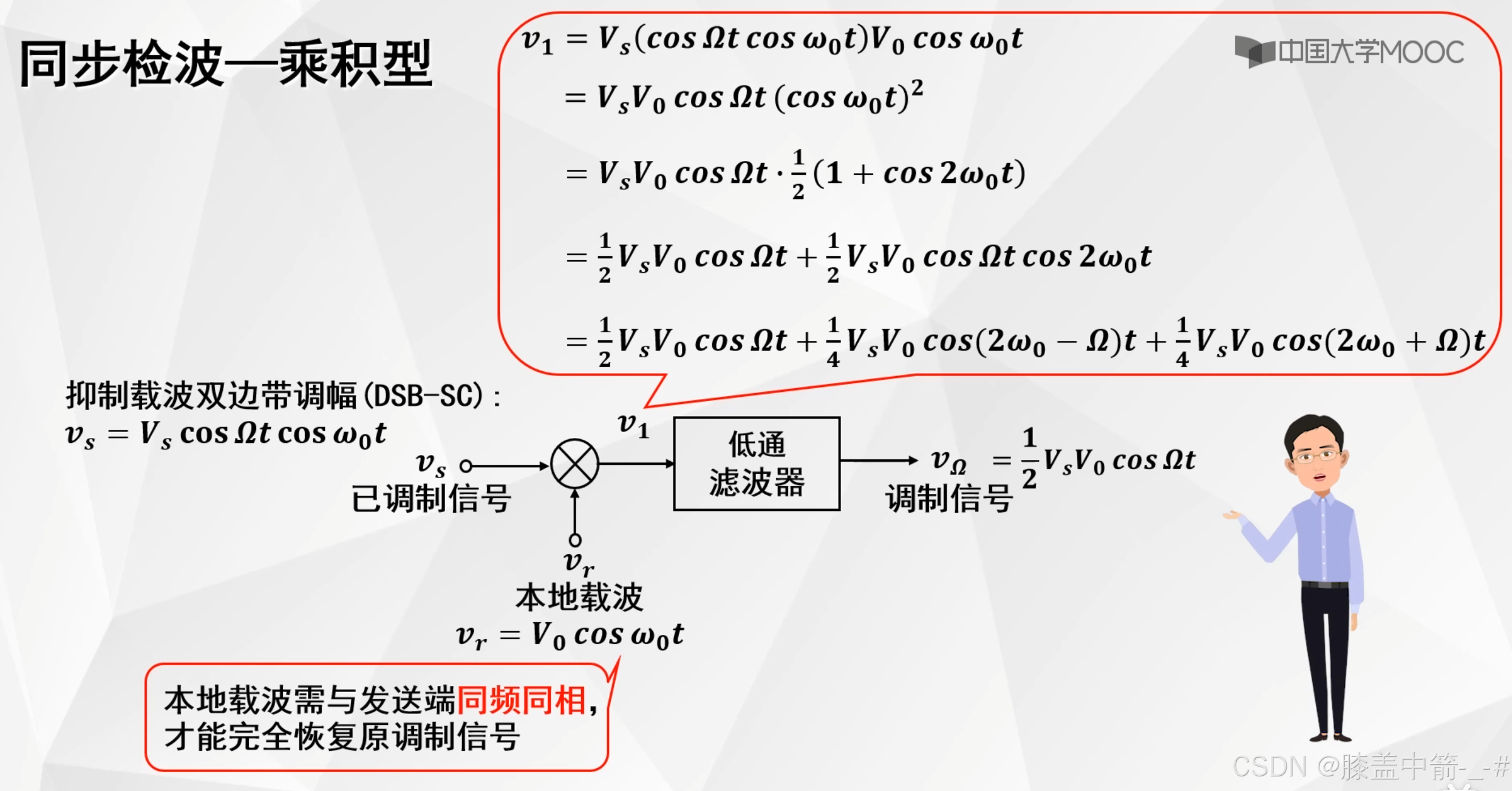

乘积型

- 输入的两个信号相乘是乘积型的,对于输入的已调制信号,是抑制载波的双边带调幅。对于此处的载波信号,由于是在接收端,常把载波叫作本地载波,根据同步同步检波的要求,本地载波需要与输入端的载波同频同相(都是cosω0)。

- 两个输入信号相乘,得到v1,再将v1的表达式用倍频公式展开,得到一部分是低频信号,一部分是高频信号,经过低通滤波器以后,高频信号滤掉,就得到了想要的调制信号。

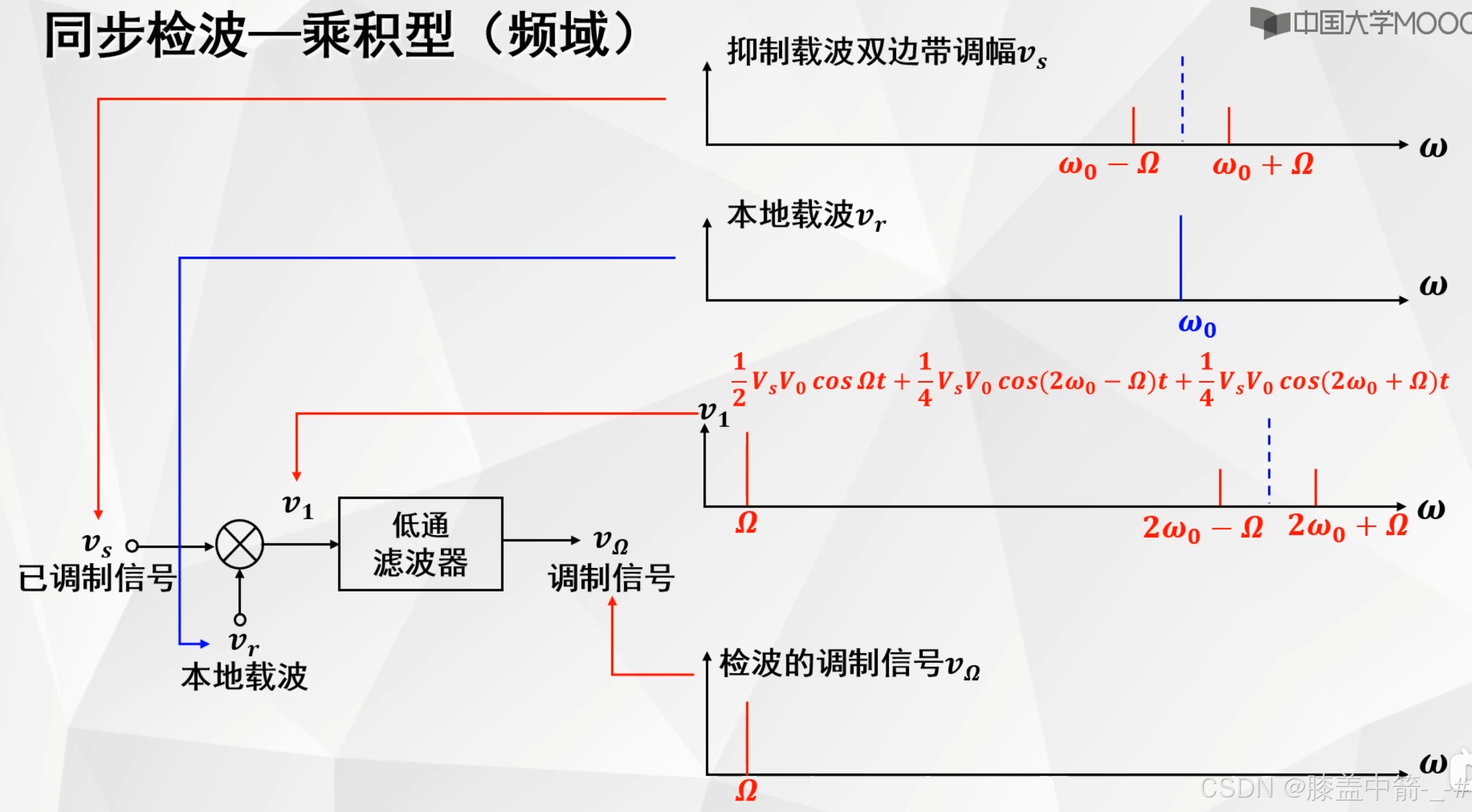

频域

- 对于输入的已调制信号,属于高频信号,去掉了载波。

- 对于本地载波,需要与发端的载波同频同相。

- 经过乘法器之后,包含三项:所需的低频调制信号,还有两个两倍的ω0加减的高频信号。

- 经过低通滤波器以后,高频的部分被滤除,得到的检波后的调制信号就是低频的调制信号。

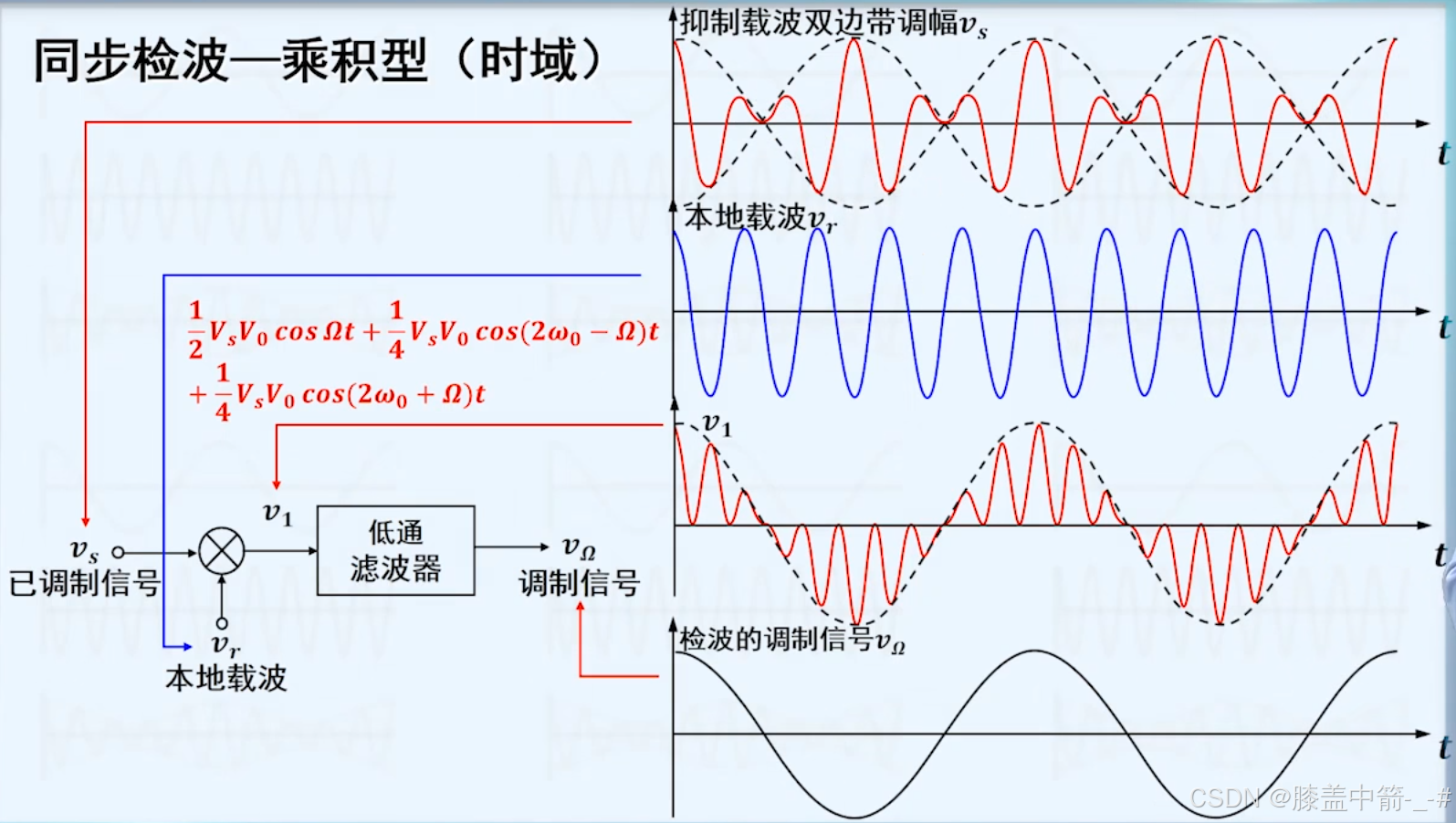

时域

- 对于输入的已调制信号的波形,抑制载波的双边带调幅,存在相位翻转。

- 对于本地载波的波形,是余弦,频率与发端的频率也是一样的。

- 经过乘法器之后的波形,时域表达式中可见,频率加倍,波形密集度大约会比载波高一倍。

- 经过低通滤波器以后,高频的部分被滤除,检波后得到的就是想要的余弦波。

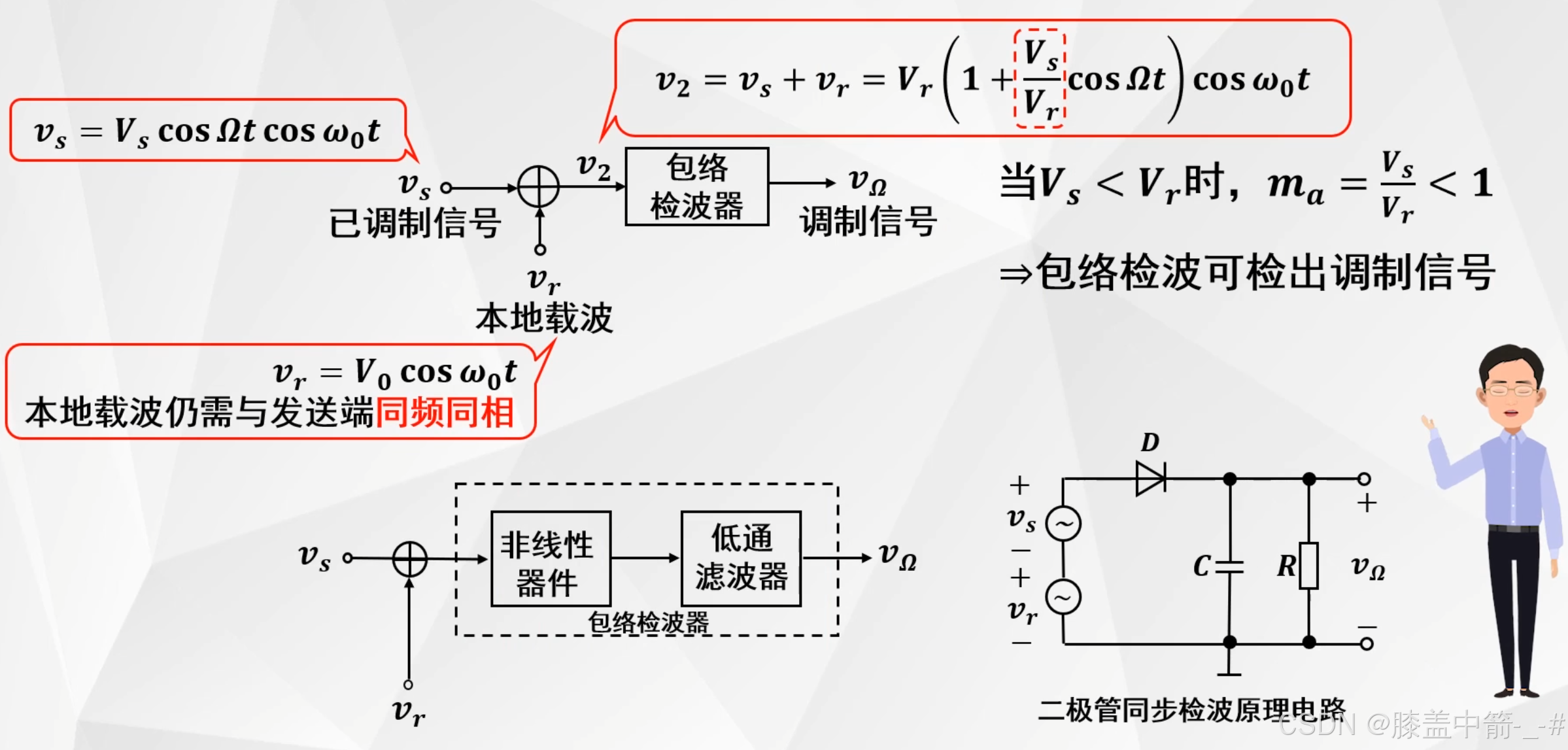

叠加型

- 叠加就是把两个输入信号通过加法器叠加到一起。一个是输入的抑制载波双边带,本地载波仍然需要与输入端同频同相。

- 表达式中可以看出,从加法器出来的信号就是普通调幅的已调制信号,普通调幅的已调制信号就可以用包络检波来进行解调,后面的就是包络检波模块(非线性器件+低通滤波器)。

- 叠加型的同步检波,实际上将同步检波转化为包络检波。虽然转化为了包络检波,但是本地载波的同频同相的要求并没有被删除。对于这种方式,不仅要求同步,而且还要避免包络检波失真的问题,因此叠加型的同步检波的容易程度和性能都都不如包络检波。

小结

对于同步检波而言,主要解决抑制载波的双边带调幅以及单边带调幅;包络检波主要针对普通调幅。而同步检波是否能针对普通调幅呢?

1717

1717

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?