文章目录

基本门电路

module BasGate(a,b,Y1,Y2,Y3,Y4,Y5,Y6);

input a,b;

output Y1,Y2,Y3,Y4,Y5,Y6;

assign Y1=a&b;

assign Y2=~(a&b);

assign Y3=a|b;

assign Y4=~(a|b);

assign Y5=a^b;

assign Y6=~a;

endmodule

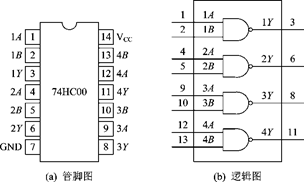

74HC00

module test_74HC00(a,b,y);

input a,b;

output y;

assign y=~(a&b);

endmodule

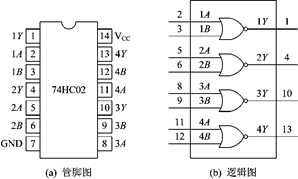

74HC02

module test_74HC02(a,b,y4);

input a,b;

output y4;

assign y4=~(a|b);

endmodule

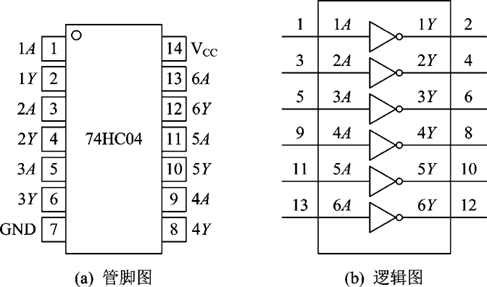

74HC04

module test_74HC04(a,b,y);

input a,b;

output y;

assign y=~(a);

endmodule

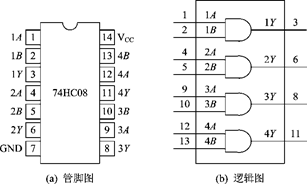

74HC08

module test_74HC08(a,b,y);

input a,b;

output y;

assign y=a&b;

endmodule

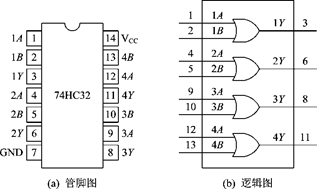

74HC32

module test_74HC32(a,b,y);

input a,b;

output y;

assign y=a|b;

endmodule

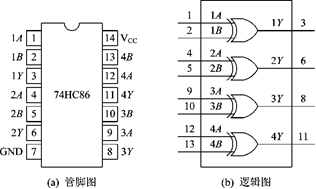

74HC86

module test_74HC86(a,b,y);

input a,b;

output y;

assign y=a^b;

endmodule

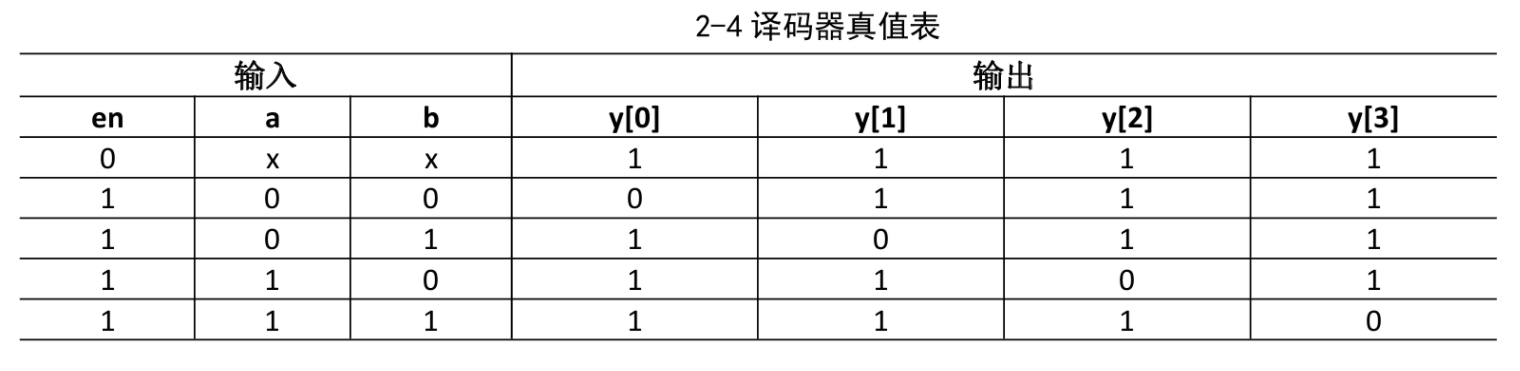

2-4译码器电路

module dec2x4(a,b,en,y);

input a,b,en;

output reg[3:0]y;

reg af,bf;

always @(a,b,en)

begin

af=~a;

bf=~b;

y[0]<=~(en&af&bf);

y[1]<=~(en&af&b);

y[2]<=~(en&a&bf);

y[3]<=~(en&a&b);

end

endmodule

4位原码~补码转换器

module ori_c(A,Y);

input [3:0]A;

output reg [3:0]Y;

always @*

begin

if(A[3])

Y=4'b1111-A[2:0]+1;

else

Y=A;

end

endmodule

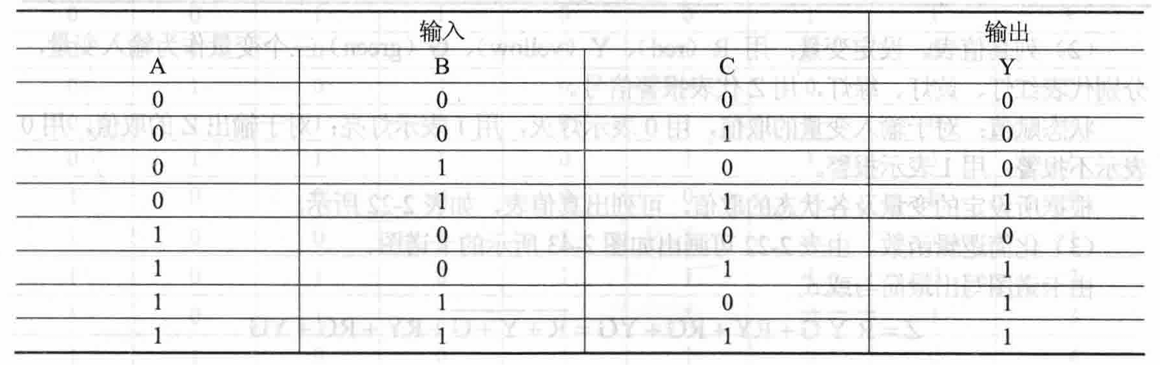

裁判表决电路

module cp(A,B,C,Y);

input A,B,C;

output reg Y;

always @ *

begin

case({A,B,C})

0:Y=0;

1:Y=0;

2:Y=0;

3:Y=1;

4:Y=0;

5:Y=1;

6:Y=1;

7:Y=1;

default:Y=1'bx;

endcase

end

endmodule

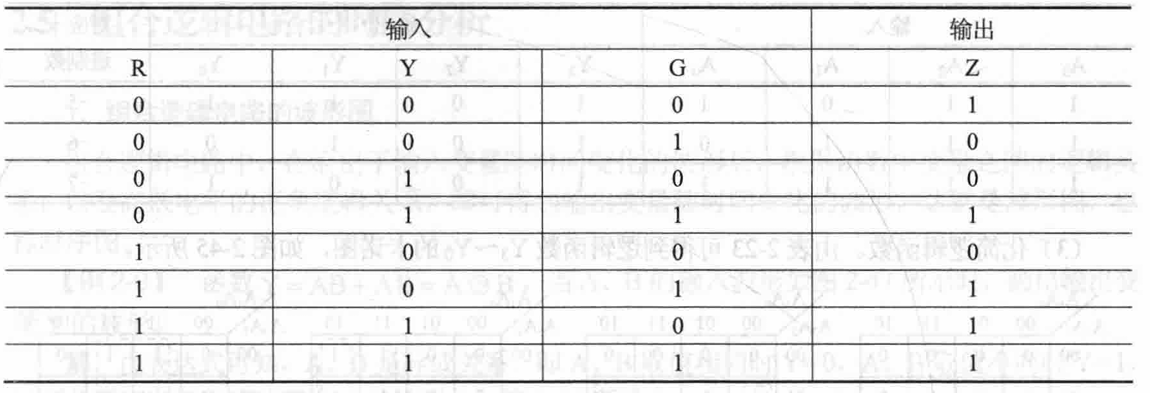

交通灯故障检测电路

module transport(r,y,g,z);

input r,y,g;

output reg z;

always @(r or y or g)

begin

case({r,y,g})

3'b000:z=1;

3'b001:z=0;

3'b010:z=0;

3'b011:z=1;

3'b100:z=0;

3'b101:z=1;

3'b110:z=1;

3'b111:z=1;

default:z=1'bx;

endcase

end

endmodule

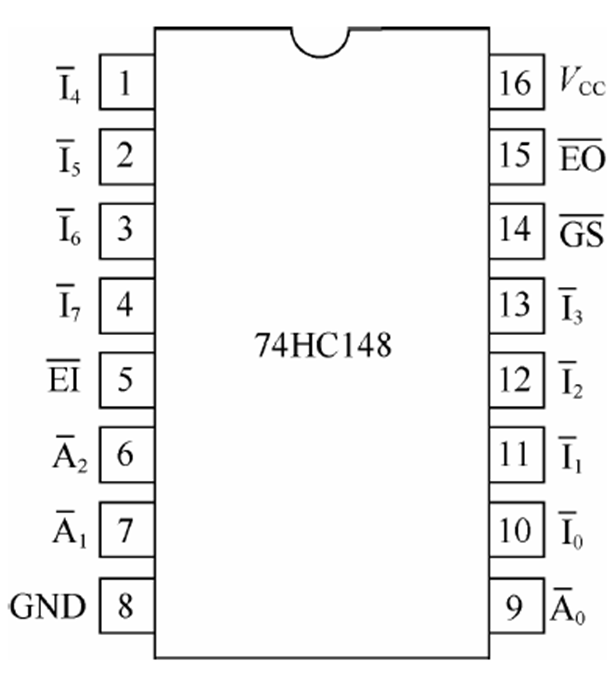

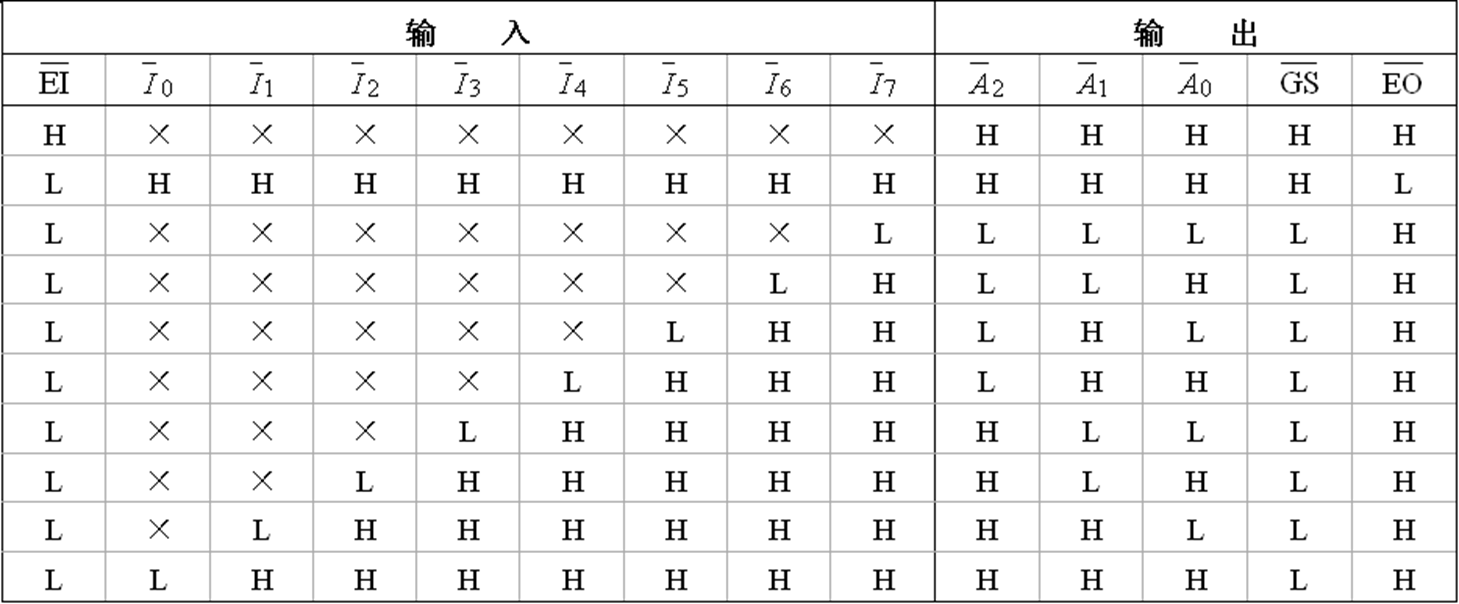

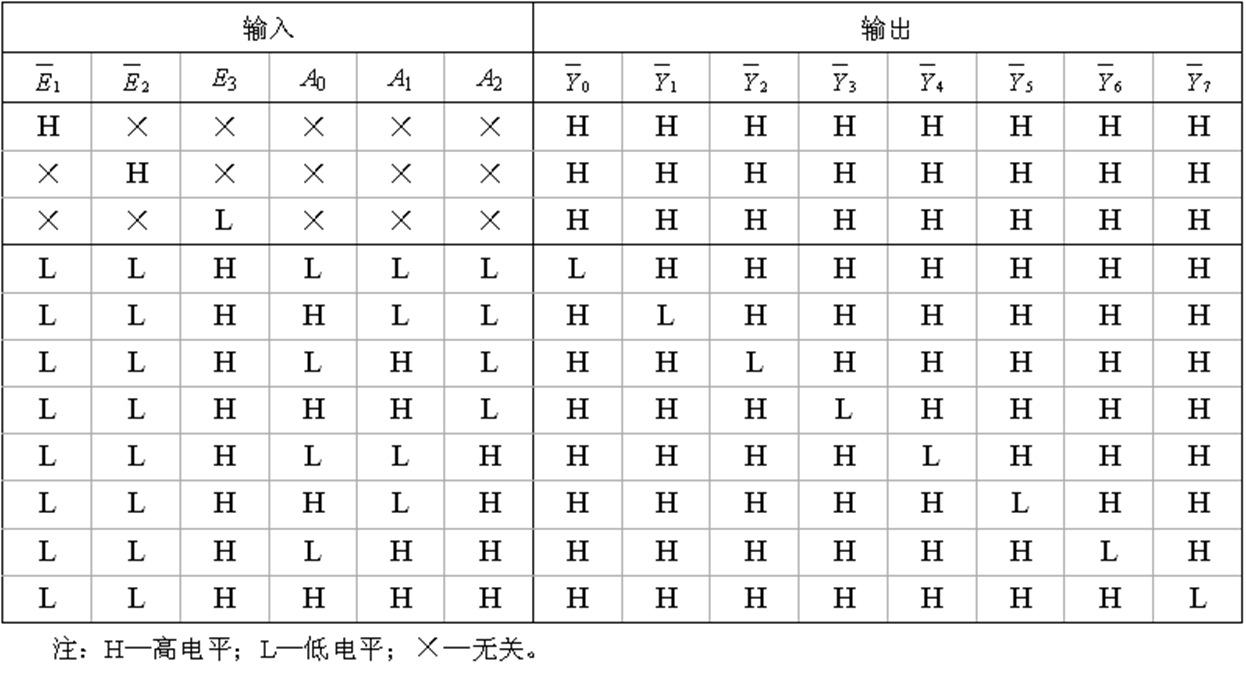

74HC148

module test_74HC148(datain,EI,dataout,EO,GS);

input [7:0]datain;

input EI;

output [2:0]dataout;

output EO,GS;

reg [2:0]dataout;

reg EO,GS;

integer I;

always @(EI or datain)

begin

if(EI)begin dataout=7;GS=1;EO=1;end

else if(datain==8'b11111111)

begin dataout=7;GS=1;EO=0; end

else

begin

for(I=0;I<8;I=I+1)

begin

if(~datain[I])begin dataout=~I;GS=0;EO=1; end

end

end

end

endmodule

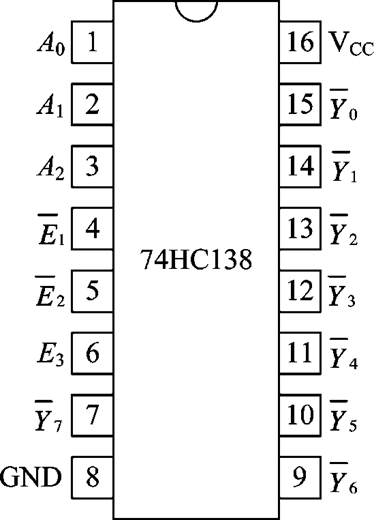

74HC138

module test_74HC138(E1N,E2N,E3,A,Y);

input E1N,E2N,E3;

input [2:0]A;

output reg [7:0]Y;

integer k;

always @(E1N or E2N or E3 or A)

begin

if(E1N==1)Y=8'b11111111;

else if(E2N==1)Y=8'b11111111;

else if(E3==0)Y=8'b11111111;

else if(E1N==0&&E2N==0&&E3==1)

for(k=0;k<8;k=k+1)

begin

if(A==k)Y[k]=0;

else Y[k]=1;

end

end

endmodule

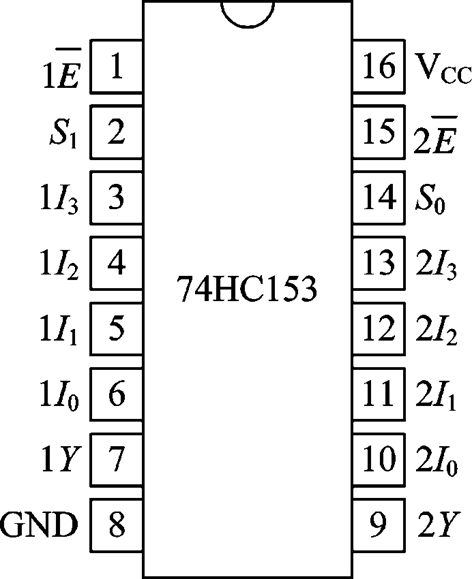

74HC153

module test_74HC153(E,S,I,Y);

input E;

input [1:0]S;

input [0:3]I;

output reg Y;

always @(E or S or I)

begin

if(E)Y=0;

else

case(S)

2'b00:Y=I[0];

2'b01:Y=I[1];

2'b10:Y=I[2];

2'b11:Y=I[3];

default:Y=1'bx;

endcase

end

endmodule

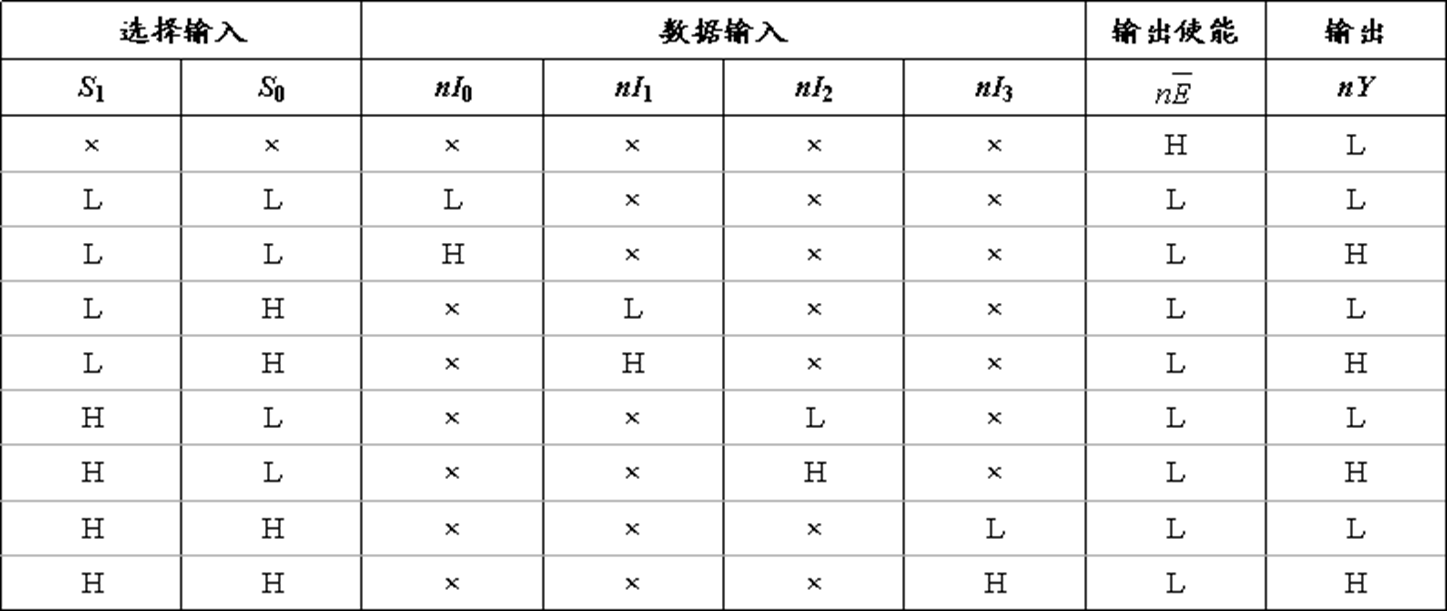

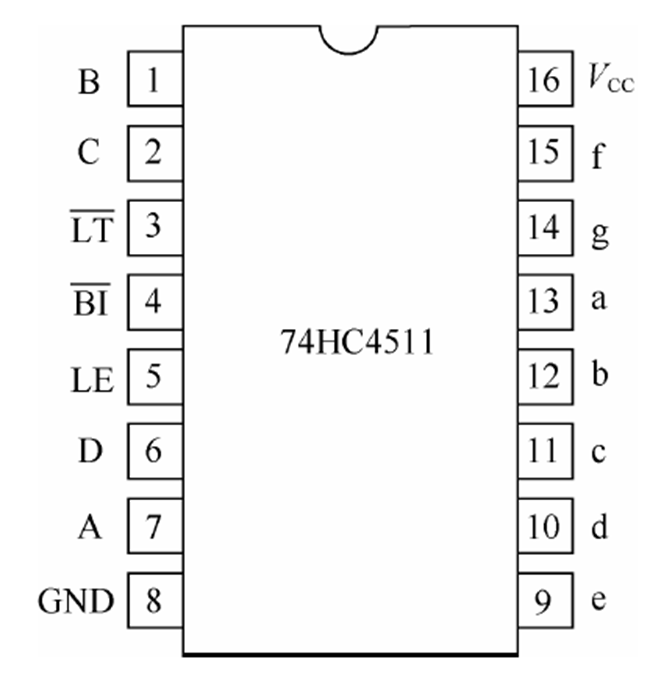

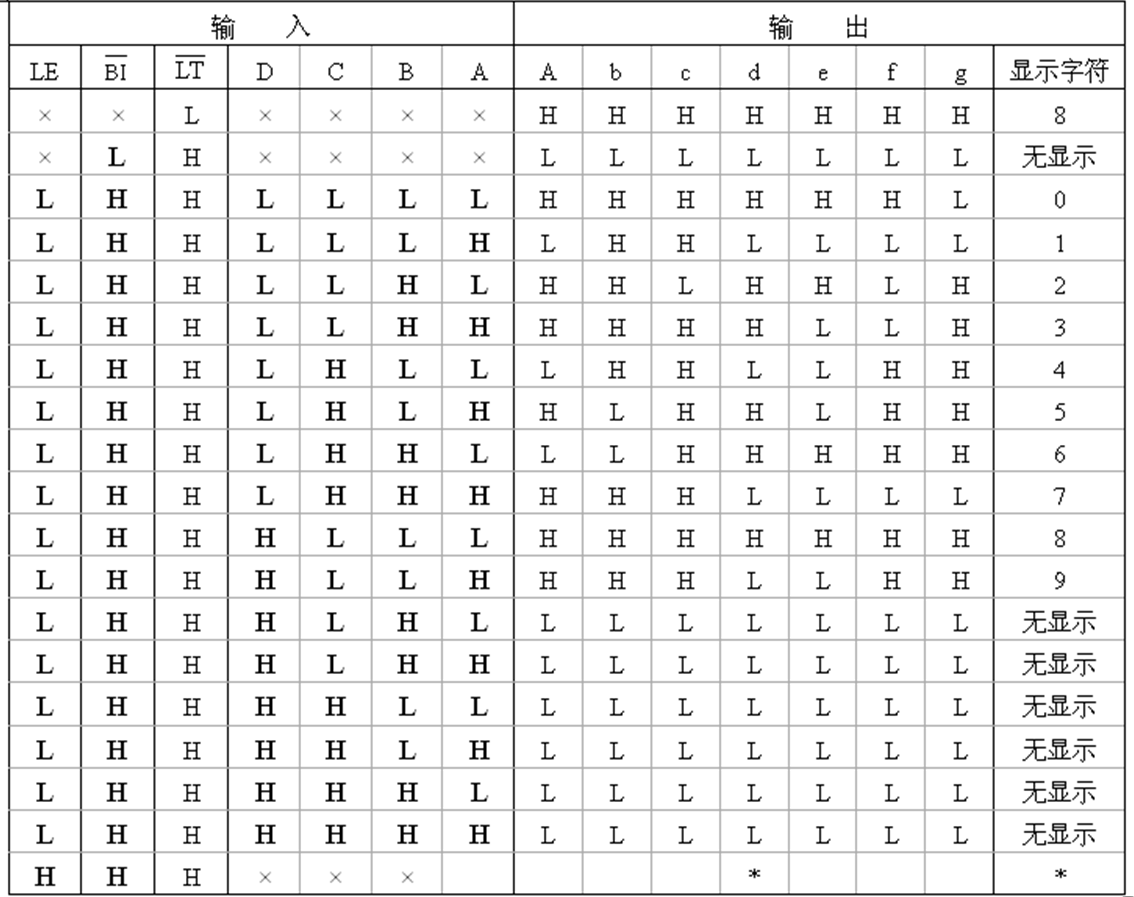

74HC4511

普通74HC4511

普通74HC4511仅支持显示0-9

module normal_74HC4511(LE,BI,LT,D,Y);

input LE,BI,LT;

input [3:0]D;

output reg [6:0]Y;

always @(LT or BI or LE or D)

if(!LT)Y=7'b1111111;

else if(!BI)Y=0;

else if(!LE)

case(D)

0:Y=7'B1111110;

1:Y=7'B0110000;

2:Y=7'B1101101;

3:Y=7'B1111001;

4:Y=7'B0110011;

5:Y=7'B1011011;

6:Y=7'B1011111;

7:Y=7'B1110000;

8:Y=7'B1111111;

9:Y=7'B1111011;

default:Y=7'b0000000;

endcase

endmodule

拓展型74HC4511

扩展型74HC4511可以支持显示0-F以及小数点

module expand_74HC4511(A,Seg,LT_N,BI_N,LE);

input LT_N, BI_N, LE;

input[3:0] A;

output[7:0] Seg;

reg [7:0] SM_8S;

assign Seg=SM_8S;

always @(A or LT_N or BI_N or LE)

begin

if(!LT_N) SM_8S=8'b11111111;

else if(!BI_N) SM_8S=8'b00000000;

else if(LE) SM_8S=SM_8S;

else

case(A)

4'd0:SM_8S=8'b00111111; // 3f(00111111 对应的十六进制数),方便结果查看

// 按“小数点-g-f-e-d-c-b-a”顺序,最高位0表示小数点不显示。

4'd1:SM_8S=8'b00000110;

4'd2:SM_8S=8'b01011011;

4'd3:SM_8S=8'b01001111;

4'd4:SM_8S=8'b01100110;

4'd5:SM_8S=8'b01101101;

4'd6:SM_8S=8'b01111101;

4'd7:SM_8S=8'b00000111;

4'd8:SM_8S=8'b01111111;

4'd9:SM_8S=8'b01101111;

4'd10:SM_8S=8'b01110111;

4'd11:SM_8S=8'b01111100;

4'd12:SM_8S=8'b00111001;

4'd13:SM_8S=8'b01011110;

4'd14:SM_8S=8'b01111001;

4'd15:SM_8S=8'b01110001;

default:;

endcase

end

endmodule

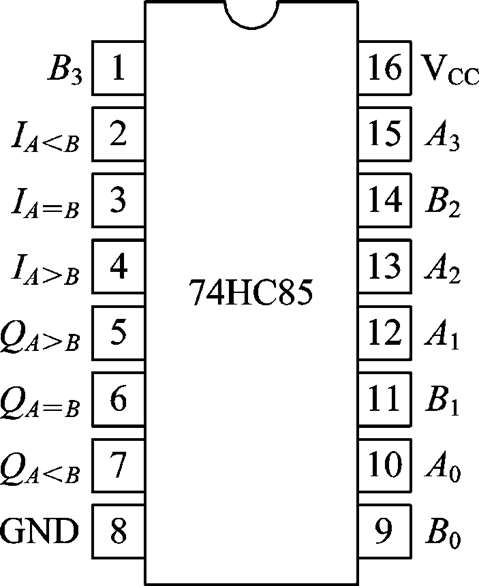

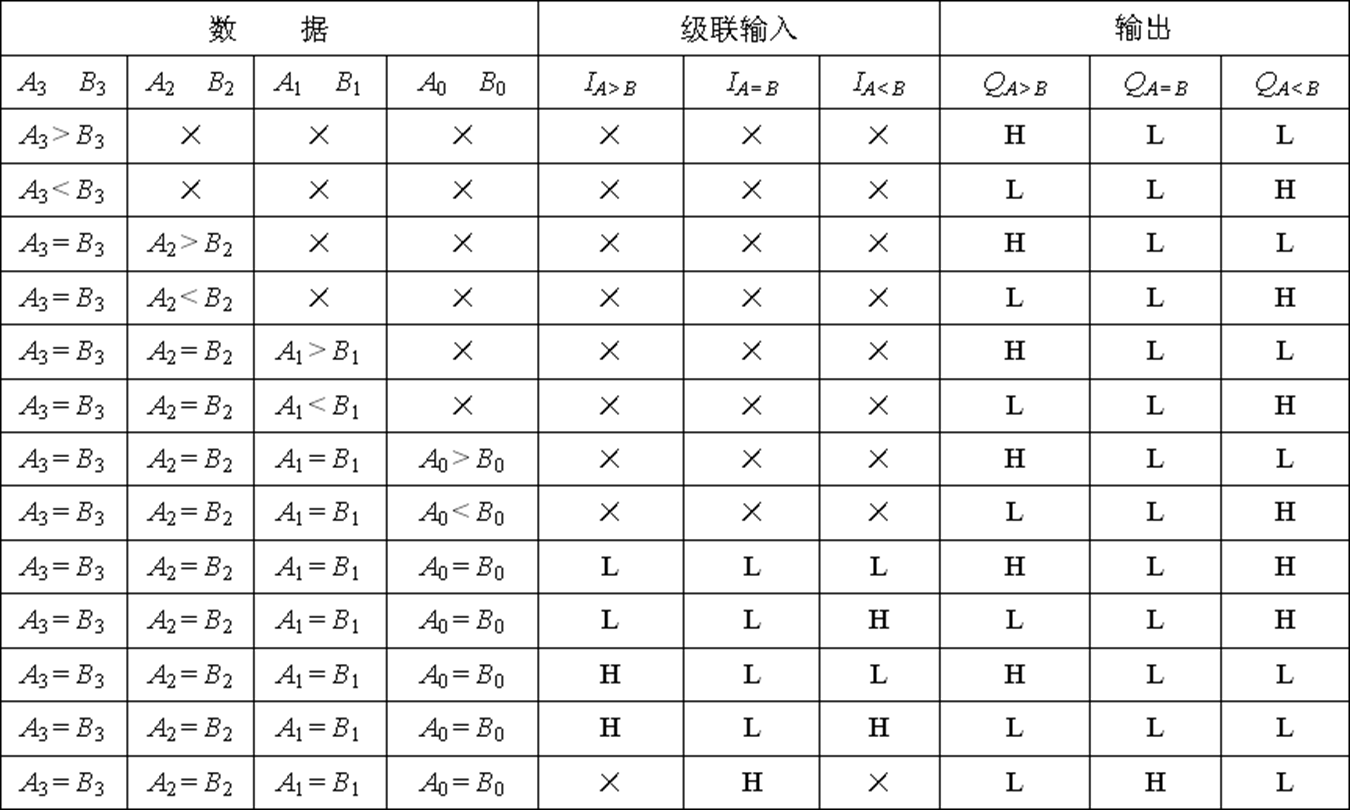

74HC85

module test_74HC85(A,B,I,Q);

input [3:0]A;

input [3:0]B;

input [2:0]I;

output reg [2:0]Q;

always @*

if(A>B)Q=3'b100;

else if(A<B)Q=3'b001;

else

case(I)

3'b000:Q=3'b101;

3'b001:Q=3'b001;

3'b100:Q=3'b100;

3'b101:Q=3'b000;

3'bx1x:Q=3'b010;

default:Q=1'bx;

endcase

endmodule

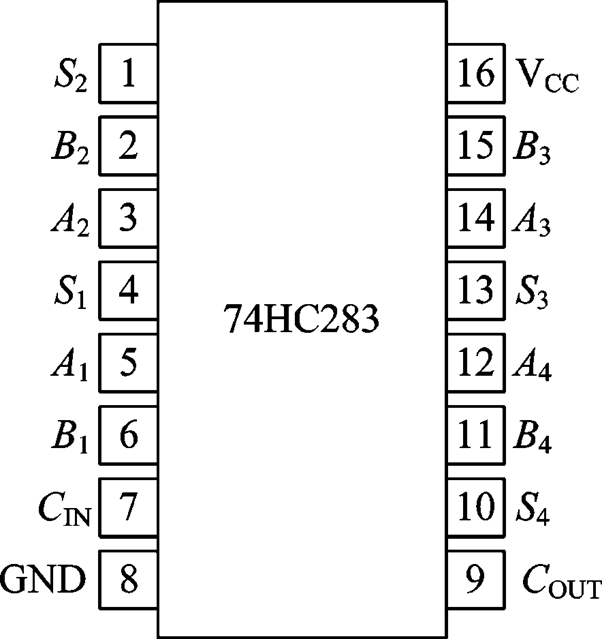

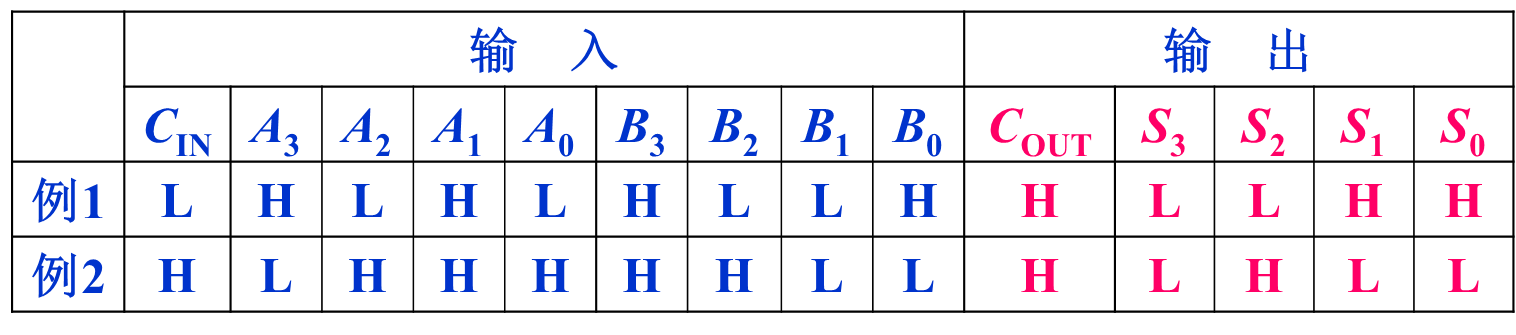

74HC283

module test_74HC283(Cin,A,B,Cout,S);

input Cin;

input [3:0]A,B;

output reg Cout;

output reg [3:0]S;

always @(Cin or A or B)

begin

{Cout,S}=A+B+Cin;

end

endmodule

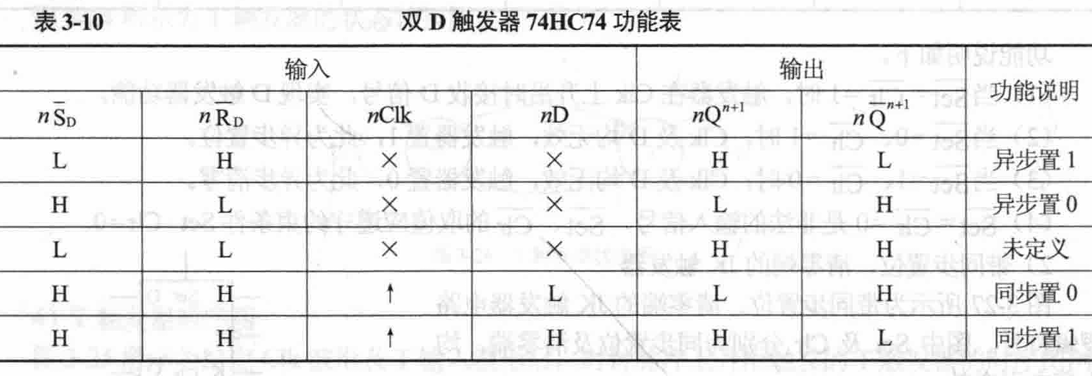

74HC74

module test_74HC74(sd,rd,clk,D,Q,Q_n);

input sd,rd,clk,D;

output reg Q,Q_n;

always @(posedge clk or negedge sd or negedge rd)

case({sd,rd})

0:begin Q=1;Q_n=1; end

1:begin Q=1;Q_n=0; end

2:begin Q=0;Q_n=1; end

3:begin Q=D;Q_n=~D; end

default:begin Q=1'b1;Q_n=1'b1; end

endcase

endmodule

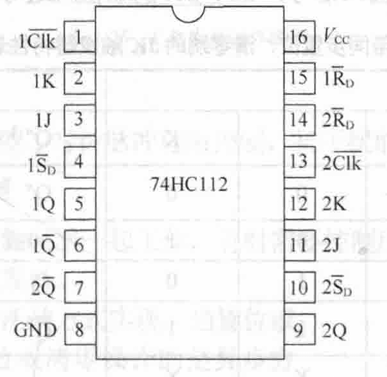

74HC112

module test_74HC112(sd,rd,clk,J,K,Q,Q_n);

input sd,rd,clk,J,K;

output reg Q;

output Q_n;

always @(negedge sd or negedge rd or negedge clk)

case({sd,rd})

0:Q<=1;

1:Q<=1;

2:Q<=0;

3:

case({J,K})

0:Q<=Q;

1:Q<=0;

2:Q<=1;

3:Q<=~Q;

default:Q<=1'bx;

endcase

default:Q<=1'bx;

endcase

assign Q_n=~Q;

endmodule

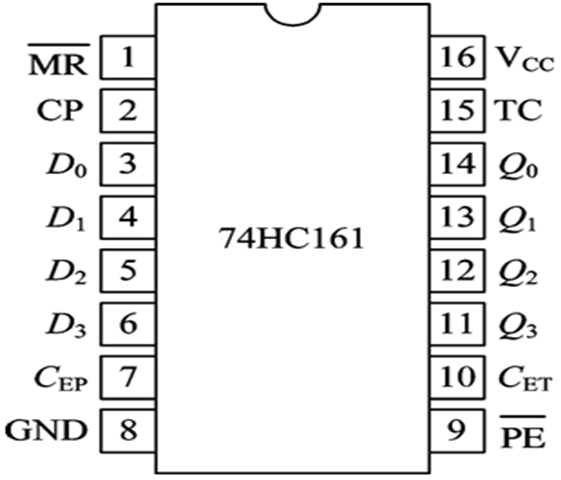

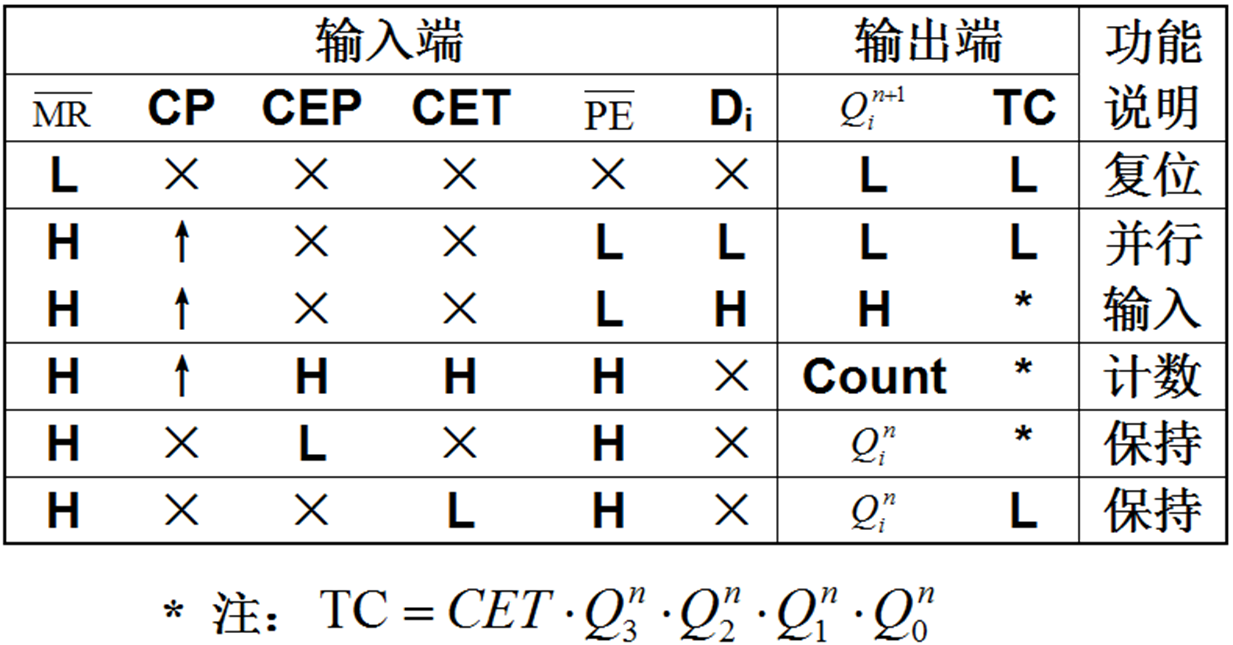

74HC161

module test_74HC161(Q,TC,MR,CP,CEP,CET,PE,D);

input MR,CP,CEP,CET,PE;

input [3:0]D;

output [3:0]Q;

output TC;

reg [3:0]Q;

always @(negedge MR,posedge CP)

if(!MR)

Q=0;

else if(CEP &CET & PE)

Q=Q+1;

else if(!PE)

Q=D;

assign TC=&{CET,Q};

endmodule

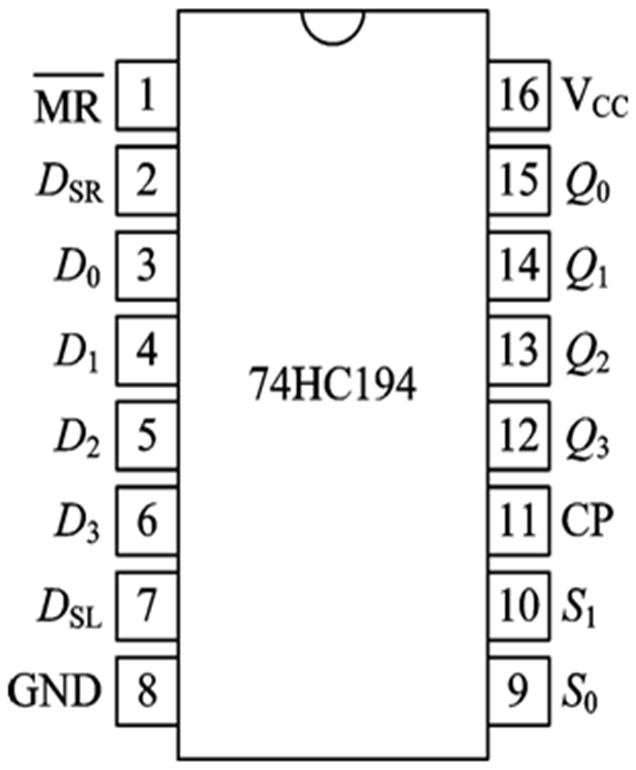

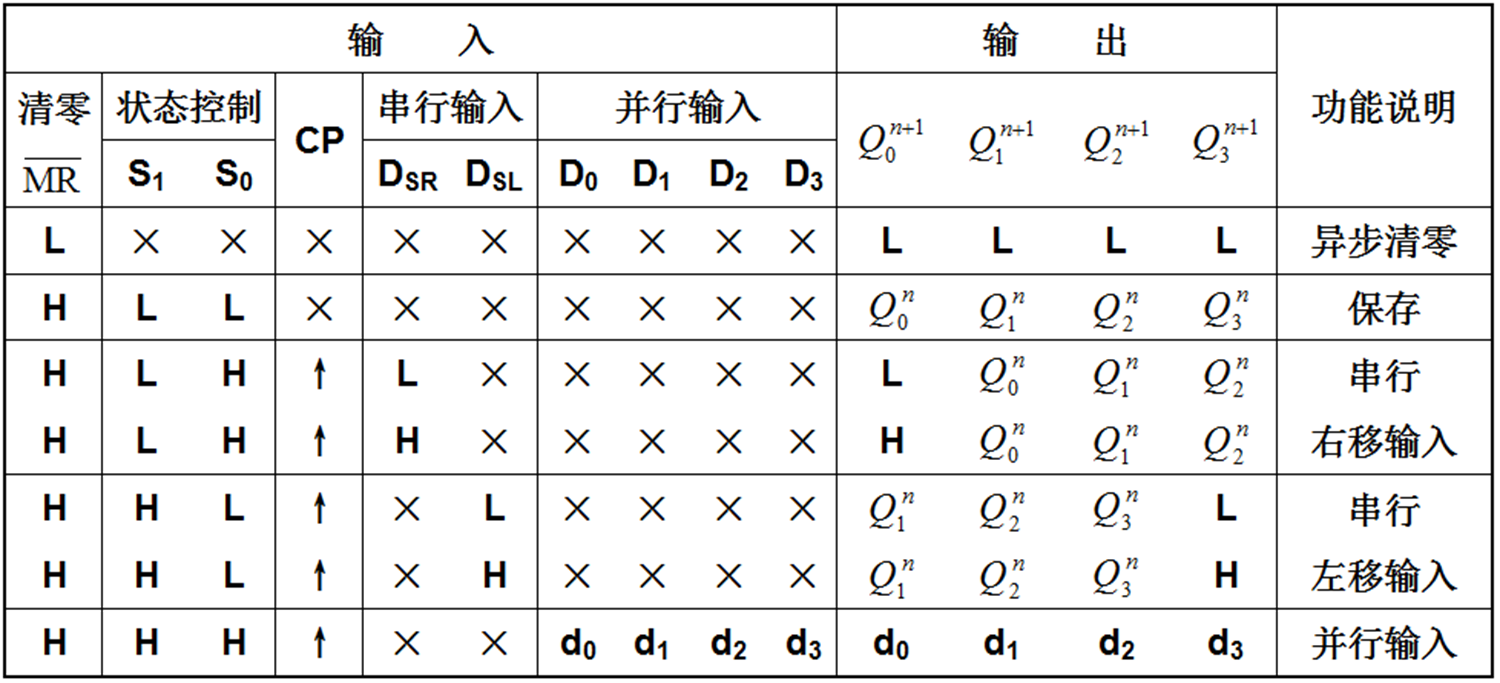

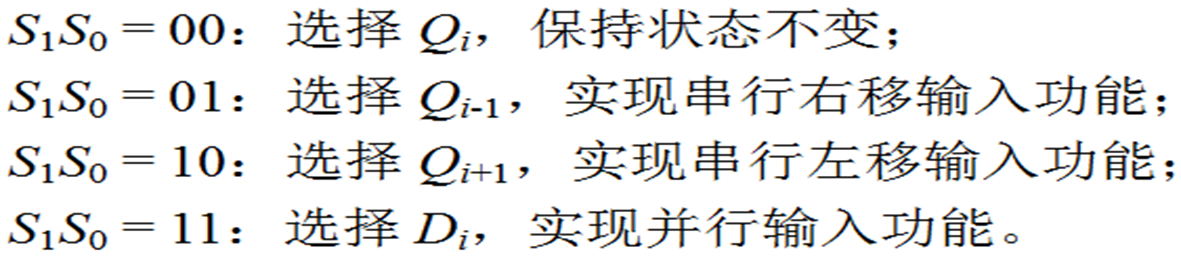

74HC194

module test_74HC194(MR,S,CP,DSR,DSL,D,Q);

input MR,DSR,DSL,CP;

input [1:0]S;

input [0:3]D;

output reg [0:3]Q;

always @(negedge MR or posedge CP)

if(!MR)Q<=4'b0000;

else if(S==2'b00)Q<=Q;

else if(S==2'b01)Q<={DSR,Q[0],Q[1],Q[2]};

else if(S==2'b10)Q<={Q[1],Q[2],Q[3],DSL};

else if(S==2'b11)Q<=D;

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?