目录

一、实验内容

a) 介绍

在这次实验中,你将熟悉 Logisim 的操作流程,并且学习如何通过画图的方法 设计出计算机当中的核心运算器件——ALU。 然后,我们将使用七段数码管进一 步地人性化地显示出 ALU 的计算结果。

b) 全加器设计

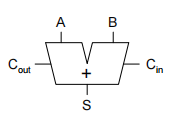

一个全加器具有三个输入(A, B, Cin)和两个输出(S, Cout)。如下图所示,输入 A 和 B 各代表一个 1 比特二进制数,输出 S 表示 A 和 B 之和:

Cin (进位输入) and Cout (进位输出)信号用于输入和输出多于一个比特的情况

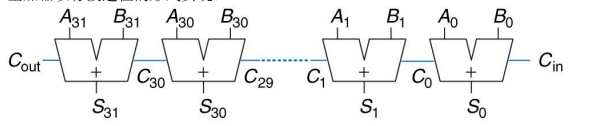

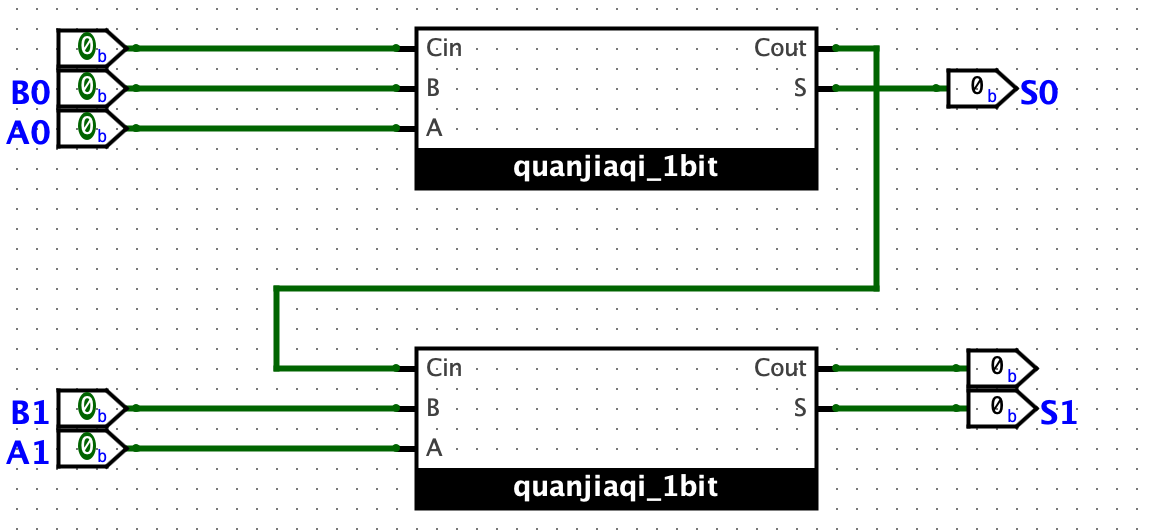

c)设计一个 2 比特加法器

一个全加器只能够实现 1 比特的运算。要实现 N 比特的加法,可以采用多个全加器以行波进位的形式实现

二、实验步骤

2.1 全加器的设计

(1)真值表:

| Inputs | Outputs | |||

| Cin | B | A | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

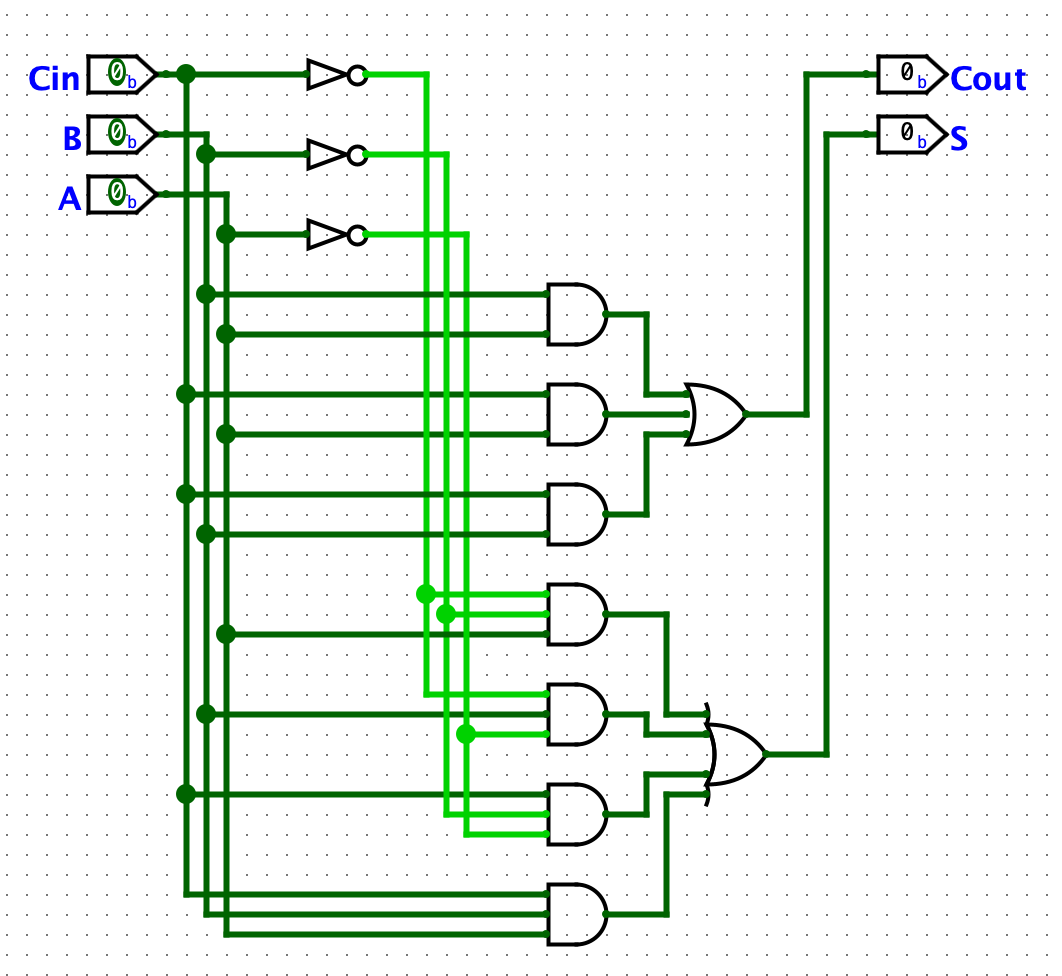

(2)电路原理图

图1 全加器的电路原理图

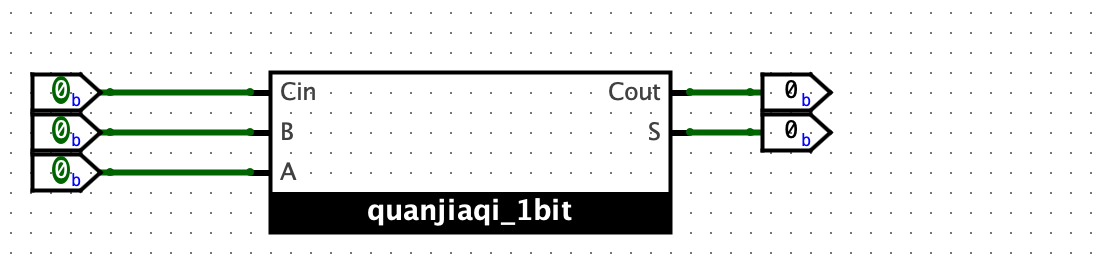

图2 全加器的封装电路图

(3)步骤

①使用逻辑门等电子器件实现全加器的逻辑方程,推断出全加器的实验表达式:

Cout=B*A+Cin*A+Cin*B

S=(not)Cin*(not)B*A+(not)Cin*B*(not)A+Cin*(not)A*(not)B+Cin*B*A

②设置全加器电路输入位为A、B、Cin,输出位为S和Cout,S为和位,Cout为进位位

③将A、B、Cin分别连接到或门和与门的输入端,输出端为S、Cout

④经过结果运算,得到S,Cout

2.2 加法器的设计

(1)真值表

| A1 | A0 | B1 | B0 | S1 | S0 | 溢出情况 |

| 0 | 0 | 0 | 0 | 0 | 0 | 无 |

| 0 | 0 | 0 | 1 | 0 | 1 | 无 |

| 0 | 0 | 1 | 0 | 1 | 0 | 无 |

| 0 | 0 | 1 | 1 | 1 | 1 | 无 |

| 0 | 1 | 0 | 0 | 0 | 1 | 无 |

| 0 | 1 | 0 | 1 | 1 | 0 | 无 |

| 0 | 1 | 1 | 0 | 1 | 1 | 无 |

| 0 | 1 | 1 | 1 | 0 | 0 | 有 |

| 1 | 0 | 0 | 0 | 1 | 0 | 无 |

| 1 | 0 | 0 | 1 | 1 | 1 | 无 |

| 1 | 0 | 1 | 0 | 0 | 0 | 有 |

| 1 | 0 | 1 | 1 | 0 | 1 | 有 |

| 1 | 1 | 0 | 0 | 1 | 1 | 无 |

| 1 | 1 | 0 | 1 | 0 | 0 | 有 |

| 1 | 1 | 1 | 0 | 0 | 1 | 有 |

| 1 | 1 | 1 | 1 | 1 | 0 | 有 |

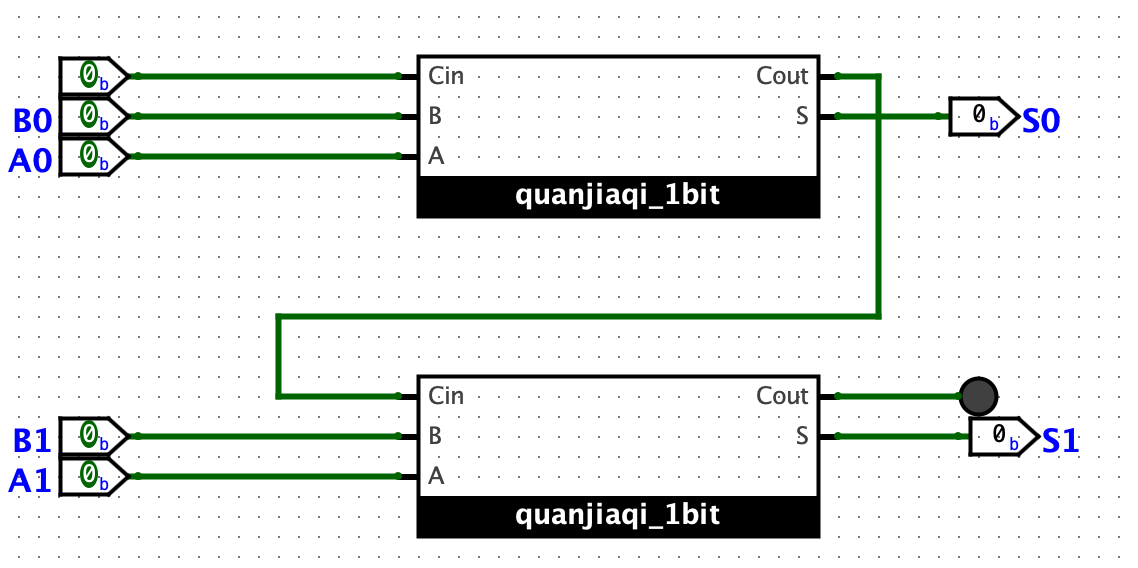

(2)电路原理图

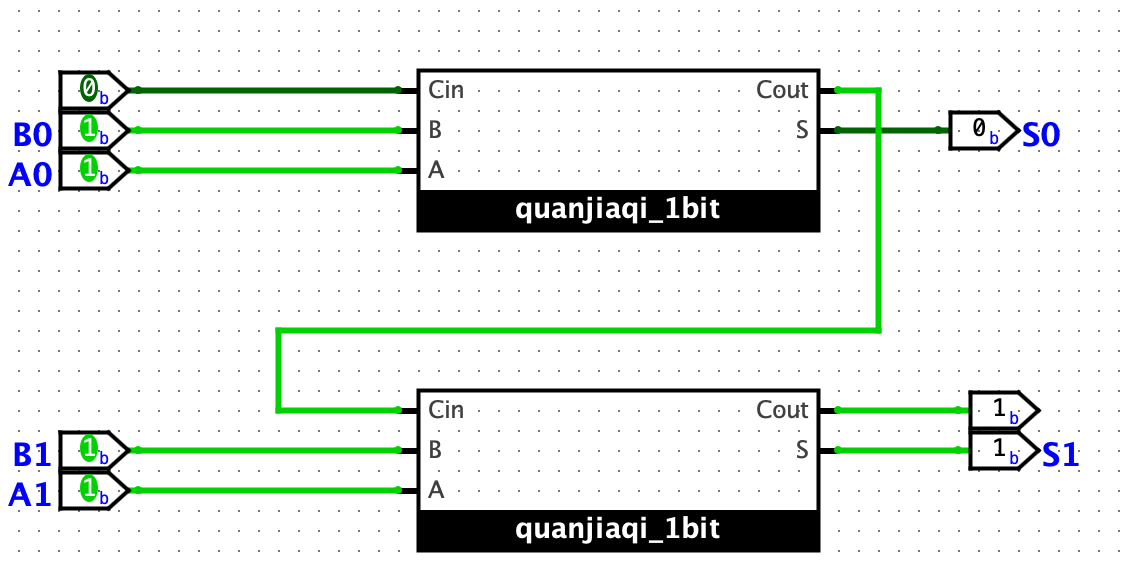

图3 加法器封装电路图

(3)步骤

①用上面方法创建一比特全加器。

②将两个一比特全加器级联起来,第一个全加器的输出进位连接到第二个全加器的输入进位,从而实现两个二进制数的相加。

③逻辑表达式:

S0 = ~Cin⋅~B0⋅A0+~Cin⋅B0⋅~A0+Cin⋅~B0⋅~A0+Cin⋅B0⋅A0

Cout = B1⋅A1+B0⋅A0⋅A1+B0⋅A0⋅B1+Cin⋅A0⋅A1+Cin⋅A0⋅B1+Cin⋅B0⋅A1+Cin⋅B0⋅B1

S1 = ~Cin⋅~B0⋅~B1⋅A1+~Cin⋅~B0⋅B1⋅~A1+~Cin⋅~A0⋅~B1⋅A1+~Cin⋅~A0⋅B1⋅~A1+B0⋅A0⋅~B1⋅~A1+B0⋅A0⋅B1⋅A1+~B0⋅~A0⋅~B1⋅A1+~B0⋅~A0⋅B1⋅~A1+Cin⋅A0⋅~B1⋅~A1+Cin⋅A0⋅B1⋅A1+Cin⋅B0⋅~B1⋅~A1+Cin⋅B0⋅B1⋅A1

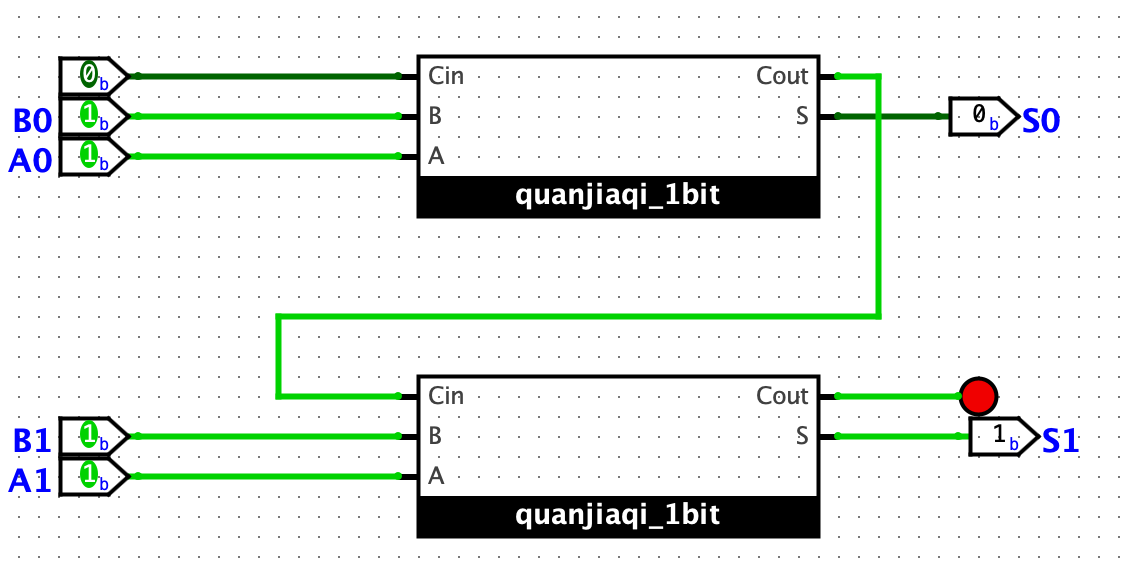

④判断溢出:插入LED灯判断是否溢出(若LED亮灯则溢出,否则无溢出)

图4 判断是否溢出

三、调试过程

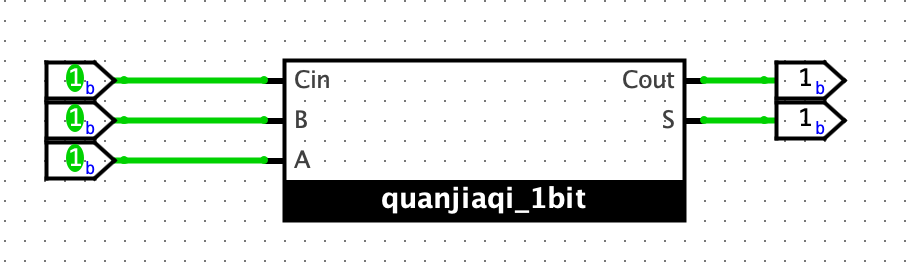

3.1 全加器调试过程

eg.1

图5 Cin=1 B=1 C=1得Cout=1,S=1

使用表达式进行检验:Cout=B·A+Cin·A+Cin·B=1*1+1*1+1*1=3

S=~Cin·~B*A+~Cin·B·~A+Cin·~A·~B+Cin·B·A=0+0+0+1=1

经检验结果,设计成立

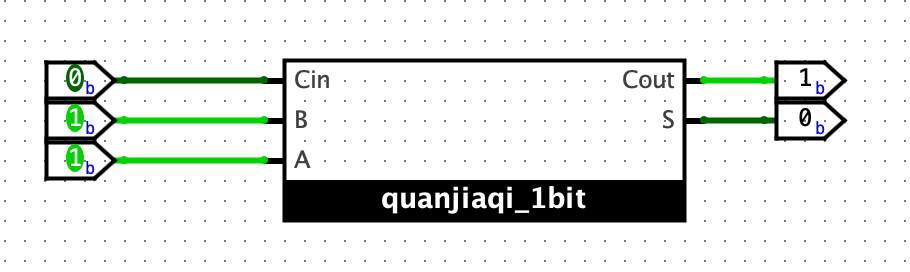

eg 2:

图6 Cin=0 B=1 A=1 得Cout=1,S=0

使用表达式进行检验:Cout=B*A+Cin*A+Cin*B=1+0+0=1

S=(not)Cin*(not)B*A+(not)Cin*B*(not)A+Cin*(not)A*(not)B+Cin*B*A=0+0+0+0=0

2.加法器的调试过程

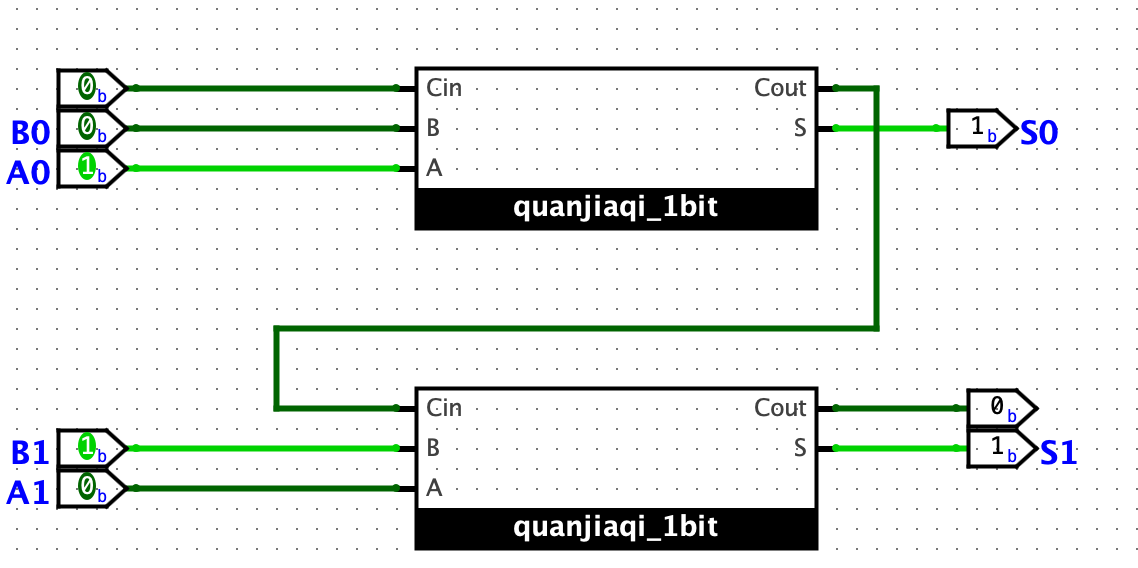

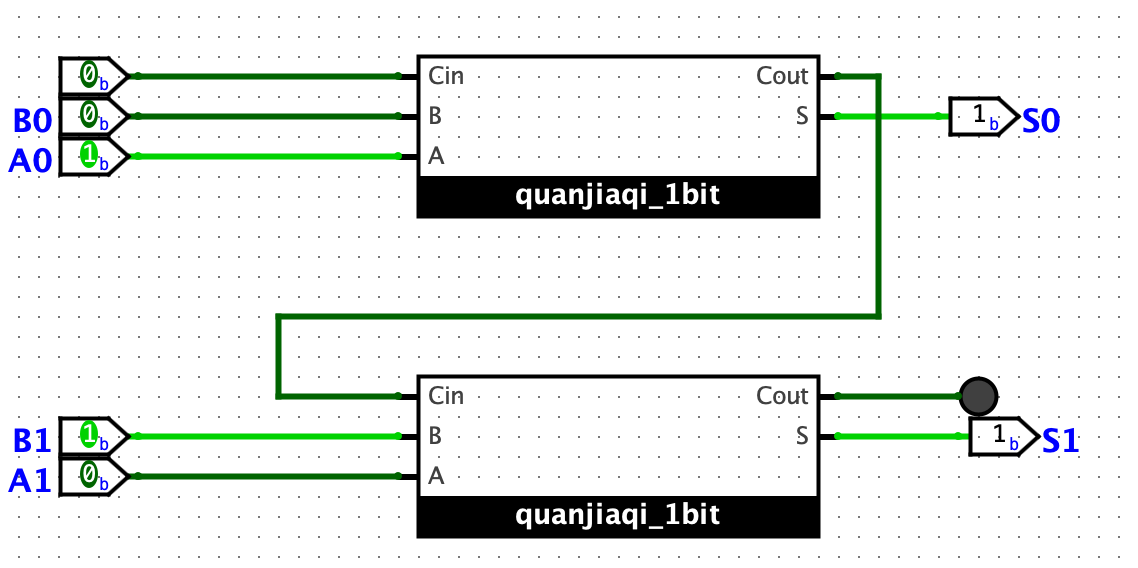

图7 A0=1、B0=0、B1=1、A1=0得S0=1、Cout=0、S1=1

进行检验:LED灯不亮 A1A0+B1B0=01+10=11 S1=1 S0=1 无溢出

图9 A0=1、B0=1、B1=1、A1=1得S0=0、Cout=1、S1=1

进行检验:LED灯发亮 A1A0+B1B0=11+11=6 S1S0=10=2 有溢出

有溢出的真值表:

| A1 | A0 | B1 | B0 | S1 | S0 | 溢出情况 |

| 0 | 1 | 1 | 1 | 0 | 0 | 有 |

| 1 | 0 | 1 | 0 | 0 | 0 | 有 |

| 1 | 0 | 1 | 1 | 0 | 1 | 有 |

| 1 | 1 | 0 | 1 | 0 | 0 | 有 |

| 1 | 1 | 1 | 0 | 0 | 1 | 有 |

| 1 | 1 | 1 | 1 | 1 | 0 | 有 |

四、实验使用环境

本实验采用 Logisim 电路仿真平台。在使用 Logisim 设计本实验要求的数字电路的时候,

必须使用基本的逻辑门完成设计,而不允许使用 Logisim 提供的运算器(如封装好的加法

器、复用器或带译码器的七段数码管)

五、实验小结和思考

1. 遇到的问题

-

二进制表示混淆:起初不清楚如何区分高低位,导致2bit补码范围理解错误(实际范围:-2到1)。

-

减法器设计困惑:不确定1bit减法是否可行(实际可通过补码实现:A - B = A + (~B + 1))。

2. 解决过程

-

确定高低位定义和补码范围,明确2bit补码最小值为

10(-2),最大值为01(1)。

3. 实验收获

-

从真值表推导逻辑表达式(如

S = A⊕B⊕Cin)。 -

独立设计加法器、减法器(基于补码)和复用器电路。

- 二进制数的位权概念(低位为

2^0,高位为2^1)。 - 减法器本质是“加补码”,统一了加减法硬件设计。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?