| 课 程 设 计 说 明 书 |

|

| 课程设计名称 |

计算机组成原理课程设计 |

| 专 业 |

计算机科学与技术 |

| 班 级 |

|

| 学生姓名 |

|

| 指导教师 |

|

2022 年 6 月 13 日

|

|

|||

|

|

基于HDL的硬件部件仿真设计 |

||

| 起止日期 |

2022年 6 月13 日—2022年6 月17日 |

设计地点 |

网络 |

| 设计任务及日程安排: 设计任务: 日程安排: 本次设计共一周时间,日程安排如下: 第1-4天:完成设计任务中至少3个实验,并且自选题目至少1个,编写设计报告; 第5天:验收设计程序,答辩,提交设计报告。 |

|||

注:此任务书由指导教师在课程设计前填写,发给学生作为本门课程设计的依据。

目录

实验一 一位全加器的设计与仿真

实验目标:设计一个一位全加器模型并编写测试程序进行仿真测试。

实验要求:设计模块名称fulladd,输入端口a,b,c_in。输出端口sum,c_out。编写的测试程序要保证测试充分。

利用公式

- sum= a⊕b⊕c_in

- c_out=ab+(a⊕b)c_in

模块程序:

module full_adder(a,b,c_in,c_out,sum);

input a,b,c_in;

output c_out,sum;

wire sum,c_out;

assign {c_out,sum}=a+b+c_in;

endmodule

测试程序:

`timescale 1ns/1ns

module full_adder_tb;

reg a,b,c_in;

wire c_out,sum;

integer i,j;

parameter delay=100;

full_adder U1(a,b,c_in,c_out,sum);

initial

begin

a=0;b=0;c_in=0;

for(i=0;i<2;i=i+1)

for(j=0;j<2;j=j+1)

begin

a=i;b=j;c_in=0;

#delay;

end

for(i=0;i<2;i=i+1)

for(j=0;j<2;j=j+1)

begin

a=i;b=j;c_in=1;

#delay;

end

end

endmodule

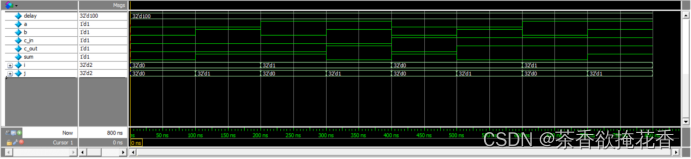

仿真波形:

分析:

实验一 一位全加器的设计与仿真 实验二 四位全加器的设计与仿真 实验三 32位浮点乘法器的设计与仿真 实验四 简单运算器的设计与仿真 实验五 一位比较器的设计与仿真 实验六 八位比较器的设计与仿真 实验七 1/2分频器的设计与仿真 实验八 二选一多路选择器的设计与仿真 实验九 四选一多路选择器的设计与仿真 实验十 3-8译码器的设计与仿真 实验十一 触发器的设计与仿真 实验十二 移位寄存器的设计与仿真 实验十三 存储器设计与仿真 实验十四 同步FIFO的设计与仿真

实验一 一位全加器的设计与仿真 实验二 四位全加器的设计与仿真 实验三 32位浮点乘法器的设计与仿真 实验四 简单运算器的设计与仿真 实验五 一位比较器的设计与仿真 实验六 八位比较器的设计与仿真 实验七 1/2分频器的设计与仿真 实验八 二选一多路选择器的设计与仿真 实验九 四选一多路选择器的设计与仿真 实验十 3-8译码器的设计与仿真 实验十一 触发器的设计与仿真 实验十二 移位寄存器的设计与仿真 实验十三 存储器设计与仿真 实验十四 同步FIFO的设计与仿真

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1197

1197

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?