上回书已经将组合逻辑电路的部分都简单的说完了,组合逻辑电路中的元器件是无记忆功能的,那么有记忆存储功能的器件是什么呢?具有存储功能的逻辑单元电路有两个典型的代表——锁存器和触发器。

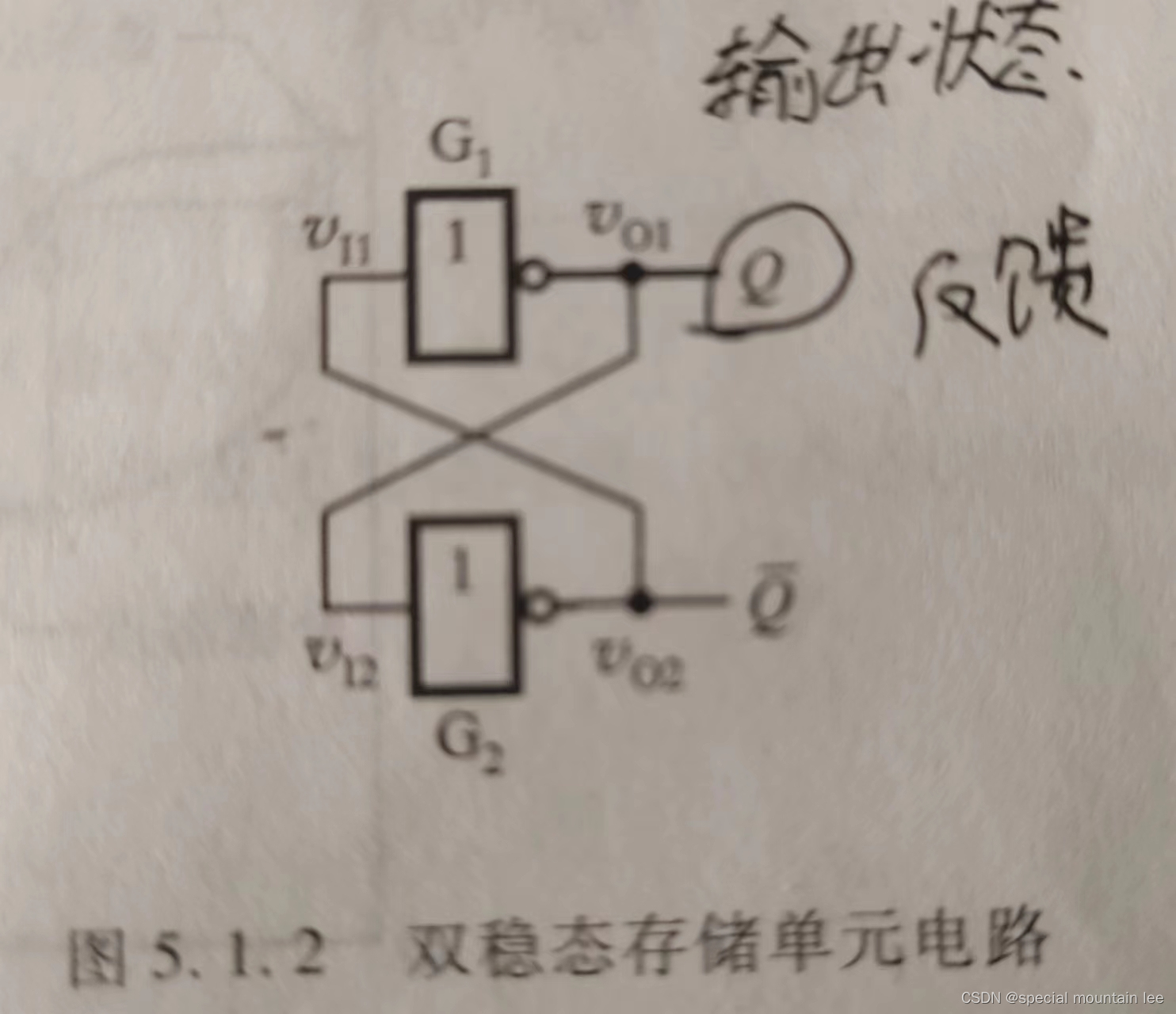

上图是双稳态存储单元电路,双稳态是指稳态0和稳态1(有时候会出现介稳态),这也是锁存器和触发器两者的共同点。由于这个特点,这两个器件只能长期存储一位二进制数,只有在外部信号作用时才能发生改变。上图的电路可以在两种稳定状态之间切换,并且能够在没有持续输入信号的情况下保持在当前状态。

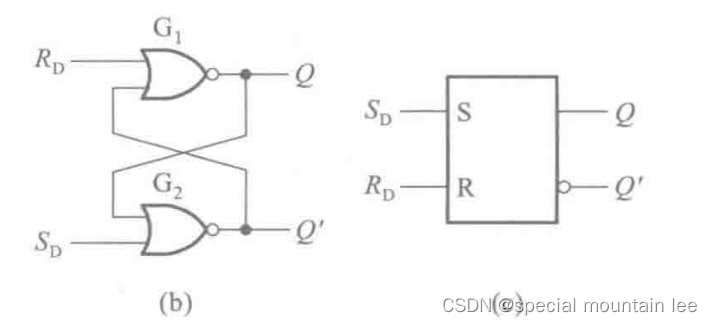

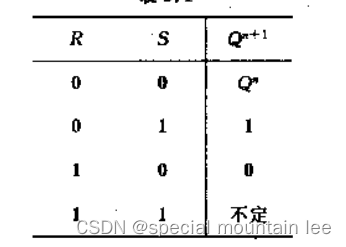

锁存器是一种对脉冲电平敏感的存储电路。它们可以在特定输入脉冲电平作用下改变状态。有基本SR(Set-Reset)锁存器,D锁存器,JK锁存器和T锁存器。要说最基本的应该是SR锁存器,其他的锁存器都是基于它的电路做出相应的功能扩展。像SR只有保持、低电平、高电平和不确定这四种状态,而JK锁存器则是具有置位、复位和翻转功能。来看看电路图。

这是用或非门构成的SR锁存器的电路图。当然还有其他的就不考虑了,看看它的这真值表。

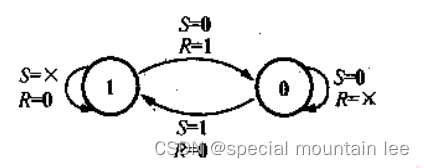

这里大家在做题的时候,还要知道一个新概念——状态图。状态图是一种用于描述系统或对象在不同状态之间的转换以及在每个状态下可能发生的动作和事件的图形表示方法。要理清现态与次态,输入和输出之间的关系。以SR锁存器为例,来看看它的状态图。

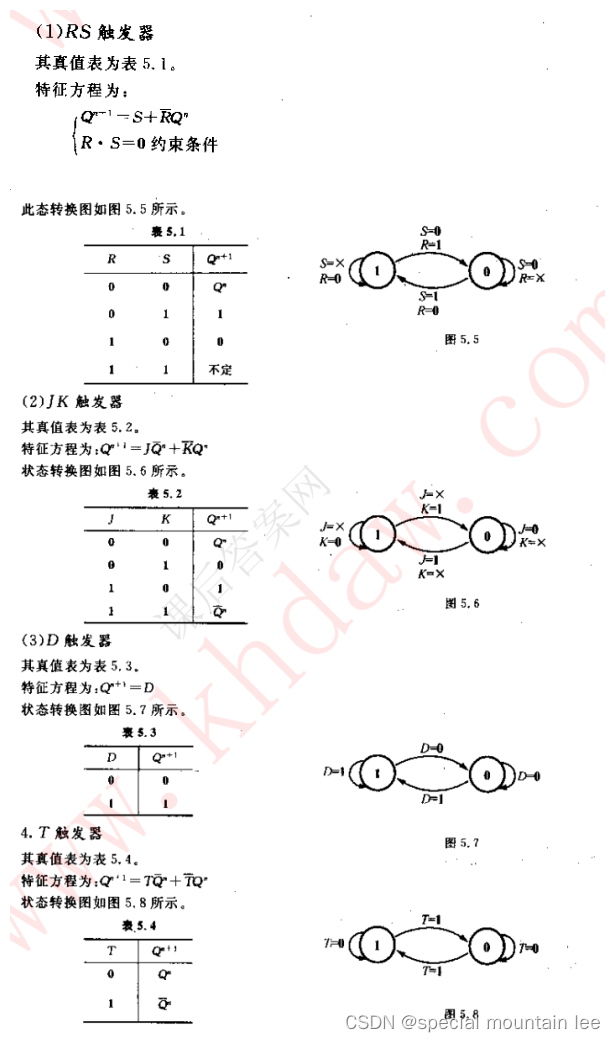

接下来是触发器,在脉冲边沿作用下的状态进行刷新。虽然它与锁存器的状态转换方式不同,但是触发器的内核本质上仍是锁存器。触发器可以分为主从触发器、维持阻塞触发器。这里不进行细讲,感兴趣的同学可以去百度上搜搜。按逻辑功能可以分为D触发器、JK触发器、T触发器、SR触发器以及T'触发器。这里咱们主要关注它们的特性表、状态图。

大家理解记忆。这里还有两个注意点。当输入信号相同(J=K)时,JK触发器构成T触发器。当输入信号相反(J=K')时,JK触发器构成D触发器。怎么得到的呢?但凡遇到触发器的转换时,大家只要注意到特征方程,进行对比就行了。

讲完了锁存器和触发器这两个基本逻辑电路。来看看它和组合逻辑电路的结合体——时序逻辑电路。根据触发器的时钟是否在同一个时钟脉冲下,分为同步时序逻辑电路和异步时序逻辑电路。说到这里咱们就要看看时序逻辑电路的设计和分析了,首先是分析的步骤:1、确定电路的组成部分:包括触发器、组合逻辑电路等,并确定触发器的类型和数量。2、写出时钟方程:即各个触发器的时钟信号表达式。3、写出驱动方程:根据电路中输入信号和触发器的逻辑关系,写出每个触发器输入信号的表达式。4、写出状态方程:根据触发器的特性方程和驱动方程,推导出每个触发器次态的表达式。5、列出状态转换表:列出电路所有可能的状态以及在输入和时钟作用下的次态。6、画出状态转换图:以图形的方式直观地展示状态之间的转换关系。7、描述电路的逻辑功能:根据状态转换图和状态转换表,总结电路的逻辑功能。其次是设计的步骤:1、逻辑抽象:明确设计要求,确定输入、输出变量以及电路的状态数。2、状态分配:给每个状态指定一个二进制代码。3、画出状态转换图:根据设计要求,画出状态之间的转换关系及对应的输入、输出。4、写出状态方程和驱动方程:根据状态转换图,推导出状态方程和驱动方程。5、检查自启动能力:确保电路在任何初始状态下都能进入有效循环。6、画出逻辑电路图:根据驱动方程和输出方程,画出实际的逻辑电路图。

好了,今天就记这么多。明天来看看时序逻辑电路的几个典型案例。

欲知后事如何,且听下回分解。OVO..........

664

664

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?