前言

在前面我们了解了CPU的结构,功能;进一步探究了指令不同周期其数据的流向;紧接着进一步探究每条指令执行的每一步微操作命令的数据是如何在CPU中流动的,以一个加法指令进行讲解的其每一步微操作的数据流向。我们通过之前的学习,了解到了,每一个微指令的执行必定伴随着某些由微指令发生器发出的控制信号控制着数据的流向,这一节我们将学习,控制器是如何发出这些控制命令的。

一、控制器的功能和工作原理

控制器,即就是CU,对于CU的实现有两种方式,一种是硬布线的方式,一种是微程序控制的方式;硬布线方式就是直接由硬件设计完成,根据各种状态来发出各种的微操作信号,如信号(MARin和PCout信号,若CU发出此控制信号,就可以实现微操作(PC)-->MAR,将PC中的指令地址送入MAR中)。

1.1硬布线方式

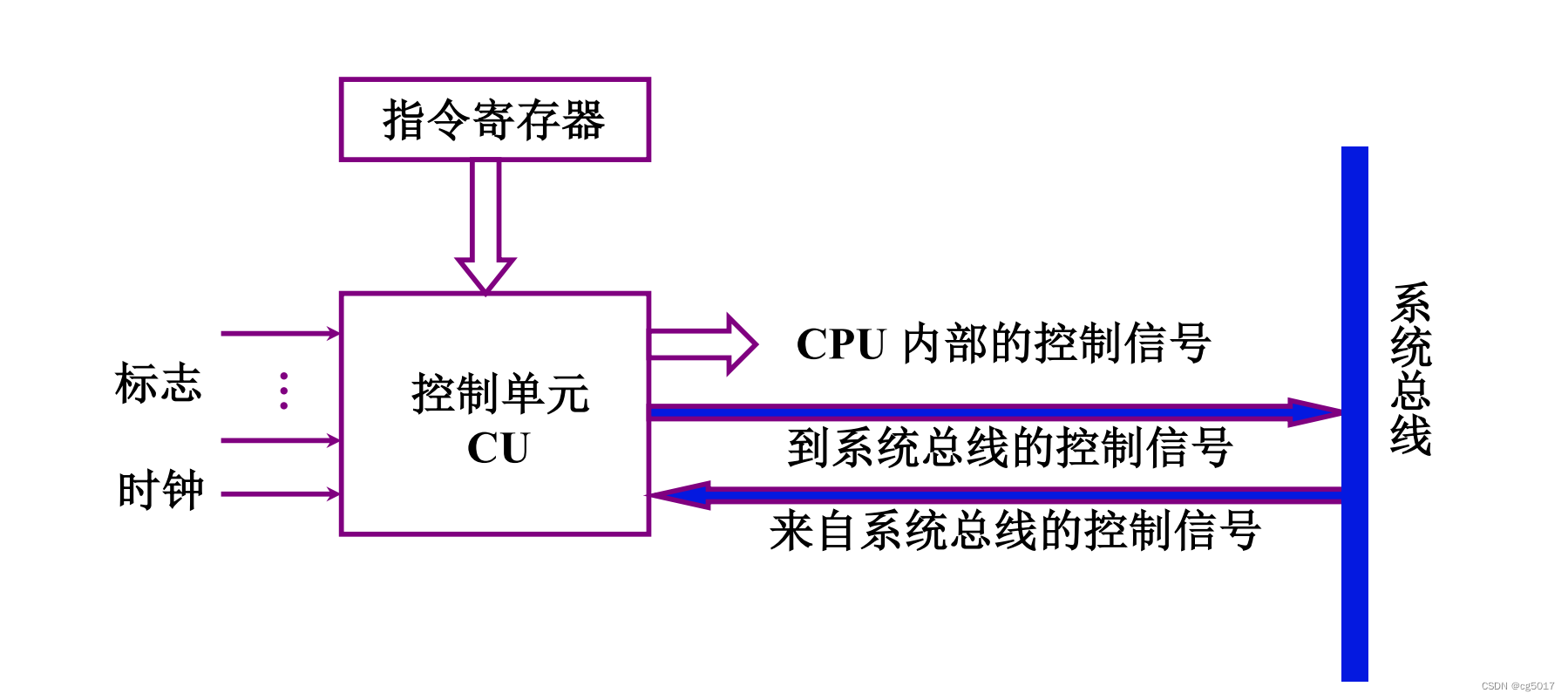

先来看下控制单元CU如何产生一系列微操作信号;首先由指令寄存器将指令操作码部分送入指令译码器,将译码结果送入CU控制器,同时还需要时钟控制的时钟信号和来自ALU中PSW寄存器中的状态一起被输入到CU控制单元;这些然后会由控制器产生对应的微操作信号,微操作控制信号的产生就会促使微操作的进行。

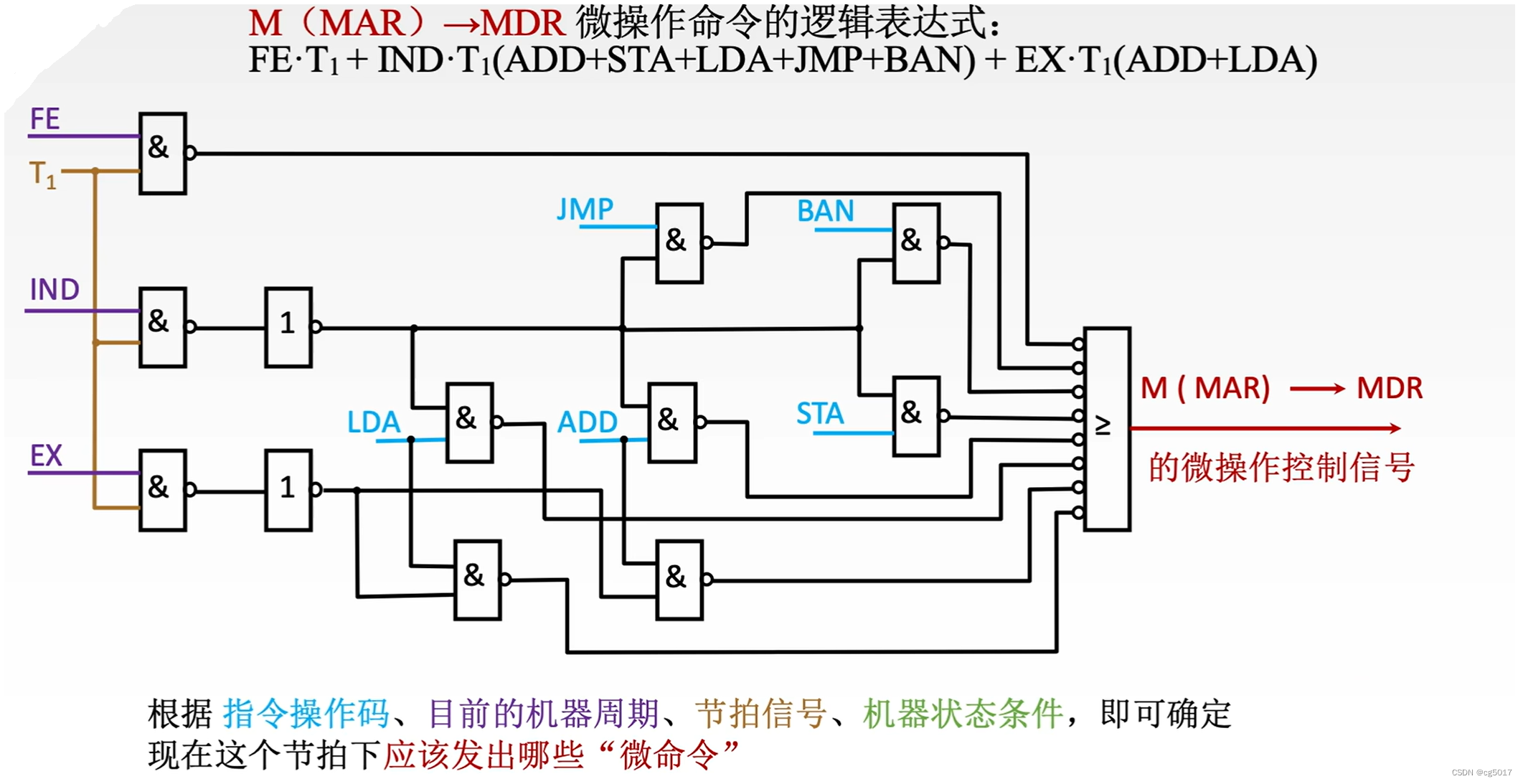

①以一条微指令的执行来看其如何实现硬布线

FE、IND、EX分别表示是取址周期,间址周期和执行周期信号,因为对于微操作M(MAR)-->MDR是在这三个周期里都可能会被用到的,所以使用该信号控制是哪个周期里执行该微操作指令。对于T1信号是时钟信号,时钟信号给出其现处于哪个节拍,因为在一个机器周期内,例如一个取址周期内,其可能是由多个节拍组成的,而在每个节拍内CU都会发出相应的控制信号来控制微操作的执行,而其实所有的微操作也是有步骤的,所以还需要时钟信号来控制每个机器周期内每个微操作的命令的执行顺序。

分析微操作M(MAR)-->MDR的逻辑表达式

① FE*T1有效:FE表示是在取址周期,T1有效,也就是说取址周期内,在某个T1时钟周期内有效的时候,就会直接形成该微操作的信号。我们来回顾一下取址周期的所需要进行的微操作(PC–>MAR (1),M(MAR)–>MDR (2),MDR–>IR (3),PC+1–>PC(4))这些微操作的执行都是在每个时钟周期下控制完成的,并且得有序进行,比如序号为1的指令就必须在T0时钟周期内完成,序号为2的指令就必须在T1时钟周期内完成,序号为2,3的指令就必须在T2时钟周期内完成,为什么序号为2,3的指令可以同时在同一个周期内完成呢?适应为微指令的操作对象不同,所以可以同时进行;所以不难发现在取址周期内微指令M(MAR)-->MDR的执行是必须要在T1时钟内完成的并且此时机器周期标记FE有效。

② IND*T1(ADD+STALDA+JMP+BAN)有效:IND表示间址周期,ADD+STALDA+JMP+BAN表示不同的指令信号,由指令译码电路传送给微命令发生器,由于间址阶段的微操作M(MAR)-->MDR也是只能在T1时钟内才有效。

③EX*T1*(ADD+LDA)有效,必须是处于指令的执行阶段,即EX有效,且处于执行周期的第二个节拍,即T1时钟内进行,同时要求指令类型为ADD或者LDA。

所以,对于任意一个微操作的发生,它是可能出现在任意一个时期的任意一个阶段,所以对于硬布线来实现CU,我们必须清楚的规定该微操作发生于哪个指令周期,指令周期的哪个节拍,哪个指令执行需要用到该微操作,以及来自PSW等的状态,这样就可以根据这些给出相应的操作信号,从而执行微指令。

② 硬布线的优缺点

优点: 全部由硬件来实现,速度快,一般RSIC精简指令集使用硬布线实现CU。

缺点: 硬布线硬件成本高,同时对于指令的增加和减少十分不友好,一但指令增加或者减少的话,就得需要重新设计电路图;对于CSIC指令集不适用,因为指令多,硬布线的线路就会十分的复杂。

为了实现CSIC指令集的控制执行,便出现了微程序控制的方式,下一小节,我们将学习微程序控制的方式来实现CU控制器。

4482

4482

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?