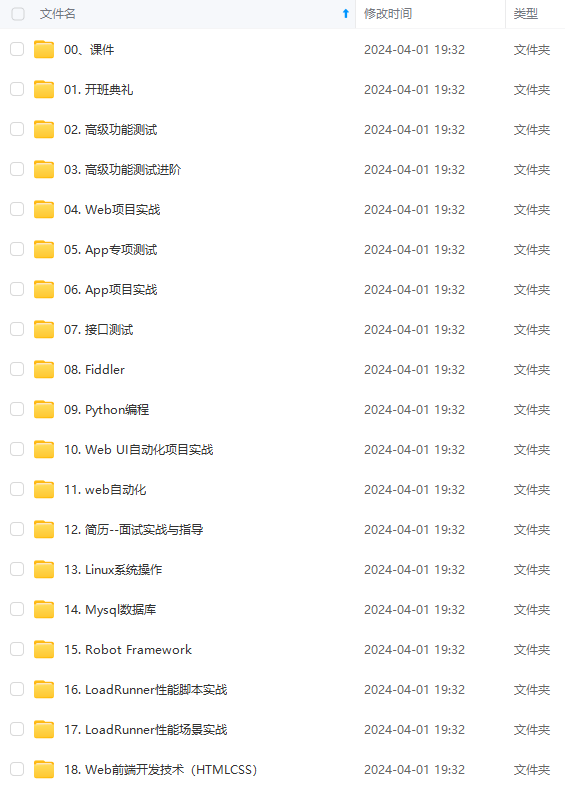

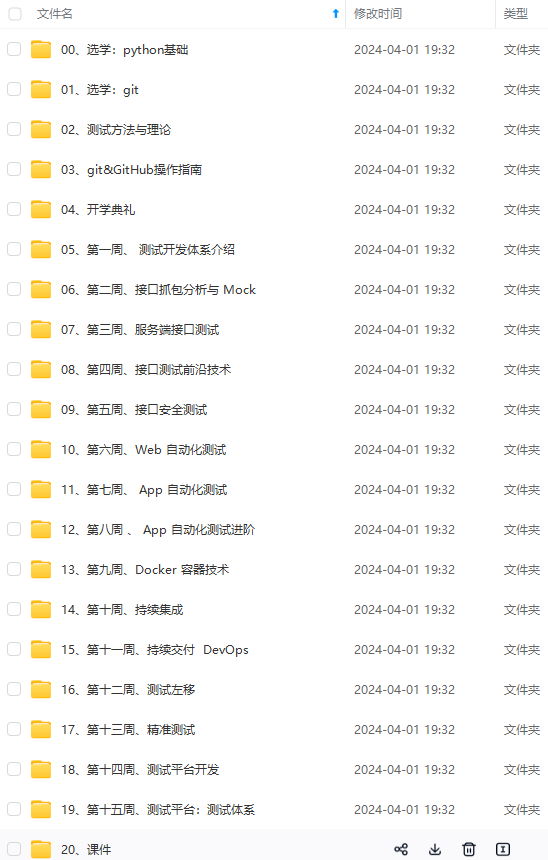

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上软件测试知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

1.普通寄存器:一定会有控制信号控制读/写(可能分开,2bit;可能合并,1bit)

2.暂存寄存器:单总线结构下,总线只能有一个输入,但是ALU需要有两个数据,故需要通过先把一个数据放入暂存寄存器中,然后以一个数据从总线输入,一个数据从暂存寄存器输入的方式实现ALU运算

3.通用寄存器组:需要有控制信号用于选择是哪个通用寄存器

4.带有移位功能的寄存器:每左移一位,真值 * 2;每右移一位,真值 / 2

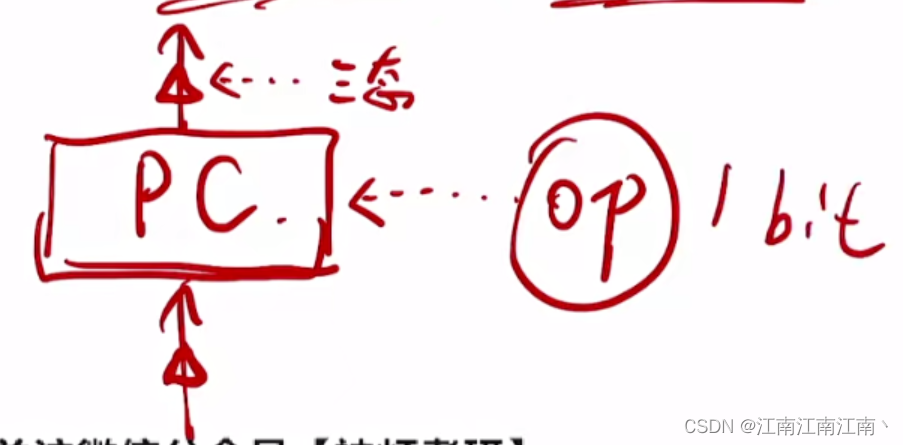

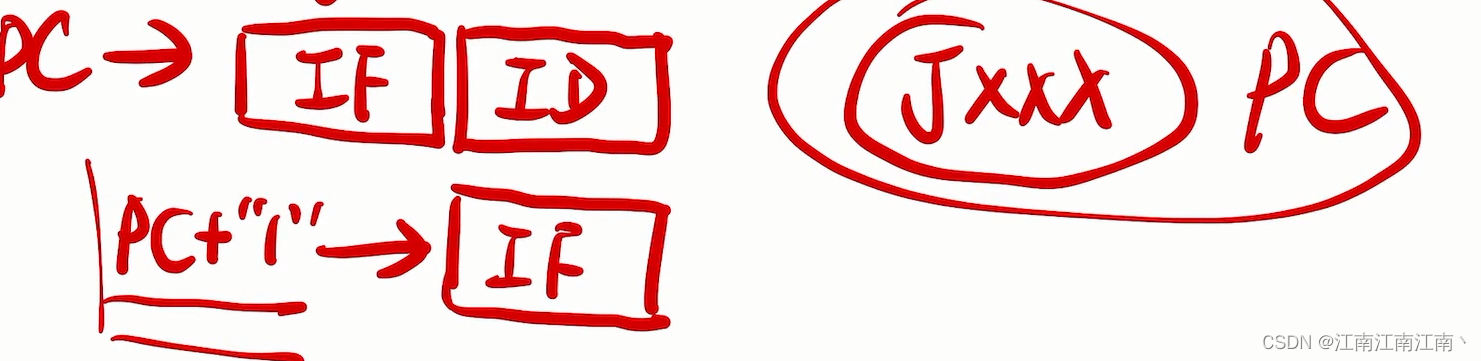

5.带自增功能的寄存器:PC寄存器可以通过自增功能自动实现PC + “1”

4和5这种带有特殊功能的寄存器需要有控制信号(至少1bit,支持的功能越多,控制信号的位数也就越多,需要保留一种状态表示什么都不做,即直送)控制其是否进行此功能:例如PC,当给它施加的op = 1时,即自增(PC++ );op = 0时,即不自增

4和5这种带有特殊功能的寄存器需要有控制信号(至少1bit,支持的功能越多,控制信号的位数也就越多,需要保留一种状态表示什么都不做,即直送)控制其是否进行此功能:例如PC,当给它施加的op = 1时,即自增(PC++ );op = 0时,即不自增

6.带有其他功能的寄存器:取反、移位等等

数据产生变化的地方除了操作元件外,寄存器本身也可能支持对数据进行某种简单处理

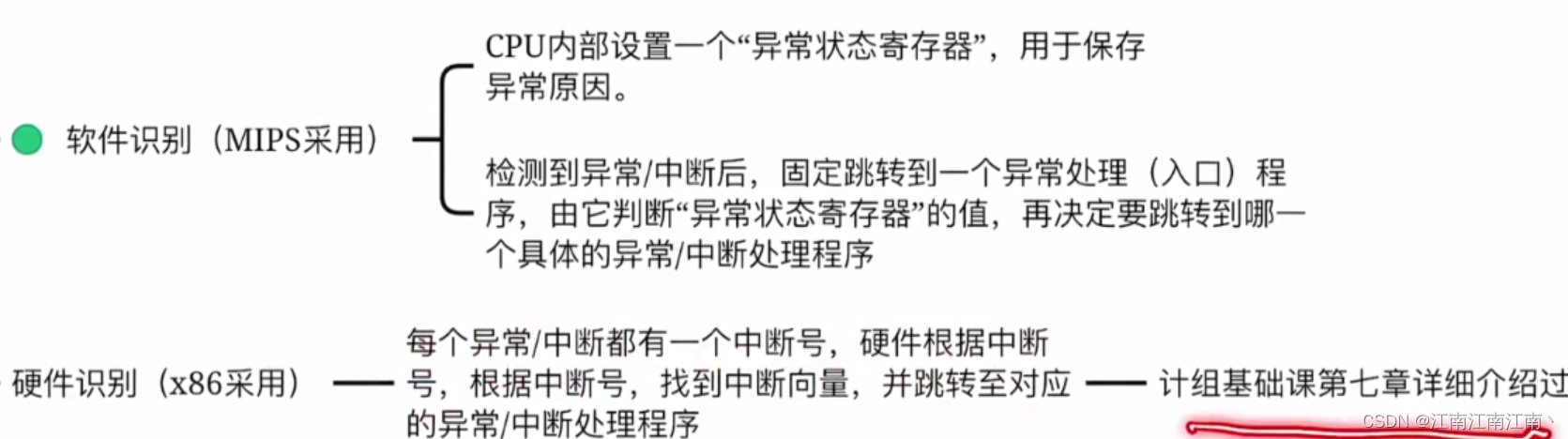

4.中断

1.硬件识别:硬件检测到中断号后,根据中断号决定执行的中断处理程序在哪,并执行

1.硬件识别:硬件检测到中断号后,根据中断号决定执行的中断处理程序在哪,并执行

2.软件识别:检测到中断后,先统一执行一个中断的入口程序,入口程序再根据当前的异常跳转到具体的中断处理程序

5.数据通路

除了控制器之外的所有用于实现指令功能的部件

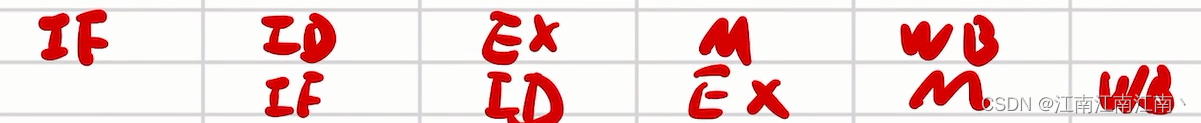

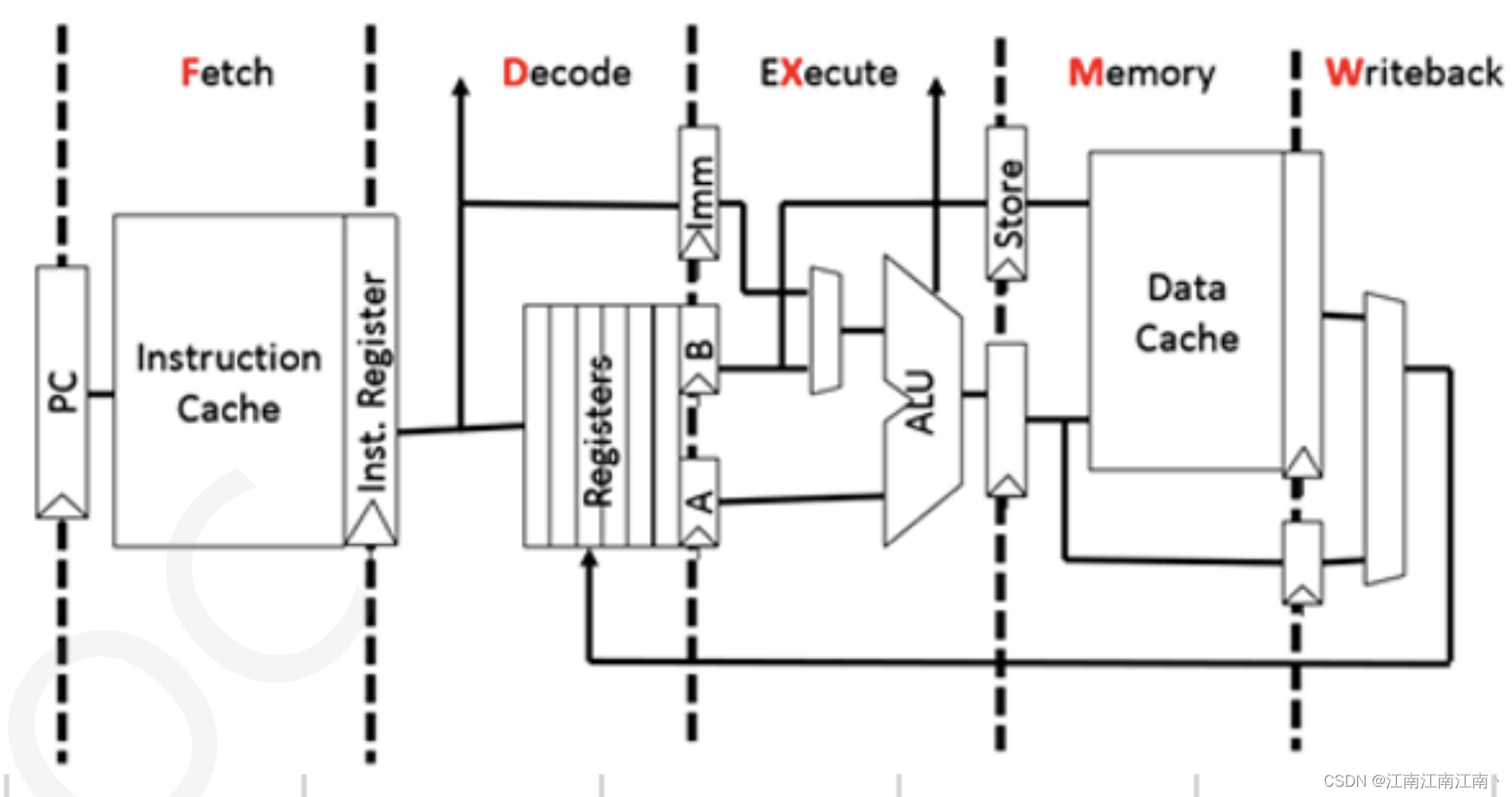

6.五段式指令流水线

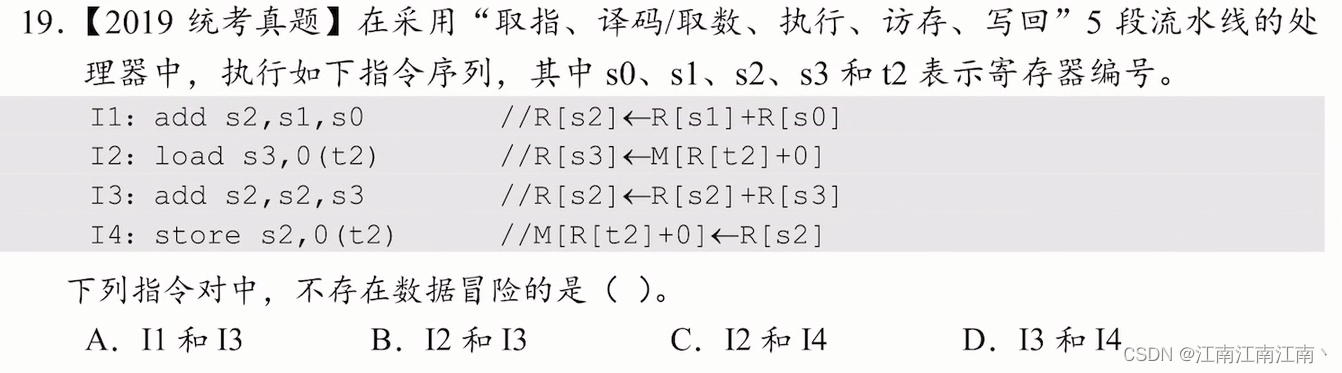

①数据冒险:前一条指令未写入,后一条指令就读出(后一条指令需要基于前一条指令的结果时)

(1)前面的指令:写寄存器发生在第五个段(WB)

(2)后面的指令:读(与前面指令相同的)寄存器发生在第二个段(ID)

(3)若后面的指令是前面指令的相邻三条指令之一(即后面的指令是前面的指令后的第一条、第二条、第三条指令),则会发生数据冒险;若后面的指令不是前面指令的相邻三条指令之一(即后面的指令至少是前面指令后的第四条指令),则不会发生数据冒险

(4)分析思路:一条一条指令从前往后分析,如果一条指令写了某个寄存器,则观察与之相邻的三条指令中,是否有哪一条指令读取同一寄存器

I1写入S2,I3和I4读出S2,且两者都是I1相邻的三条指令,故I1与I3,I1与I4数据冒险

I2写入S3,I3读出S3,I2是I3相邻的三条指令之一,故I2和I3数据冒险

I2只会改变S3的值,而I4中并未使用S3,故I2和I4不会数据冒险

I3写入S2,I4读出S2,I4是I2相邻的三条指令之一,故I3和I4数据冒险

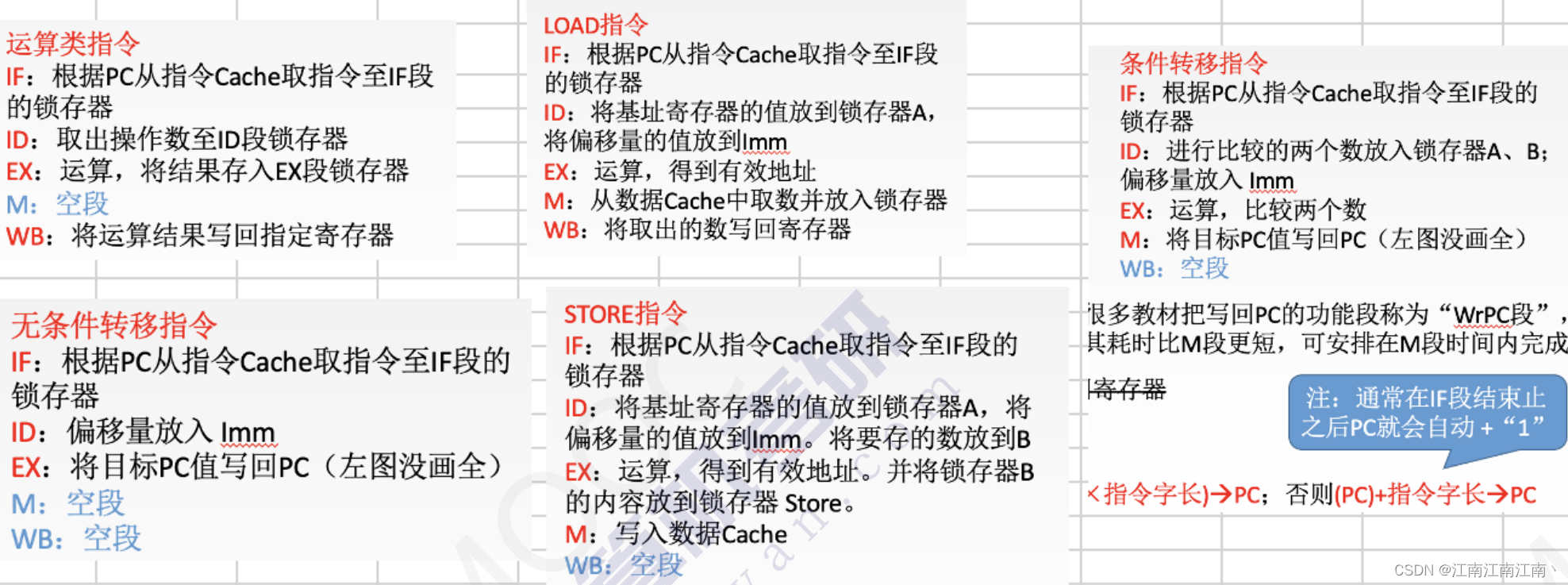

②控制冒险:在上一条指令的IF阶段完成后(取值阶段),PC会自动实现+ “1”,即会指向下一条相邻指令;但当前执行的指令如果会改变PC的值,且下一条指令的IF在上一条指令的EX前进行,则会发生控制冒险;

有条件转移(M,第四个段改变PC):EX(第三个阶段)进行条件是否满足的判断;M(第四个阶段)若条件满足则改变PC的值,不满足则不改变PC的值(此时也不会发生控制冒险);第五个段为空段(什么事都不做);故停三个周期,再取下一条指令,就不会发生控制冒险

无条件转移(EX,第三个段改变PC)(包括call和ret):在EX(第三个阶段)就写回PC;M(第四个阶段)和WB(第五个阶段)为空段(什么事都不做);故停两个周期,再取下一条指令,就不会发生控制冒险

③数据相关导致指令流水线阻塞:该指令使用了前面某条指令的数据写入

④理想情况:一条接一条往后执行

⑤为了保证能指令的每个阶段能在一个机器周期内完成,数据只能从寄存器中取,并且只能写回寄存器(采用LOAD、STORE指令访存)

⑥IF(取指令):根据PC的地址从指令CACHE中取出该指令,并放入指令寄存器IR中

ID(译码/读寄存器):根据IR中从寄存器组中取出相应的操作数,并放入A和B中;若有一个数据的寻址方式位立即寻址,即指令中包含立即数,则该立即数放入IMM中

EX(执行/计算地址):将A和B/IMM中的数据作为ALU输入的两端,经过ALU计算后,将结果输出到EX锁存器中

MEM(访存):将EX锁存器中的内容写回DATA CACHE中;计算类指令ADD在MEM阶段不需要做任何事

写回(WB):将结果写回寄存器组

⑦在上一条指令执行完某个阶段前,下一条指令不能进入该阶段:例如上一条指令正卡在ID阶段,则就算下一条指令已经执行完IF阶段,也不能进入ID阶段,原因是若下一条指令进入则会发生数据覆盖

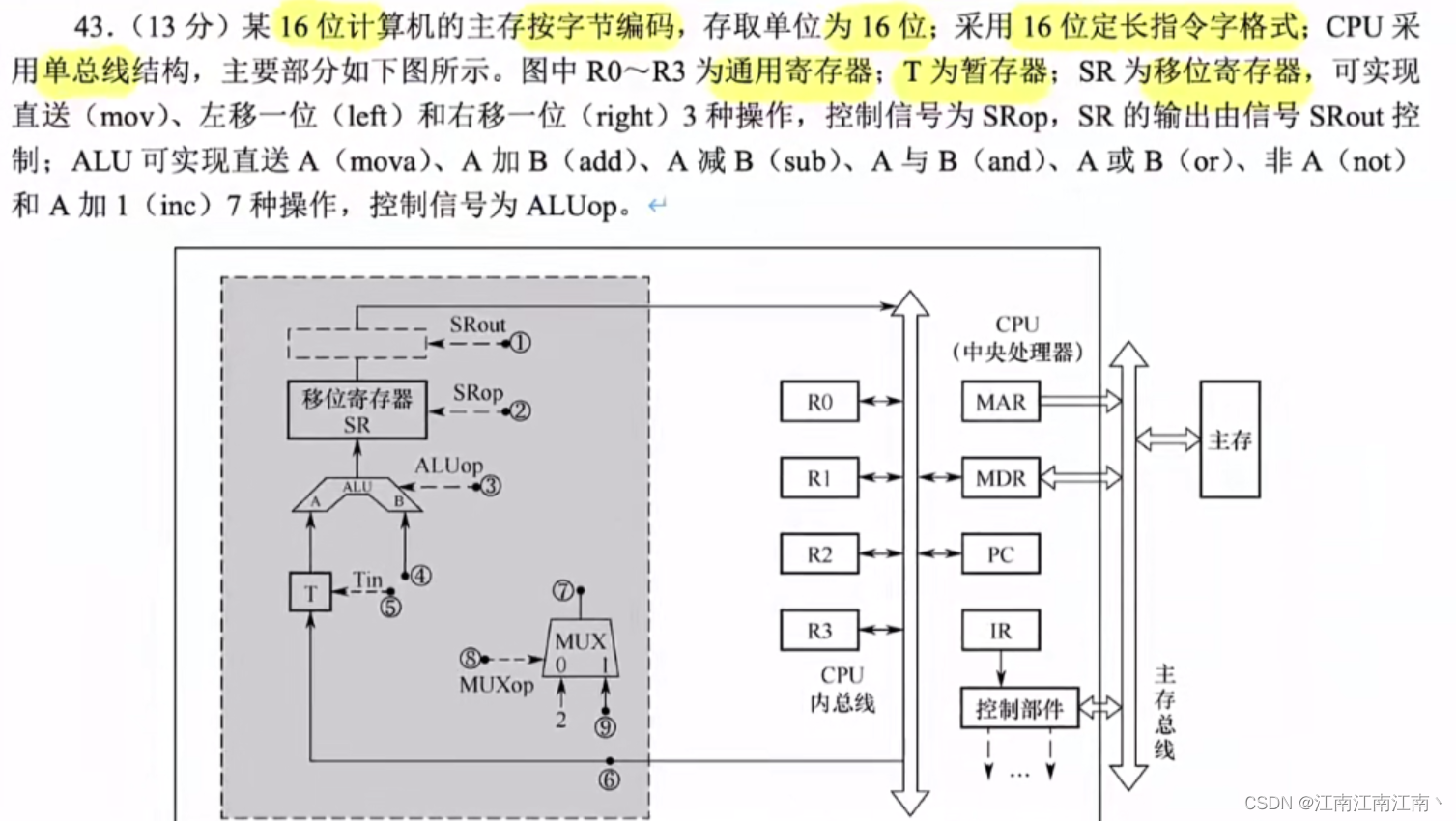

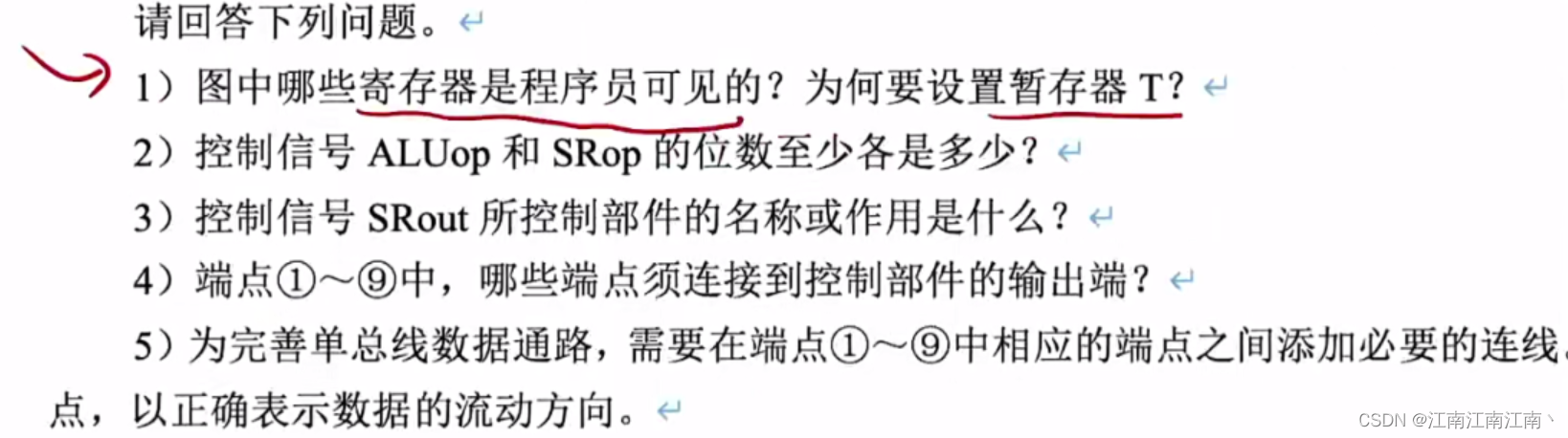

7.真题

(1)①可见:通用寄存器(R0 - R3),PC

不可见:MAR,MDR,IR,T,移位寄存器

②在单总线结构下,总线只能在同一时刻提供一个输入,而ALU需要同时有两个输入,故需要将一个数据先输入到暂存寄存器中,然后通过暂存寄存器和总线各输入一个数据的方式满足ALU两个输入的要求

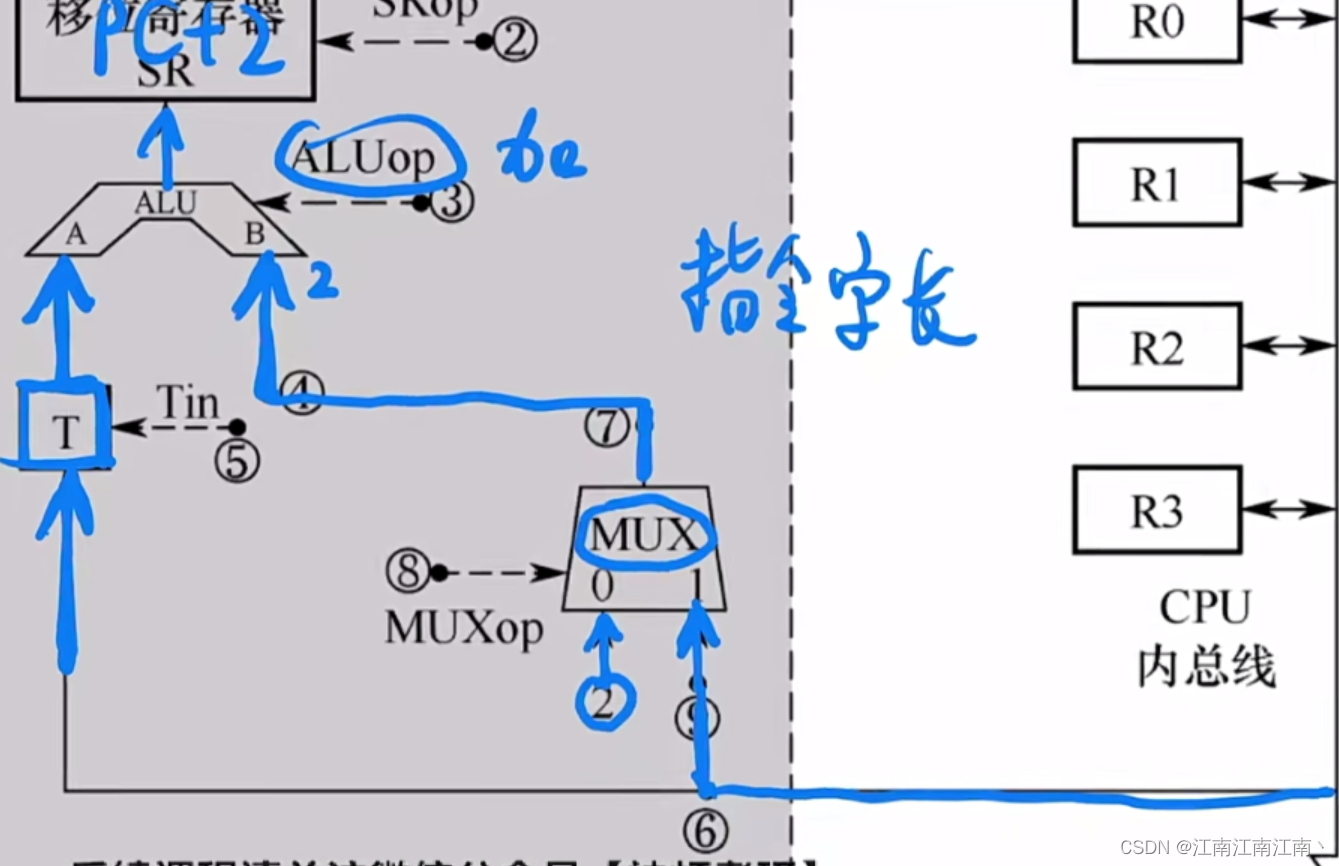

(2)①ALU支持七种操作,故需要至少3位的控制信号,即ALUop至少为3位

②SR支持三种操作,故需要至少2位的控制信号,即SRop至少为2位

(3)三态门:作用是控制移位寄存器和总线之间的数据通路是否连通

(4)①:控制移位寄存器和总线之间的数据通路是否连通

②:控制移位寄存器进行何种操作

③:控制ALU进行何种操作

⑤:控制T和总线之间的数据通路是否连通

⑧:控制MUX的0还是1端口选通

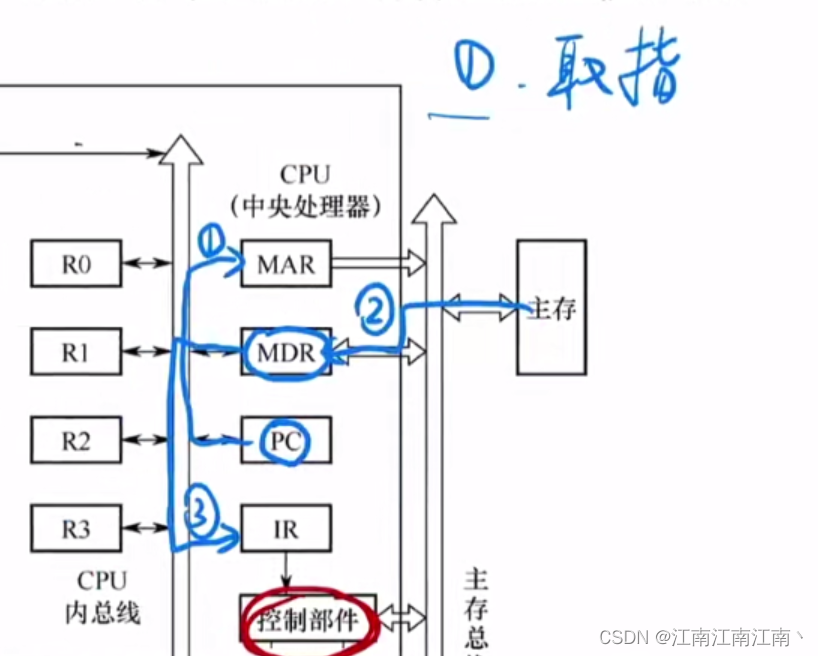

(5)取值阶段:(PC)→ MAR;M(MAR)→ MDR;(MDP)op→IR

PC + 2(指令字长为16位,按字节编码,故PC + “1” = PC + 2) :PC先经过总线输入到T中,然后通过MUXop = 0使op = 0,再给ALU施加加法命令,得到PC + 2再输入回PC中

进行其他运算时,一个数据先放在T中,然后从T输入ALU,另一个数据经过多路选择器(MUXop = 1)输入ALU

⑥→⑨

⑦→④

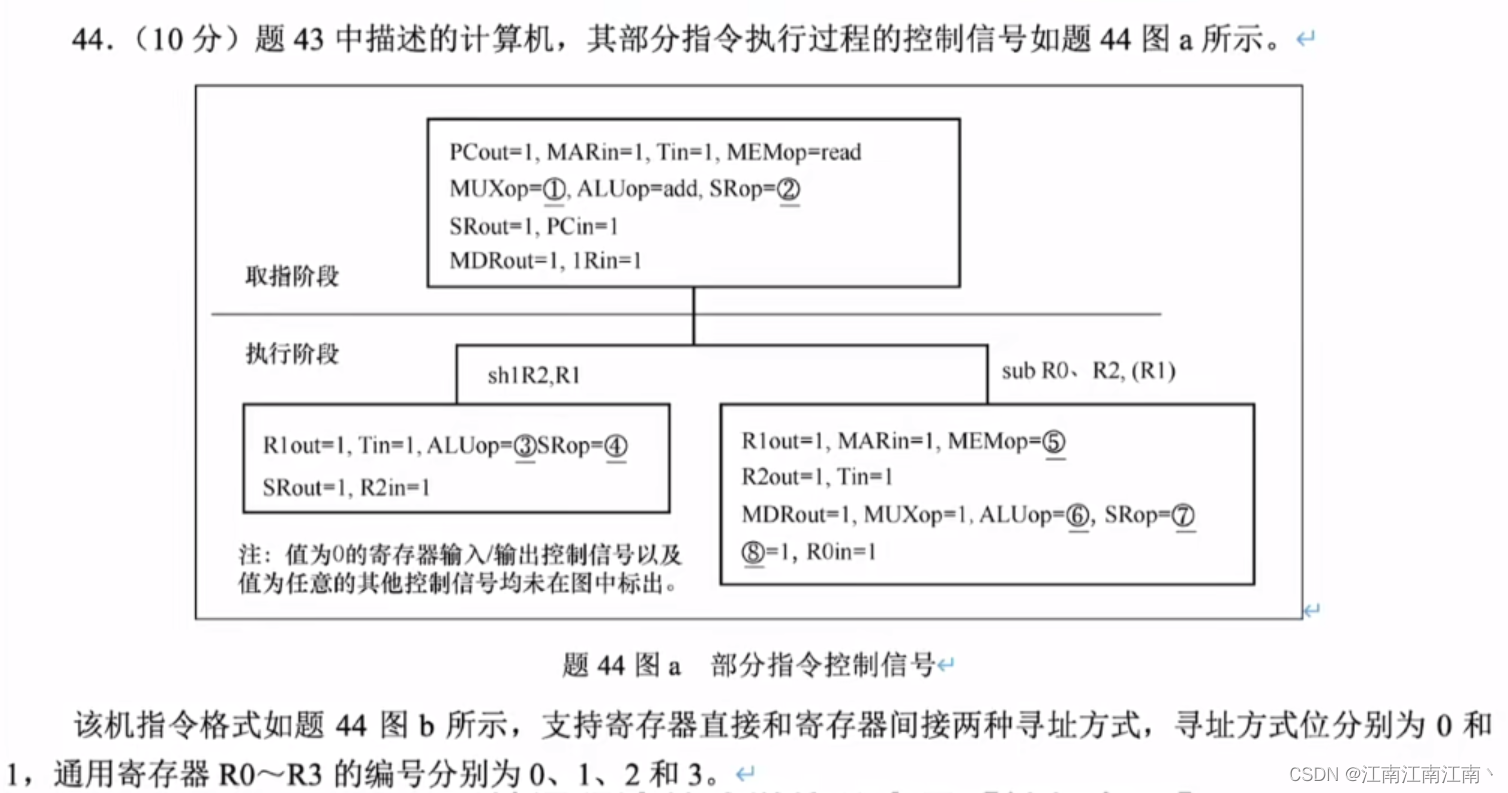

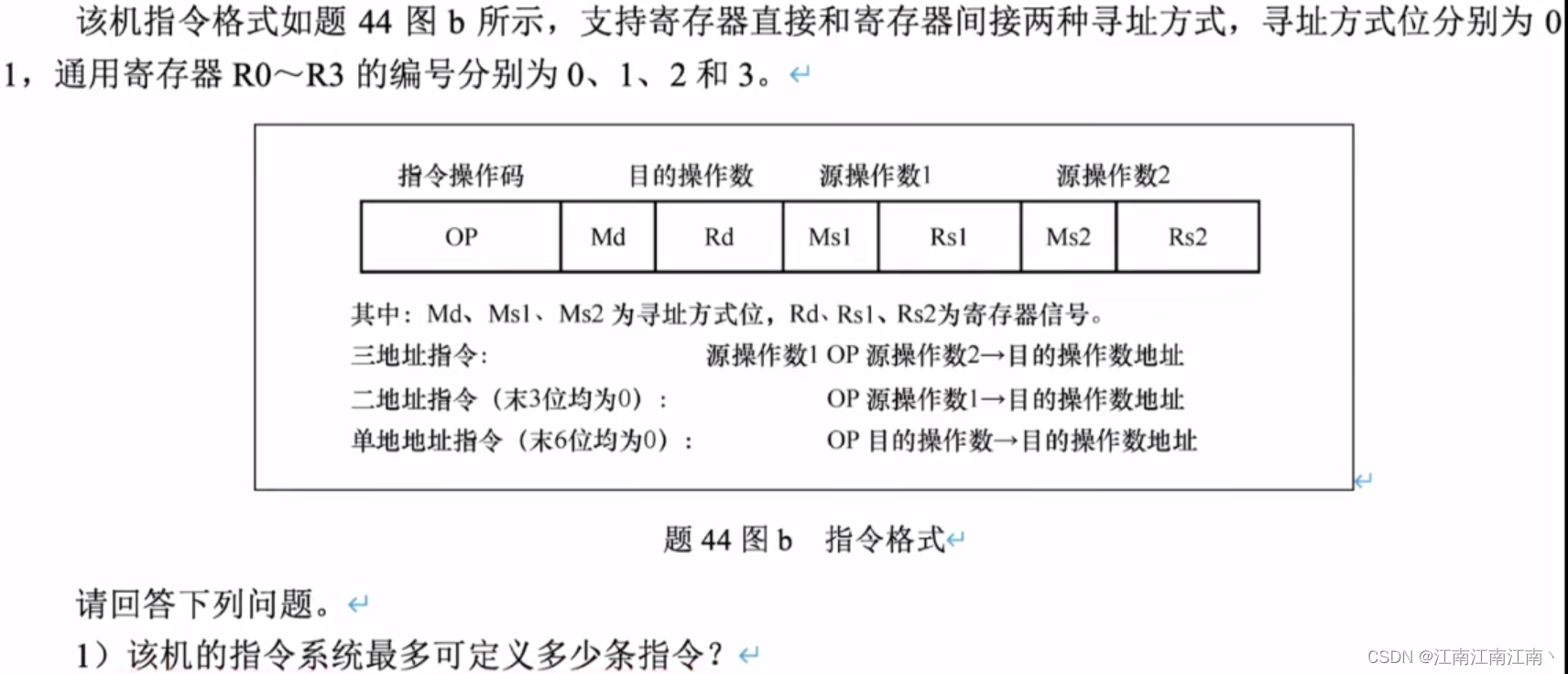

(1)①寻址方式位分别为0/1:Md、Ms1、Ms2都为1bit

②寄存器有4个:Rd、Rs1、Rs2为2bit

③指令字长为16bit → OP = 16 - 3 * (1 + 2) = 7 → 最多可以定义 2 ^ 7 = 128条指令

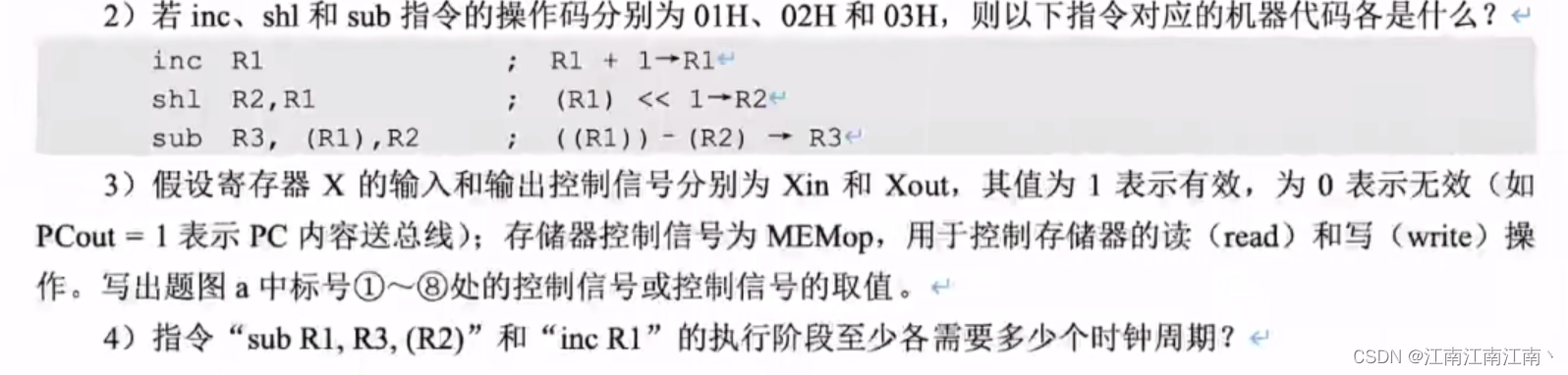

(2)①OP为7bit,则操作码分别取后七位,最高位舍去:000 0001,000 0010,000 0011

②inc:0000 001(OP)0(直接寻址)01(R1)000 000(单地址指令)

shl:0000 010(OP)0(直接寻址)10(R2)0(直接寻址)01(R1)000(二地址指令)

sub:0000 011(OP)0(直接寻址)11(R3)1(间接寻址)01(R1)0(直接寻址)10(R2)

即0240H、0488H、06EA

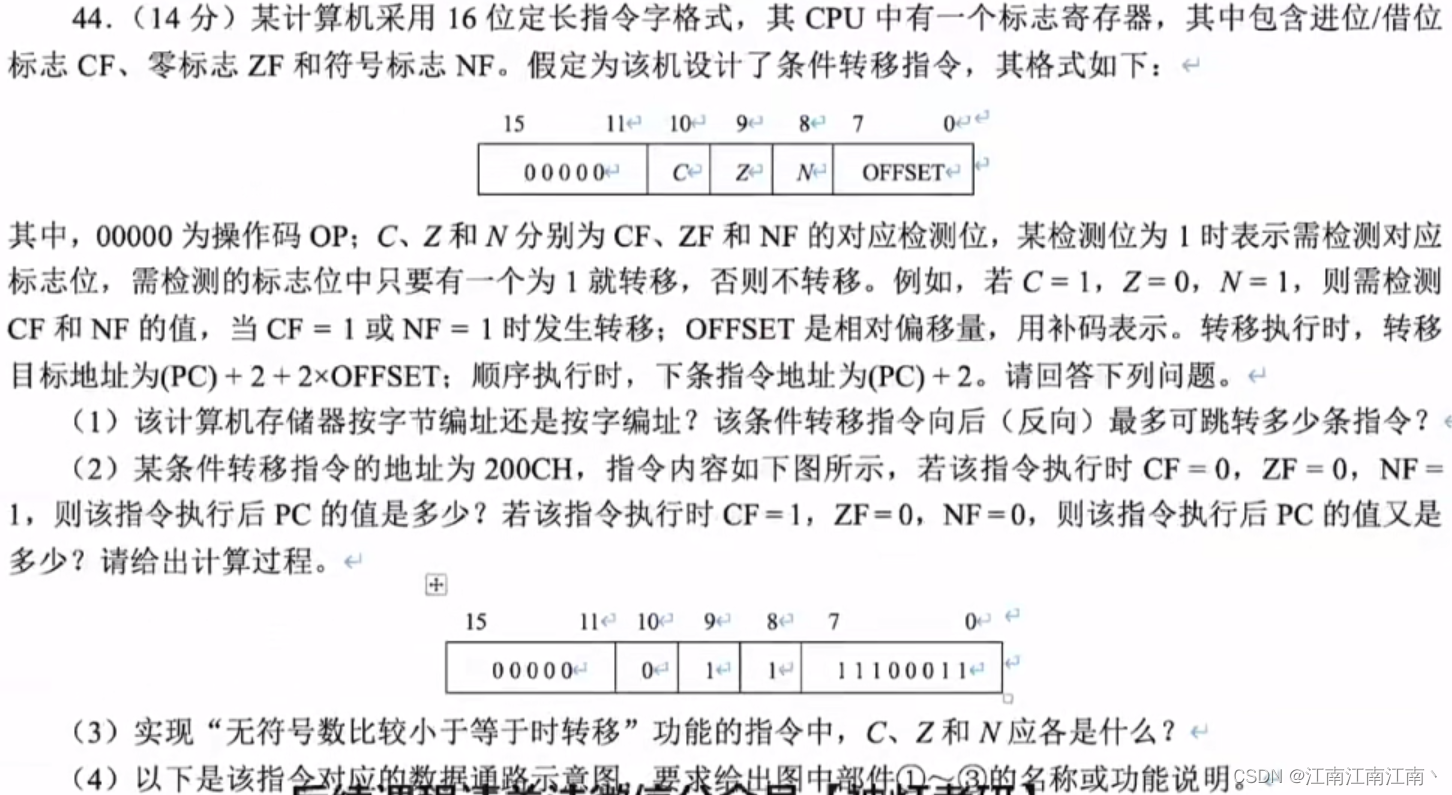

(3)①取值阶段:((PC))→IR(即将PC所指的指令,取到IR中);PC + “1”

第一步:PCout = 1,MARin = 1,Tin = 1,MEMop = read:PC中的数据输入到总线中,MAR和T同时读入PC的数据,并且对主存进行读操作(完成以PC值为地址取值,并PC+"1"做准备)

第二步:MUXop = 0,ALUop = add,SRop = mov:T寄存器中的内容和MUX0端一起输入ALU的两端,同时将SR的操作设置为直送(实现PC + “1”)

第三步:SRout = 1,PCin = 1:将SR寄存器中的内容输出到总线中,并输入PC

第四部:MDRout = 1,IRin = 1:将从主存中取出的指令从MDR输入IR中

②执行阶段:shl R2,R1

第一步:R1out = 1,Tin = 1,ALUop = mova,SRop = left:先将R1寄存器中的数据经过总线输入到T寄存器中,给ALU一个直送的控制信号(即不对数据进行处理,因为题中的ALU没有左移功能),数据经过ALU到了SR后,SR对该数据进行左移处理

第二步:SRout = 1,R2in = 1:将SR中的数据经过总线输入R2寄存器中

执行阶段:sub R0、R2,R1

第一步:R1out = 1,MARin = 1,MEMop = read:寄存器间接寻址,将R1中的内容作作为地址,放入MAR中,再读取该地址的数据

第二步:R2out = 1,Tin = 1:将R2寄存器中的数据经过总线输入到T寄存器中(ALU的计算需要两个输入)

第三步:MDRout = 1,MUXop = 1,ALUop = sub,SRop = mov,SRout = 1,R0in =1:第一步根据R1地址从主存读入的数据存放在MDR中;MDR中的数据经过总线输入到MUX中,MUX的1端连通,故数据经过MUX和T寄存器中的数据一起输入ALU;给ALU一个sub控制信号,使其进行减法操作,结果输出到SR中;给SRmov的控制信号,使其不对数据进行任何处理,并通过总线输入到R0

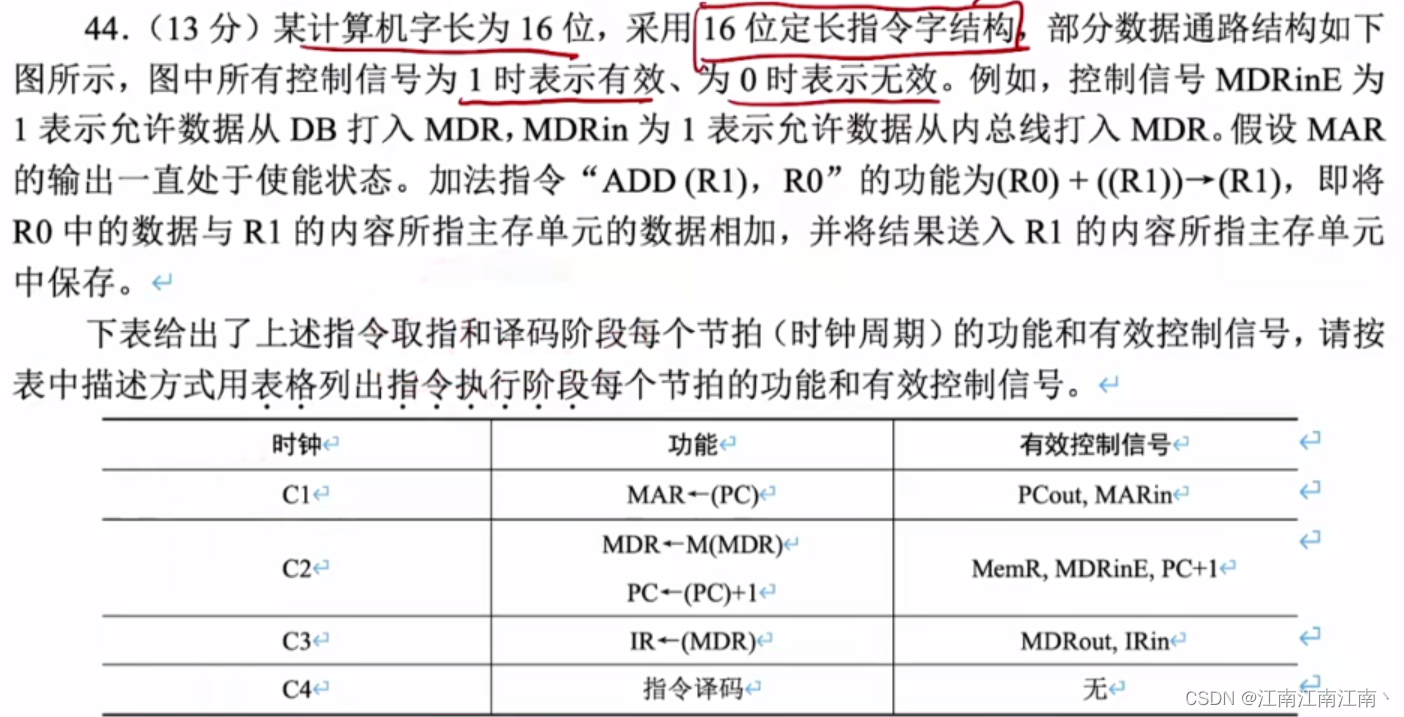

C5:(R1)→ MAR R1out,MARin

C6:M(MAR)→ MDR MemR,MDRinE

C7:(MDR)→ A MDRout,Ain

C8:(R0)+(A)→ AC R0out,ADD,Cin

C9:(AC)→ MDR ACout,MDRin

C10:(MDR)→ M(MAR) MemW,MDRoutE

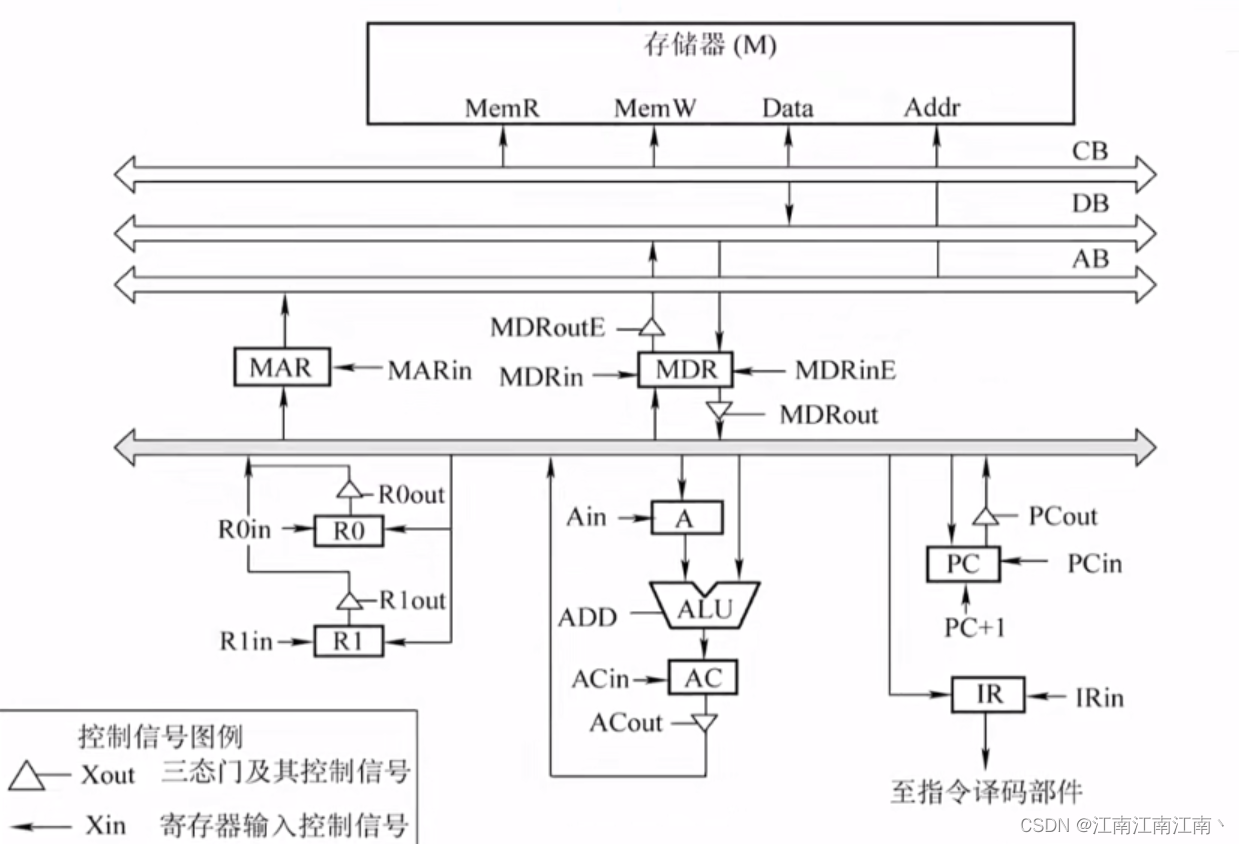

(1)①16位定长指令字格式 + 下条指令地址为(PC)+ 2 :按字节编址

(1)①16位定长指令字格式 + 下条指令地址为(PC)+ 2 :按字节编址

②OFFSET用补码表示,8bit补码的表示范围为-128到+127,目标地址为2 * OFFSET,即OFFSET的值就代表其偏移的指令条数,而PC每次执行后会自动指向下一条指令,故最多可以向后偏移128 - 1 = 127条指令

(2)①NF = 1,则需要检查NF的值,而指令中NF的值为1,故需要发生转移,OFFSET的值为1110 0011,即E3H,负数符号扩展后为FFE3H,乘以二即左移1位 = FFC6H,故PC = 200CH + 0002H + FFC6H = 1FD4H

②CF = 1,则需要检查CF的值,而该指令中CF的值不为1,则不需要发生转移,故PC = 200CH + 0002H = 200EH

(3)无符号数比较小于等于即发生借位或者等于0,故检查CF和ZF,故C = 1,Z = 1 ,N = 0

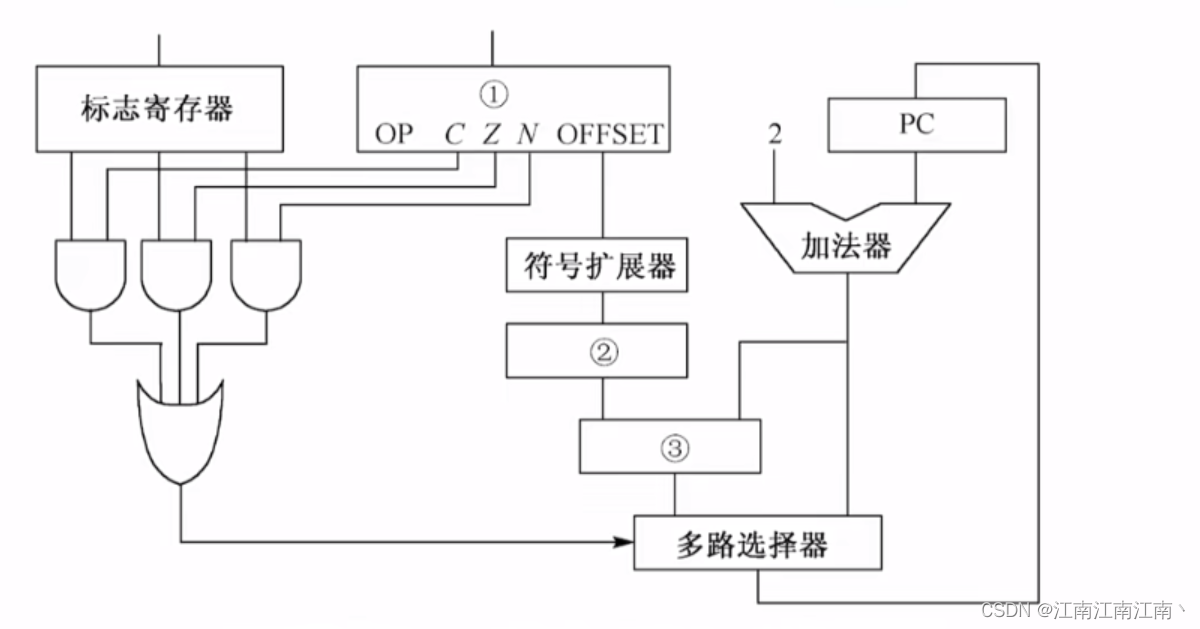

(4)1.①中由OP、CF、ZF、NF、OFFSET组成,与指令的组成部分一致,故①是指令寄存器

2.每条指令的执行结果有两种:PC + 2和PC + 2 + OFFSET * 2,这两种结果的输出分别是多路选择器左端和右端的输出(通过IR寄存器C、Z、N位和标志寄存器输出的CF、ZF、NF相与得到多路选择器的控制信号,即选择多路选择器的哪个端口输出):

右端:PC输出在加法器的右端,在经过加法器后,和加法器左端的2进行加法操作,得到PC + 2

故右端的输出为PC + 2 + OFFSET * 2:在经过③前已经得到了PC + 2,还需要OFFSET * 2,故②为移位寄存器,实现移位操作,即通过左移得到OFFSET * 2;③为加法器,实现PC + 2和OFFSET * 2的相加,得到左端的最终输出PC + 2 + OFFSET * 2

①(R2)<< 2 → R4:R2寄存器中存放的是变量i,变量i左移2位,即变量i = i * 4,再将结果放回R4中;该指令的作用是得到A[i]的相对于A[0]的地址偏移量;从此处可知,数组A的每个元素的单位大小为4B

②(R4)+(R3)→ R4:R3寄存器存放的是数组A的首地址,R4寄存器存放的是A[i]地址相对于数组A的首地址的偏移量,两者相加得到A[i]的地址;A[i] = 始址 + 下标 * 元素大小

③((R4)+ 0)→ R5:R4寄存器存放的是A[i]的地址,根据此地址从主存中取出数据,即取出数组A的第i个元素放入R5中

④(R1)+(R5)→ R1:R1寄存器存放的是当前A数组前i - 1个元素总和的变量sum,R1 + R5得到数组A前i个元素的和,并结果放回R1中,即完成sum += A[i]

⑤(R2)+ 1 → R2:R2寄存器存放的是每轮i的取值,即完成i++

⑥if(R2)! = (R6)goto loop:R6寄存器存放的是变量N,即判断R2和R6是否满足循环结束的条件,若不满足,则跳转回LOOP处执行指令;若满足则,顺序执行指令,即实现for循环

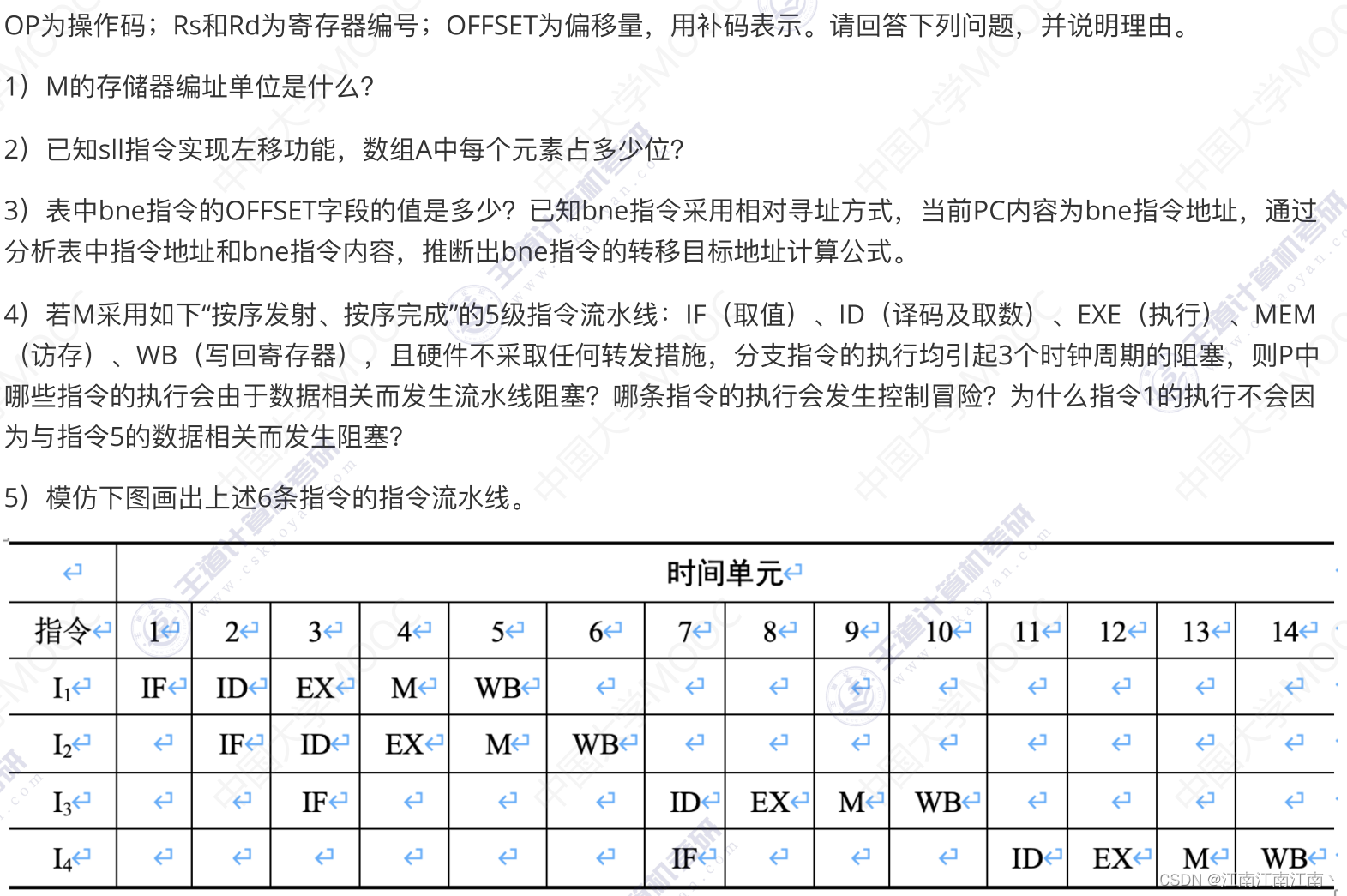

(1)每行的机器代码是4B,每行指令地址相差4,故编制单位为字节

(2)①②③的作用是得到A[i]的地址,在①中i左移两位即i = i * 4,说明每个元素占用4B

(3)①bne指令为1446 FFFAH,根据指令格式可知末尾2B为OFFSET,FFFA = -6,即该指令实现向后偏移6个单位

②根据bne指令的地址0804 8114H和LOOP地址0804 8100H对比可知,该OFFSET的单位并不是字节,而

③oop指令和bne指令相差5个指令,PC在执行bne指令时实现PC + “1”,即指向bne的下条指令,故执行bne指令时,loop的地址和PC的值相差6个指令,满足向后偏移6个单位,可知OFFSET的单位是指令字长

④得到bne指令的转移目标地址计算公式:PC + 4 + (OFFSET * 4):PC + 4实现指向PC + “1”,OFFSET * 4表示按指令字长为单位进行偏移

(4)①(R2)<< 2 → R4:结果写回R4

②(R4)+(R3)→ R4:①写入R4,②读出R4,但②是①的相邻第一条指令,数据冒险

③((R4))+ 0 → R5:②写入R4,③读出R4,但③是②的相邻第一条指令,数据冒险

④(R1)+(R5)→ R1:③写入R5,④读出R5,但④是③的相邻第一条指令,数据冒险

⑤(R2)+ 1 → R2:①写入R2,⑤读出R2,⑤不是①的相邻三条指令其中之一,不会数据冒险

⑥if(R2)!= (R6)goto loop:⑤写入R2,⑥读出R2,但⑥是⑤的相邻指令,数据冒险

故②③④⑥发生数据冒险

⑥只有转移指令才会发生控制冒险,只有⑥为条件转移指令,故⑥发生控制冒险

分支指令(bxxx,ARM架构下的条件转移指令)的执行均引起3个时钟周期(停三个时钟周期)的阻塞,故执行⑥后,将会阻塞三个时钟周期,而不管是有条件转移指令还是无条件转移指令,至多只需要停三个时钟周期就不会发生阻塞,满足不阻塞条件

(5)①loop指令可以完整的执行IF、ID、EX、M、WB五个周期(第一条指令)

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上软件测试知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

阻塞,满足不阻塞条件

(5)①loop指令可以完整的执行IF、ID、EX、M、WB五个周期(第一条指令)

[外链图片转存中…(img-ICJwki58-1715715329196)]

[外链图片转存中…(img-di54bArX-1715715329197)]

[外链图片转存中…(img-u5vybFEE-1715715329198)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上软件测试知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

735

735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?