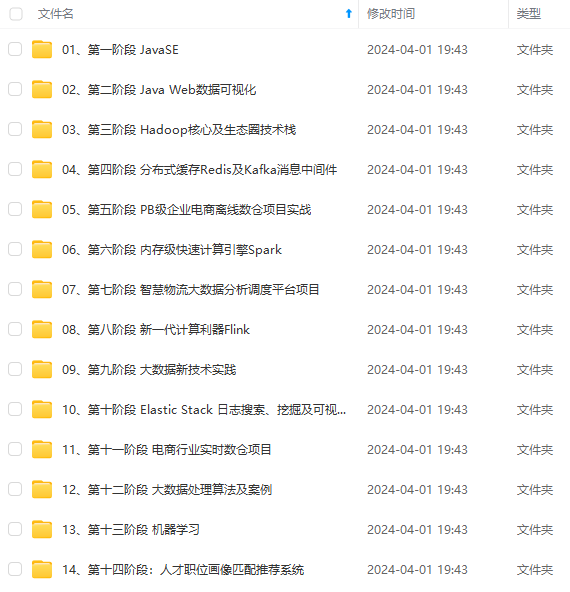

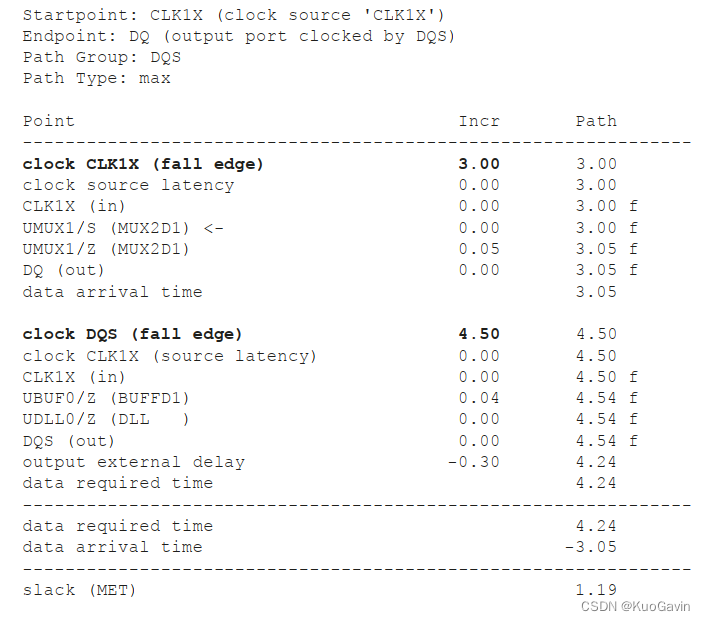

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

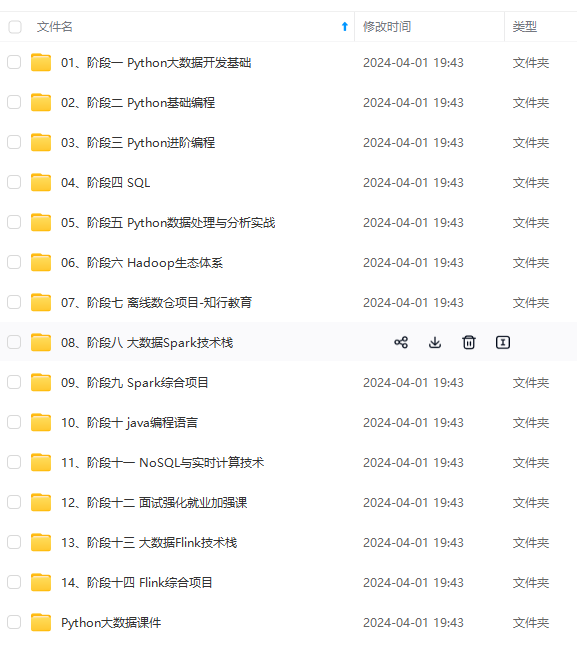

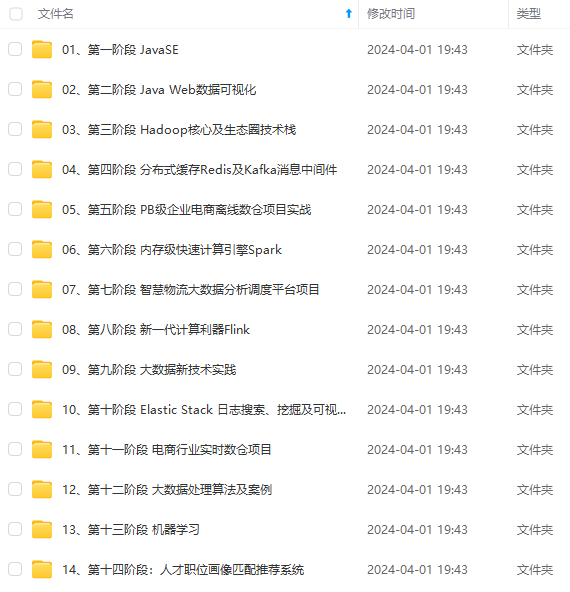

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

DQ和

D

Q

S

DQS

DQS在存储器中彼此对齐,但

D

Q

DQ

DQ和

D

Q

S

DQS

DQS选通信号也可能无法再在

D

U

A

DUA

DUA内部的存储控制器上对齐,这可能是由于

I

O

IO

IO缓冲器之间的延迟差以及

P

C

B

PCB

PCB互连走线等因素所导致的。

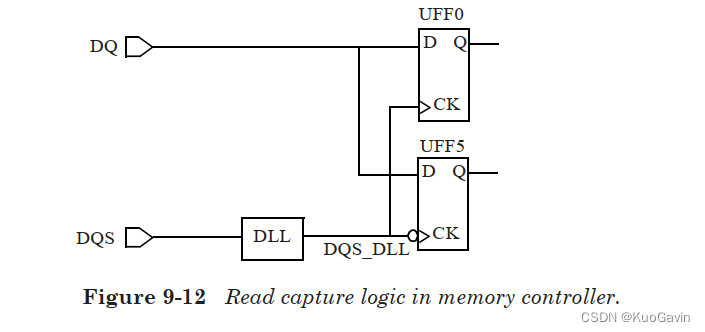

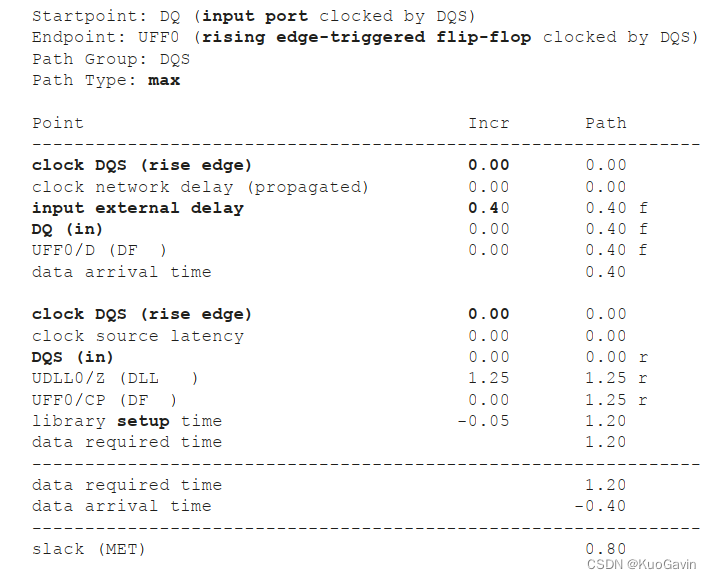

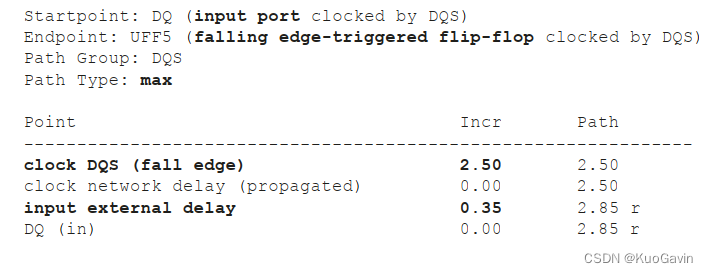

图9-12中为基本的数据读取原理图。上升沿触发的触发器在

D

Q

S

_

D

L

L

DQS\_DLL

DQS_DLL的上升沿捕获数据

D

Q

DQ

DQ,而下降沿触发的触发器在

D

Q

S

_

D

L

L

DQS\_DLL

DQS_DLL的下降沿捕获数据

D

Q

DQ

DQ。虽然图中的

D

Q

DQ

DQ路径上没有

D

L

L

DLL

DLL,但某些设计可能在数据路径上也会放置一个

D

L

L

DLL

DLL。这样可以用来延迟信号(以解决由于PVT或互连走线长度或其它差异引起的变化),以便可以在数据有效窗口的中间准确地采样数据。

为了对存储控制器上的读接口进行约束,我们在

D

Q

S

DQS

DQS上定义了一个时钟,并相对于该时钟在数据上指定了输入延迟。

create_clock -period 5 -name DQS [get_ports DQS]

假定存储器读接口以

200

M

H

z

200MHz

200MHz(当在两个时钟沿上都传输数据时相当于

400

M

b

p

s

400Mbps

400Mbps)的频率进行工作,这对应于每

2.5

n

s

2.5ns

2.5ns采样一次

D

Q

DQ

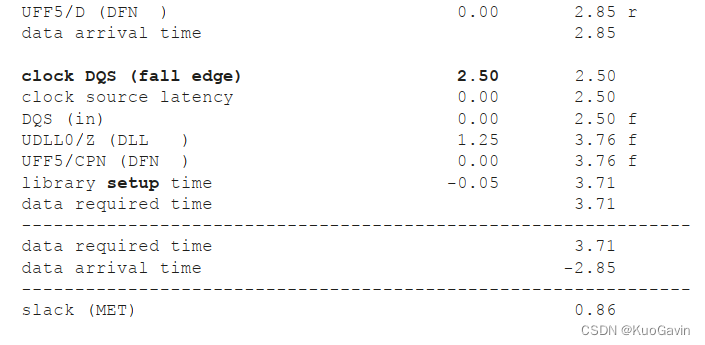

DQ数据信号。由于数据是在两个边沿上捕获的,因此需要为每个边沿分别指定输入约束。

# For rising clock edge:

set_input_delay 0.4 -max -clock DQS [get_ports DQ]

set_input_delay -0.4 -min -clock DQS [get_ports DQ]

# This is with respect to clock rising edge (default).

# Similarly for falling edge:

set_input_delay 0.35 -max -clock DQS -clock_fall \

[get_ports DQ]

set_input_delay -0.35 -min -clock DQS -clock_fall \

[get_ports DQ]

# The launch and capture are on the same edge:

set_multicycle_path 0 -setup -to UFF0/D

set_multicycle_path 0 -setup -to UFF5/D

输入延迟命令指定了

D

U

A

DUA

DUA引脚上

D

Q

DQ

DQ和

D

Q

S

DQS

DQS沿之间的延迟差,即使这两个信号通常是从存储器中同时输出的,但由于不同存储器的规格,在时序上仍会存在偏差。因此,

D

U

A

DUA

DUA内的控制器设计应考虑到两个信号之间可能存在偏斜(skew)。以下是两个触发器建立时间检查的路径报告。假设捕获触发器的建立时间要求为

0.05

n

s

0.05ns

0.05ns、保持时间要求为

0.03

n

s

0.03ns

0.03ns,且

D

L

L

DLL

DLL延迟设置为

1.25

n

s

1.25ns

1.25ns,即四分之一周期。

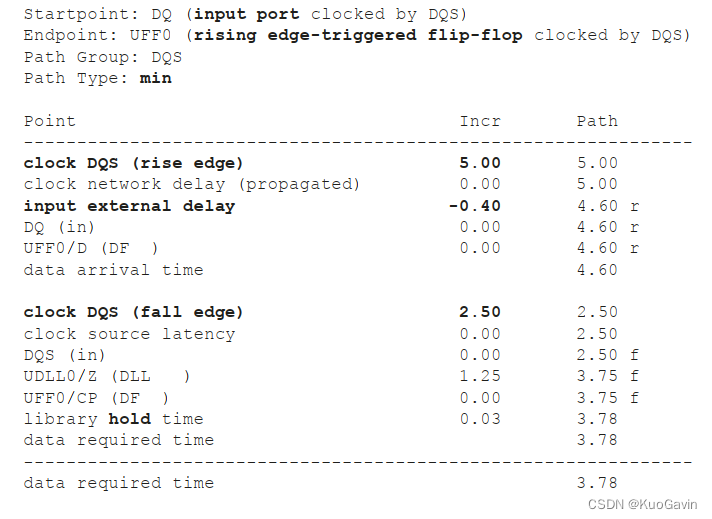

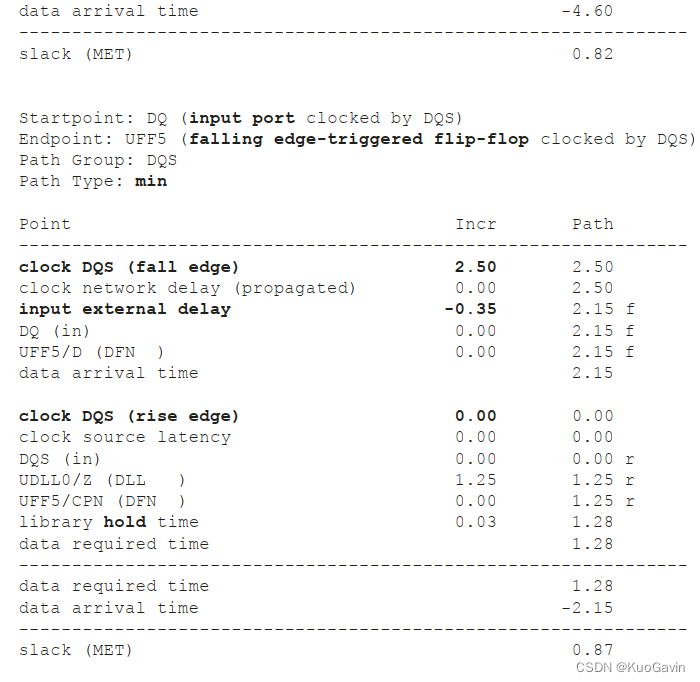

以下是保持时间检查的路径报告:

9.3.2 写周期(Write Cycle)

在写周期中,

D

Q

S

DQS

DQS沿会与从

D

U

A

DUA

DUA内存储控制器输出的

D

Q

DQ

DQ信号相差四分之一周期,因此存储器可以直接使用

D

Q

S

DQS

DQS选通脉冲去捕获数据。

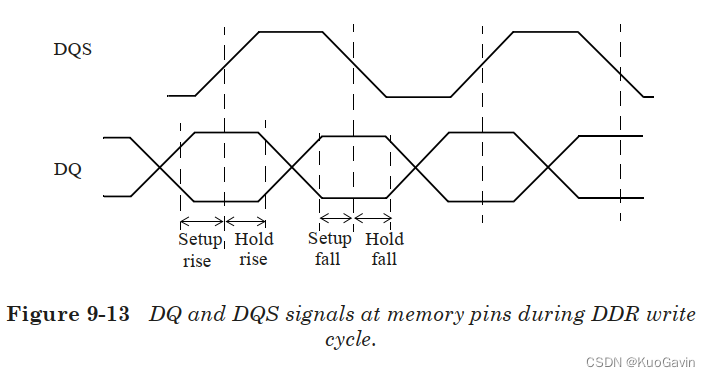

图9-13显示了存储器引脚上所需的波形,在存储器引脚处,

D

Q

S

DQS

DQS信号必须与

D

Q

DQ

DQ数据窗口的中心对齐。请注意,仍然是由于

I

O

IO

IO缓冲器延迟不匹配或者

P

C

B

PCB

PCB互连走线的变化,仅在存储控制器(

D

U

A

DUA

DUA内部)中对齐

D

Q

DQ

DQ和

D

Q

S

DQS

DQS还不足以使这些信号在

S

D

R

A

M

SDRAM

SDRAM存储器引脚处真正的对齐。因此,

D

U

A

DUA

DUA通常在写周期中使用额外的

D

L

L

DLL

DLL去进行控制,以实现

D

Q

S

DQS

DQS和

D

Q

DQ

DQ信号之间所需的四分之一周期偏移(offset)。

如何约束此模式的输出取决于控制器中时钟的生成方式,接下来我们考虑两种不同情况。

情况1:内部二倍频时钟(Case 1: Internal 2x Clock)

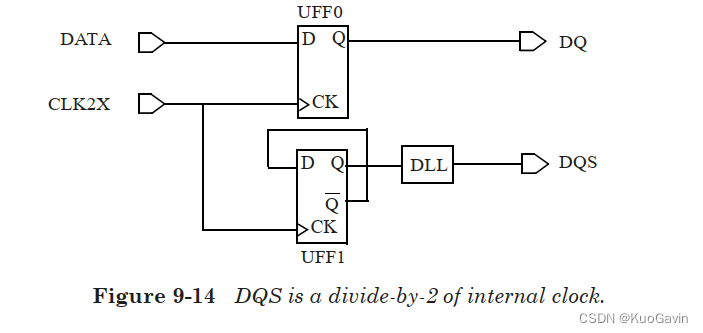

如果内部时钟是

D

D

R

DDR

DDR时钟频率的两倍,则输出逻辑可以类似于图9-14中所示。

D

L

L

DLL

DLL提供了一种必要时使

D

Q

S

DQS

DQS时钟偏斜的机制,从而满足存储器引脚上的建立时间和保持时间要求。在某些情况下,可以不使用

D

L

L

DLL

DLL,而是使用负沿触发的触发器来获得

90

90

90度的偏移。

对于图9-14中所示情况,可以进行如下输出延迟约束:

# 166MHz (333Mbps) DDR; 2x clock is at 333MHz:

create_clock -period 3 [get_ports CLK2X]

# Define a 1x generated clock at the output of flip-flop:

create_generated_clock -name pre_DQS -source CLK2X \

-divide_by 2 [get_pins UFF1/Q]

# Create the delayed version as DQS assuming 1.5ns DLL delay:

create_generated_clock -name DQS -source UFF1/Q \

-edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

D

Q

DQ

DQ输出引脚上的时序必须相对于衍生时钟

D

Q

S

DQS

DQS进行约束。

假设

D

D

R

S

D

R

A

M

DDR,, SDRAM

DDRSDRAM的

D

Q

DQ

DQ和

D

Q

S

DQS

DQS引脚之间建立时间要求分别为

D

Q

DQ

DQ上升沿的

0.25

n

s

0.25ns

0.25ns和下降沿的

0.4

n

s

0.4ns

0.4ns。类似地,假设

D

Q

DQ

DQ引脚上升沿和下降沿的保持时间要求分别为

0.15

n

s

0.15ns

0.15ns和

0.2

n

s

0.2ns

0.2ns。

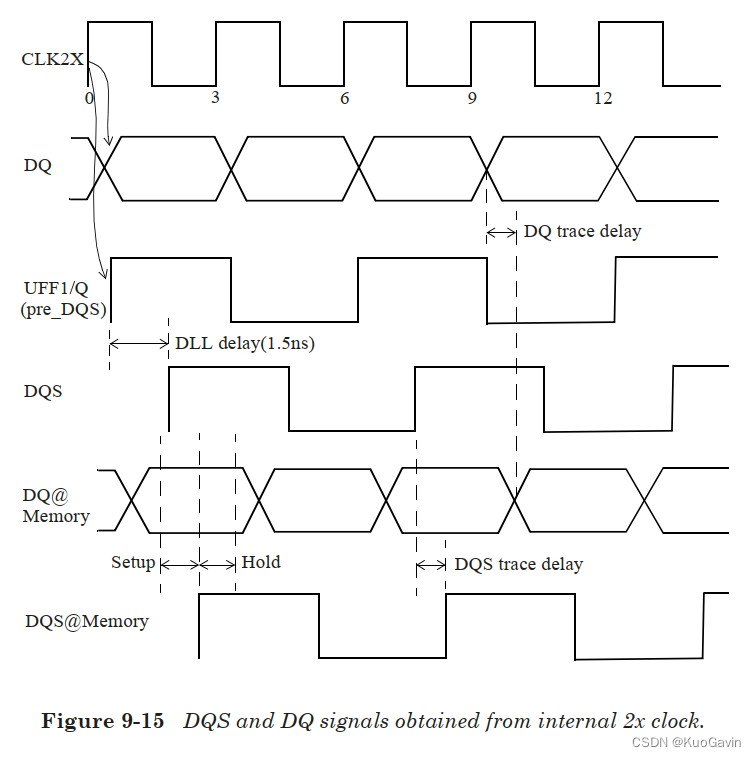

D

Q

S

DQS

DQS输出上的

D

L

L

DLL

DLL延迟已设置为四分之一周期,即

1.5

n

s

1.5ns

1.5ns,所有波形如下图9-15所示:

set_output_delay -clock DQS -max 0.25 -rise [get_ports DQ]

# Default above is rising clock.

set_output_delay -clock DQS -max 0.4 -fall [get_ports DQ]

# If setup requirements are different for falling edge of DQS,

# that can be specified by using the -clock\_fall option.

set_output_delay -clock DQS -min -0.15 -rise DQ

set_output_delay -clock DQS -min -0.2 -fall DQ

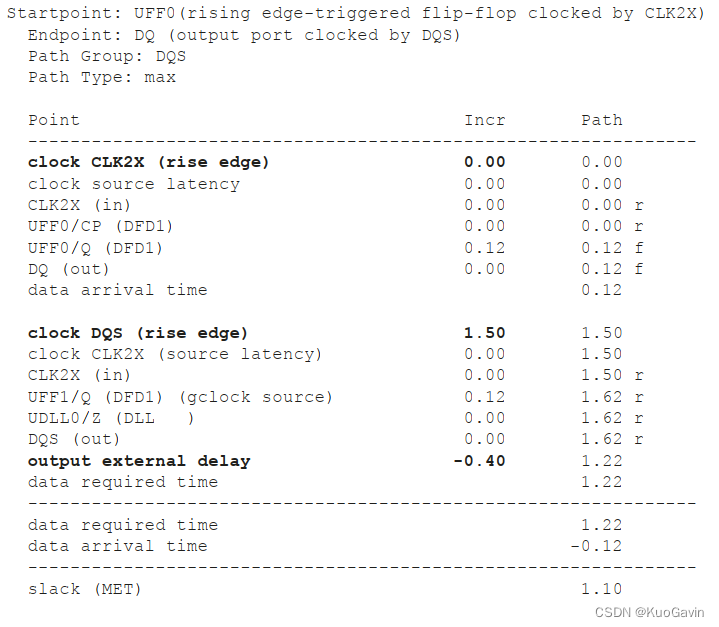

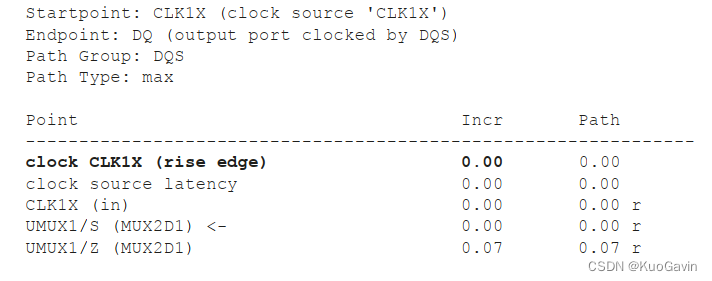

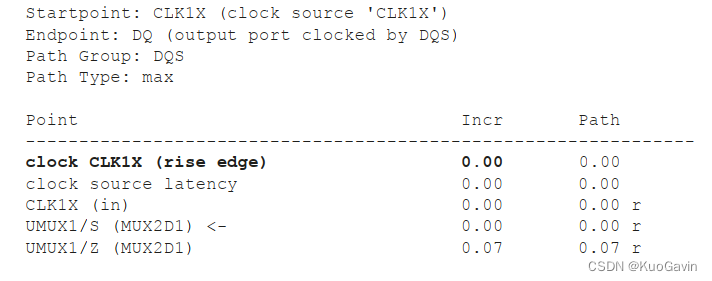

以下是通过输出

D

Q

DQ

DQ路径的建立时间检查报告。建立时间检查从

0

n

s

0ns

0ns处发起

D

Q

DQ

DQ的

C

L

K

2

X

CLK2X

CLK2X上升沿到

1.5

n

s

1.5ns

1.5ns处的

D

Q

S

DQS

DQS上升沿进行。

请注意,上述报告中的四分之一周期延迟出现在了时钟

D

Q

S

DQS

DQS上升沿的第一行中,而不是在

D

L

L

DLL

DLL实例

U

D

L

L

0

UDLL0

UDLL0的那行中。这是因为

D

L

L

DLL

DLL延迟已被建模为了衍生时钟

D

Q

S

DQS

DQS定义的一部分,而不是

D

L

L

DLL

DLL时序弧中的一部分。

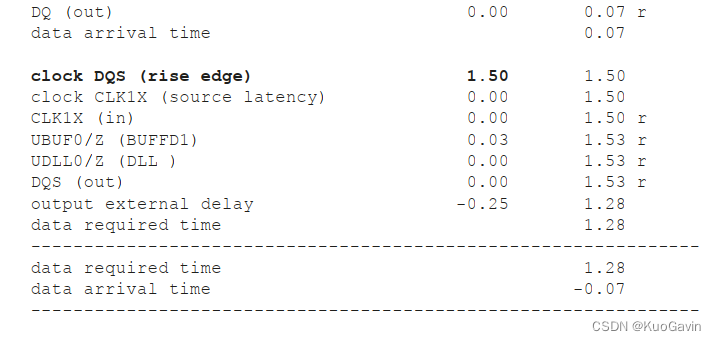

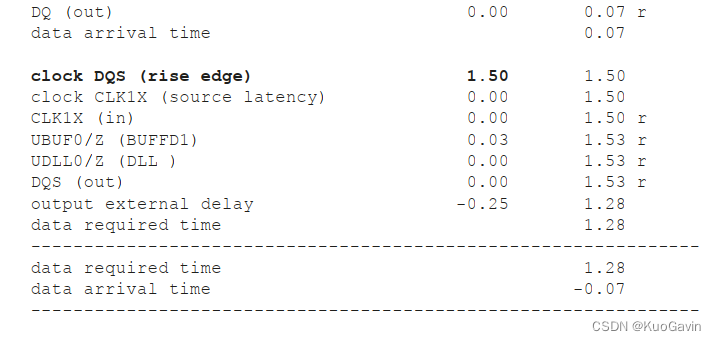

以下是通过输出

D

Q

DQ

DQ路径的保持时间检查报告。保持时间检查从

3

n

s

3ns

3ns处发起

D

Q

DQ

DQ的时钟

C

L

K

2

X

CLK2X

CLK2X上升沿到

1.5

n

s

1.5ns

1.5ns处的

D

Q

S

DQS

DQS前一个上升沿。

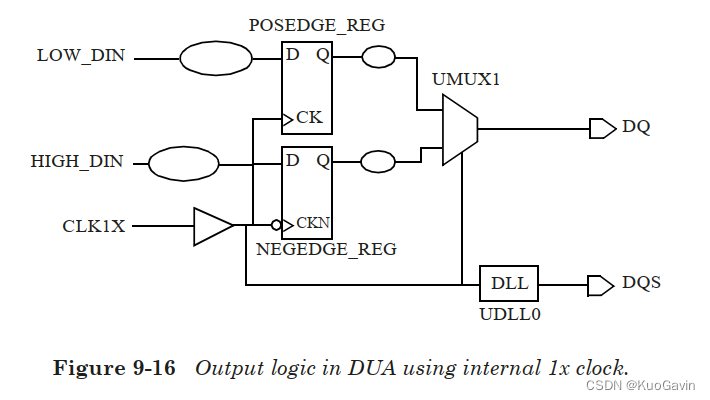

情况2:内部一倍频时钟(Case 2: Internal 1x Clock)

当内部只有一倍频时钟可用时,输出电路通常可能类似于图9-16所示的电路。

有两个触发器用于生成

D

Q

DQ

DQ数据:第一个触发器

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG由时钟

C

L

K

1

X

CLK1X

CLK1X的负沿触发,而第二个触发器

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG由时钟

C

L

K

1

X

CLK1X

CLK1X的正沿触发。每个触发器会锁存适当的边沿数据,然后使用

C

L

K

1

X

CLK1X

CLK1X作为多路复用器的选择信号来多路复用该数据:

C

L

K

1

X

CLK1X

CLK1X为高电平时,触发器

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG的输出发送到

D

Q

DQ

DQ;而当

C

L

K

1

X

CLK1X

CLK1X为低电平时,触发器

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG的输出发送到

D

Q

DQ

DQ。因此,数据会在时钟

C

L

K

1

X

CLK1X

CLK1X的两个边沿都到达输出

D

Q

DQ

DQ。请注意,每个触发器都有半个周期将数据传播到多路复用器的输入端,以确保在由

C

L

K

1

X

CLK1X

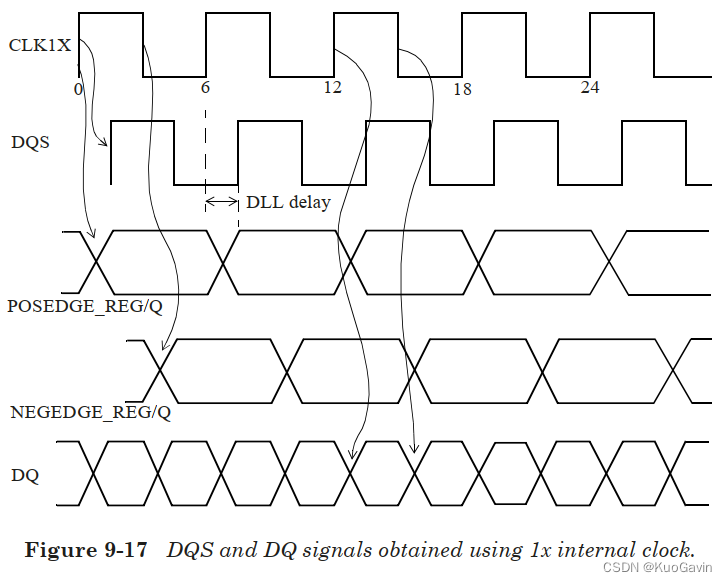

CLK1X边沿选择输入数据之前,已在多路复用器的输入端口上准备好了输入数据。相关波形如图9-17所示。

这种情况的输出延迟约束如下:

# Create the 1x clock:

create_clock -name CLK1X -period 6 [get_ports CLK1X]

# Define a generated clock at DQS. It is a divide-by-1 of

# CLK1X. Assume a quarter-cycle delay of 1.5ns on UDLL0:

create_generated_clock -name DQS -source CLK1X \

-edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

# Define a setup check of 0.25 and 0.3 between DQ and DQS

# pins on rising and falling edge of clock:

set_output_delay -max 0.25 -clock DQS [get_ports DQ]

set_output_delay -max 0.3 -clock DQS -clock_fall \

[get_ports DQ]

set_output_delay -min -0.2 -clock DQS [get_ports DQ]

set_output_delay -min -0.27 -clock DQS -clock_fall \

[get_ports DQ]

建立时间和保持时间检查可验证从多路复用器到输出的时序。建立时间检查之一是从多路复用器输入处的

C

L

K

1

X

CLK1X

CLK1X上升沿(发起

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG数据)到

D

Q

S

DQS

DQS的上升沿。另一个建立时间检查是从多路复用器输入处的

C

L

K

1

X

CLK1X

CLK1X下降沿(发起

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG数据)到

D

Q

S

DQS

DQS的下降沿。同样,保持时间检查是从(与建立时间检查)相同的

C

L

K

1

X

CLK1X

CLK1X边沿到

D

Q

S

DQS

DQS的前一个下降沿或上升沿。

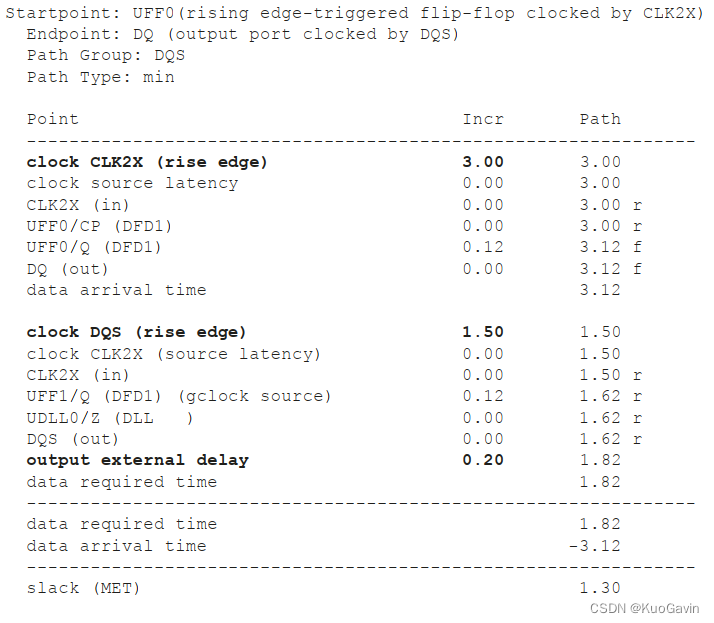

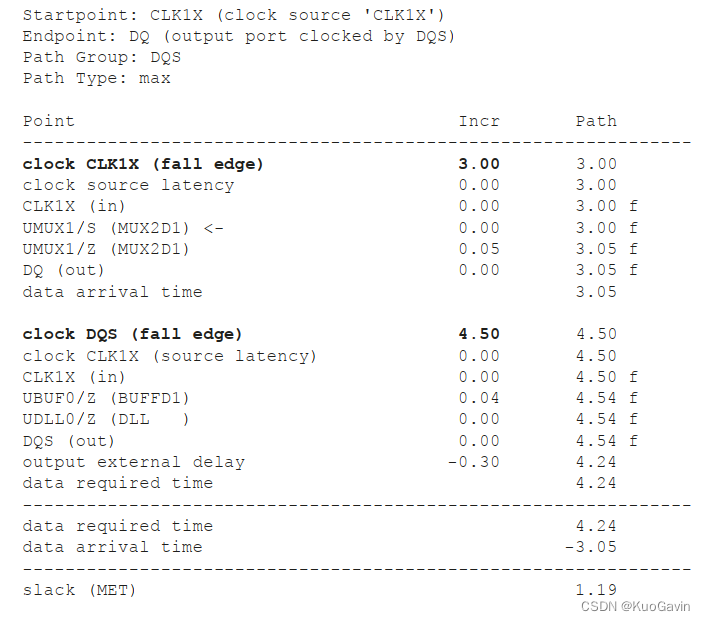

以下是通过

D

Q

DQ

DQ端口的建立时间检查报告,该检查在(选择输出

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的上升沿之间进行。

这是通过

D

Q

DQ

DQ端口的另一个建立时间检查报告,该检查在(选择输出

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的下降沿和

D

Q

S

DQS

DQS的下降沿之间进行。

这是通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的前一个下降沿之间进行。

这是另一个通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

是从多路复用器输入处的

C

L

K

1

X

CLK1X

CLK1X下降沿(发起

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG数据)到

D

Q

S

DQS

DQS的下降沿。同样,保持时间检查是从(与建立时间检查)相同的

C

L

K

1

X

CLK1X

CLK1X边沿到

D

Q

S

DQS

DQS的前一个下降沿或上升沿。

以下是通过

D

Q

DQ

DQ端口的建立时间检查报告,该检查在(选择输出

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的上升沿之间进行。

这是通过

D

Q

DQ

DQ端口的另一个建立时间检查报告,该检查在(选择输出

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的下降沿和

D

Q

S

DQS

DQS的下降沿之间进行。

这是通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的前一个下降沿之间进行。

这是另一个通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

[外链图片转存中…(img-UnvvAV0o-1715060687968)]

[外链图片转存中…(img-VDQ2HvPP-1715060687968)]

[外链图片转存中…(img-dUqZFvgx-1715060687968)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?