既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

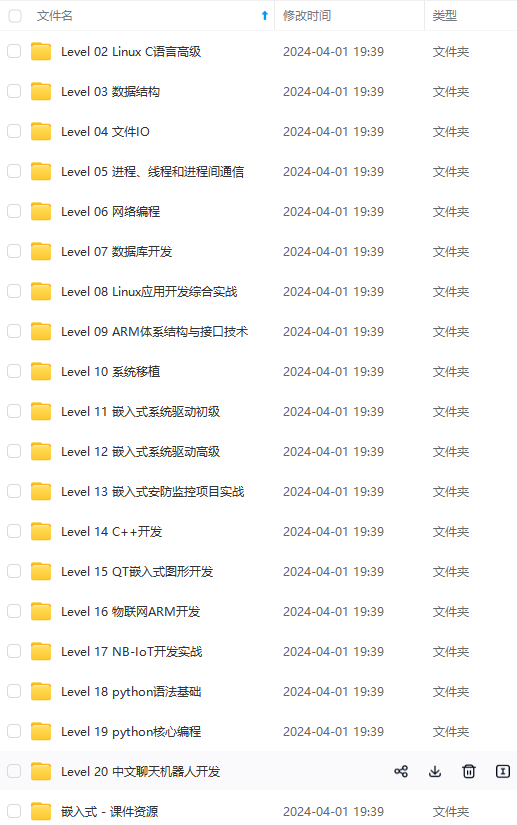

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

//提取显示数值所对应的十进制数的各个位

assign data0 = data[3:0]; // 个位数

assign data1 = data[7:4]; // 十位数

assign data2 = data[11:8]; // 百位数

assign data3 = data[15:12]; // 千位数

always @(posedge sys_clk or negedge sys_rest) begin

if(!sys_rest)

begin

CNT_NUM<=4’d0;

CLK<=1’d1;

end

else if(CNT_NUM<=CLK_NUM/2-1’b1)

begin

CLK<=~CLK;

CNT_NUM<=4’d0;

end

else

begin

CNT_NUM<=CNT_NUM+1;

CLK<=CLK;

end

end

always @(posedge CLK or negedge sys_rest) begin

if(!sys_rest)

num<=16’d0;

else

begin

num[15:12] <= data3; //则依次给4位数码管赋值

num[11:8] <= data2;

num[ 7:4] <= data1;

num[ 3:0] <= data0;

end

end

always @(posedge CLK or negedge sys_rest) begin //产生1ms脉冲

if(!sys_rest)

begin

MSCNT<=13’d0;

MS_flag<=1’b0;

end

else if(MSCNT==MSNUM-1)

begin

MSCNT<=13’d0;

MS_flag<=1’b1;

end

else

begin

MSCNT<=MSCNT+1;

MS_flag<=1’b0;

end

end

always @(posedge CLK or negedge sys_rest) begin

if(!sys_rest)

sel_num<=0;

else if(MS_flag)

begin

if(sel_num<3’d3)

sel_num<=sel_num+1;

else

sel_num<=0;

end

else

sel_num<=sel_num;

end

always @(posedge CLK or negedge sys_rest) begin

if(!sys_rest)

sel<=4’b1111;

else

begin

case(sel_num)

3’d0: begin

sel<= 4’b1110; //显示数码管最低位

num_display<=num[3:0];

end

3’d1: begin

sel<= 4’b1101; //显示数码管第1位

num_display<=num[7:4];

end

3’d2: begin

sel<= 4’b1011; //显示数码管第2位

num_display<=num[11:8];

end

3’d3: begin

sel<= 4’b0111; //显示数码管第3位

num_display<=num[15:12];

end

default sel<= 4’b1111;

endcase

end

end

always @(posedge CLK or negedge sys_rest) begin

if(!sys_rest)

seg_led<=7’b100000;

else

begin

case(num_display)

4’h0 : seg_led <= 7’b1000000;

4’h1 : seg_led <= 7’b1111001;

4’h2 : seg_led <= 7’b0100100;

4’h3 : seg_led <= 7’b0110000;

4’h4 : seg_led <= 7’b0011001;

4’h5 : seg_led <= 7’b0010010;

4’h6 : seg_led <= 7’b0000010;

4’h7 : seg_led <= 7’b1111000;

4’h8 : seg_led <= 7’b0000000;

4’h9 : seg_led <= 7’b0010000;

4’d10: seg_led <= 7’b1111111; //不显示任何字符

default : seg_led <= 7’b1000000;

endcase

end

end

endmodule

**既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!**

**由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

**[如果你需要这些资料,可以戳这里获取](https://bbs.csdn.net/topics/618679757)**

**由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

**[如果你需要这些资料,可以戳这里获取](https://bbs.csdn.net/topics/618679757)**

2650

2650

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?