Makefile基础结构

- 规则语法

target: prerequisites

command

target:生成的目标(如可执行文件、.o文件)

prerequisites:依赖项(源码、头文件等)

command:构建命令(必须用Tab缩进)

示例:

makefile

hello: hello.c

gcc -o hello hello.c

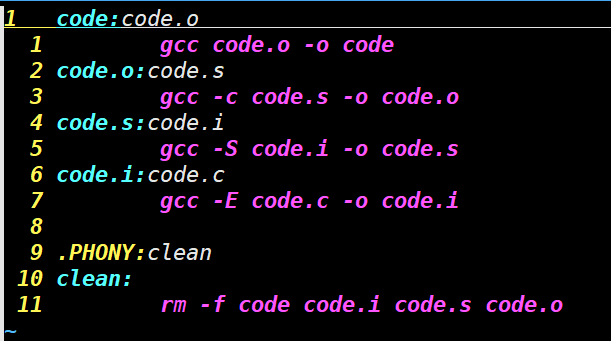

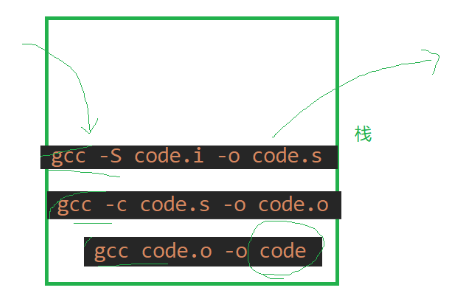

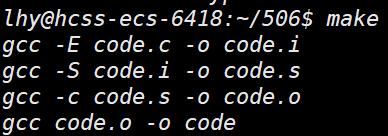

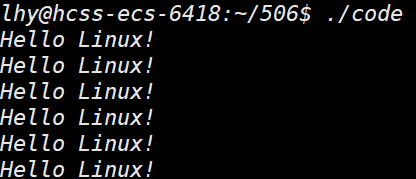

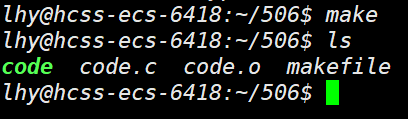

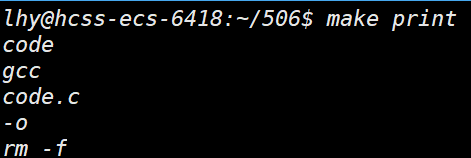

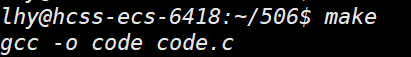

下面是模拟gcc编译文件的过程

其原理类似于一个栈,通过查找依赖文件,逐个生成

变量定义与使用

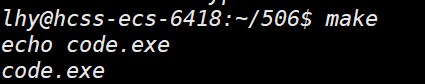

@默认不回显

BIN=code

CC = gcc

SRC=code.c

FLAGS=-o

RM=rm -f

$(BIN):$(SRC)

$(CC) $(FLAGS) $(BIN) $(SRC)

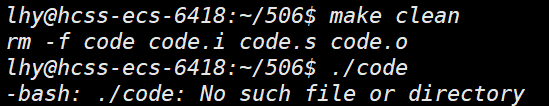

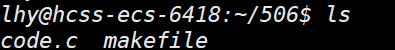

.PHONY:clean

clean:

$(RM) $(BIN)

.PHONY:print

print:

@echo $(BIN)

@echo $(CC)

@echo $(SRC)

@echo $(FLAGS)

@echo $(RM)

预定义变量:$ @(目标名//冒号左边)、$ ^(所有依赖//冒号右边)、$<(遍历依赖)用于目录里有很多个.c文件需要编译时使用

所以上面可以优化为:

BIN=code

CC=gcc

SRC=$(wildcard *.c) #自动识别.c结尾文件

OBJ=$(SRC:.c=.o) #自动生成.o文件

LFLAGS=-o

CFLAGS=-c

RM=rm -f

$(BIN):$(SRC)

$(CC) $(LFLAGS) $@ $^

%.o:%.c# 等价于code1.o,code2.o.....:code1.c,code2.c......

$(CC) $(CFLAGS) $< #自动遍历所有.c文件

.PHONY:clean

clean:

$(RM) $(BIN) $(OBJ)

赋值方式:=(延迟展开):=(立即展开)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?