目录

1、计算机的工作步骤

用计算机解决一个实际问题通常包含两个步骤,一个是上机前的各种准备,另一个是上机运行。

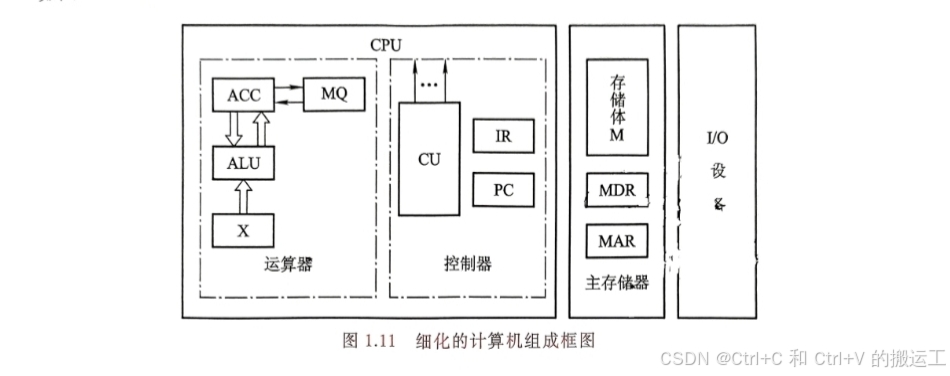

为了更形象的了解计算机的工作过程,我们需要一个详细的计算机组成框图:

上机前准备(人工准备):

-

数学模型构建:将实际问题抽象为数学表达式(如三角函数运算y=sin(x)y=sin(x)、线性方程ax+b=cax+b=c等)明确变量关系,用等式/不等式描述问题。

-

计算方法确定:选择适合计算机实现的算法(如解方程时优先选迭代法而非解析法)。计算机擅长重复计算,迭代法通过逼近逐步求解更高效。

-

解题程序编制(核心步骤):

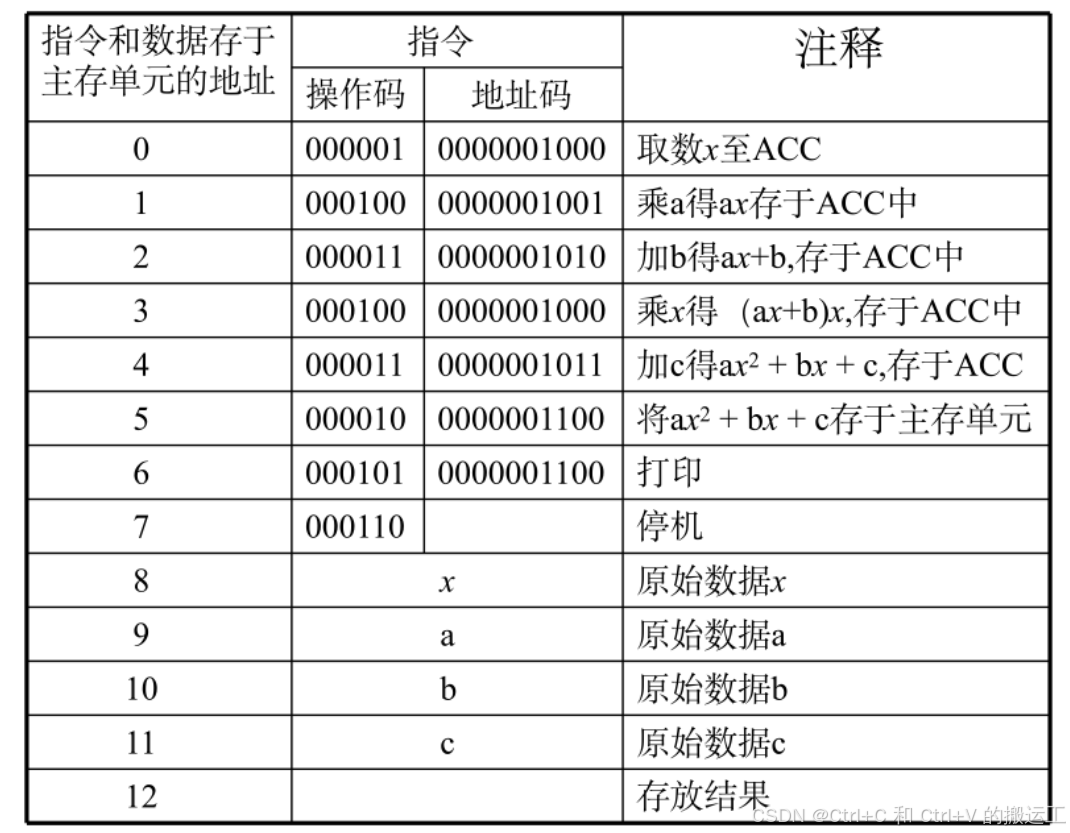

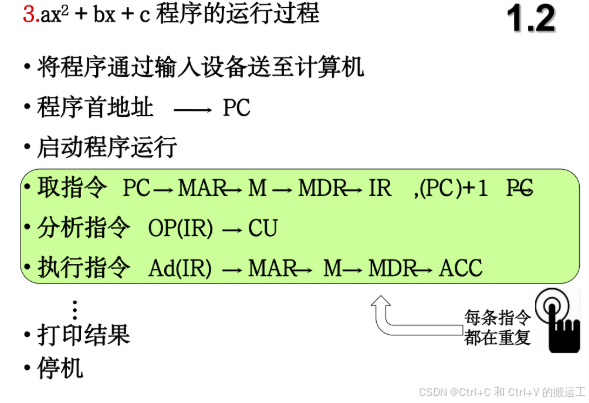

例如,计算,可以分解一下步骤:

- 读取输入:将

存入运算器

- 计算二次项:

(运算器存储结果)

- 叠加一次项:

- 乘

完成平方:

- 加常数项:

将上述的运算步骤写成某计算机一一对应的机器指令,就完成了运算程序的编写。

2、计算机的组成部件和操作过程

2、计算机的组成部件和操作过程

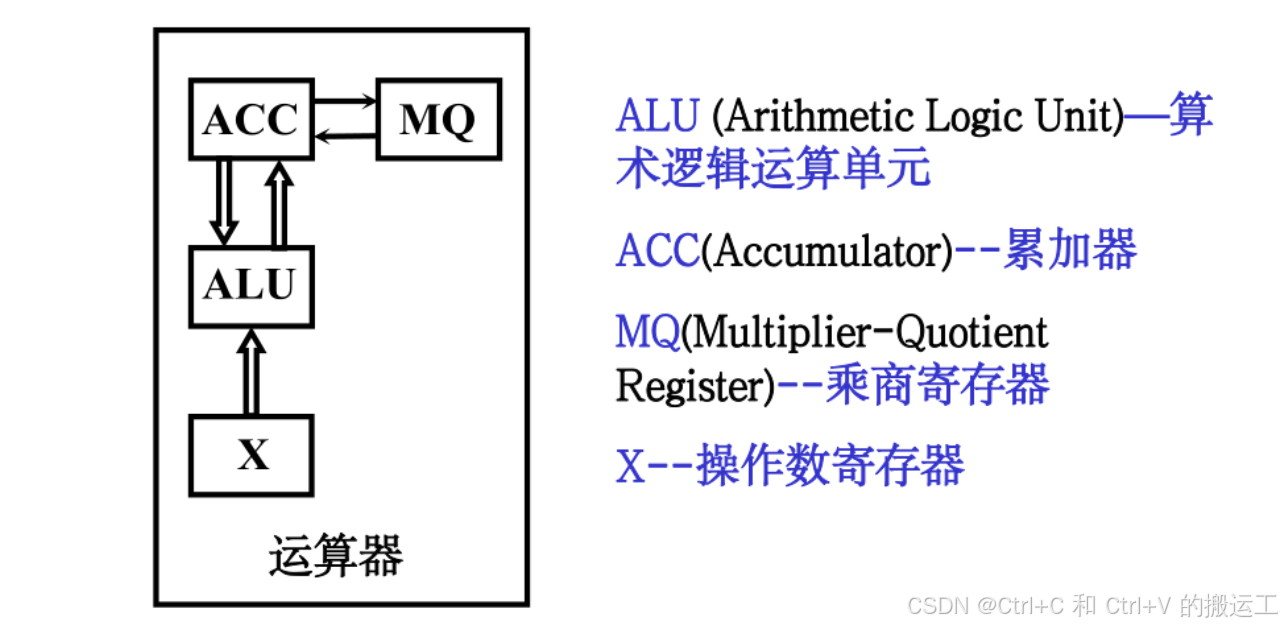

2.1、运算器

2.1.1、核心部件作用

-

ACC(累加器 Accumulator)

功能:存储运算的中间结果和最终结果。

操作中角色:在加减法时直接参与运算,乘除法时存放结果的高位或余数。 -

MQ(乘商寄存器 Multiplier-Quotient Register)

功能:乘法时存放乘数,除法时存放商;乘/除结束后存储结果的低位。

操作中角色:乘除运算时与ACC配合完成多步操作。 -

X(操作数寄存器 Operand Register)

功能:临时存放参与运算的操作数(如被加数、被减数等)。

操作中角色:提供第二操作数,与ACC或MQ联动。 -

ALU(算术逻辑单元 Arithmetic Logic Unit)

|功能:执行所有算术(加减乘除)和逻辑(与或非)运算。

操作中角色:接收ACC、X或MQ的数据,计算结果后回传至ACC或MQ。

2.1.2、操作过程(加减乘除)

记忆口诀:加法减法靠ACC,乘商MQ来接力;操作数用X暂存,ALU算完再传递。乘法右移商左移,余数恢复要注意。

-

加法操作:

(1) 被加数存入ACC,加数存入x

(2) ALU执行 ACC + X → ACC

示例:ACC初始存5,X存3 → ALU计算5+3=8→ ACC更新为8 -

减法操作:

(1) 被减数存入ACC,减数存入X

(2) ALU执行 ACC - X → ACC

示例:ACC存10,X存4 → ALU计算10−4=6 → ACC更新为6 -

乘法操作(以定点原码乘法为例)

(1) 初始化: 被乘数存入X(固定不可改); 乘数存入MQ(右移提供控制位); ACC清零(用于累加部分积)

(2) 循环判断: 检查MQ最低位→ 为1:ACC += X(加被乘数); 为0:保持ACC不变

(3) 联合右移: ACC与MQ整体右移1位: ACC最低位移入MQ最高位, MQ最低位丢弃

(4) 终止条件: 重复步骤2-3直至MQ处理完成, 最终结果高位存于ACC,低位存MQ

案例1:2×2(二进制:0010 × 0010)步骤 操作 X (被乘数) ACC (累加器) MQ (乘数/低位结果) 说明 0 初始化 10 00 10 被乘数存X,乘数存MQ 1 检查MQ最低位为0 10 00 10 不加,直接右移 ACC与MQ联合右移 10 00 01 ACC=0000→0000,MQ右移1位 2 检查MQ最低位为1 10 00+10=10 01 加被乘数到ACC ACC与MQ联合右移 10 01 00 ACC=0010→0001,MQ右移1位 结果:高位ACC=01(1),低位MQ=00(0) → 合并结果:0100(4)

案例2:2×3(二进制:0010 × 0011)

结果:高位ACC=0000(0),低位MQ=0110(6) → 合并结果:0110(6)步骤 操作 X (被乘数) ACC (累加器) MQ (乘数/低位结果) 说明 0 初始化 0010 0000 0011 被乘数存X,乘数存MQ 1 检查MQ最低位为1 0010 0000+0010=0010 0011 加被乘数到ACC ACC与MQ联合右移 0010 0001 1001 ACC=0010→0001,MQ右移1位 2 检查MQ最低位为1 0010 0001+0010=0011 1001 再次加被乘数到ACC ACC与MQ联合右移 0010 0001 1100 ACC=0011→0001,MQ右移1位 3 检查MQ最低位为0 0010 0001 1100 不加,直接右移 ACC与MQ联合右移 0010 0000 1110 ACC=0001→0000,MQ右移1位 4 检查MQ最低位为0 0010 0000 1110 不加,直接右移 ACC与MQ联合右移 0010 0000 0111 ACC=0000→0000,MQ右移1位 -

除法操作(以恢复余数法为例)

(1) 被除数存入ACC和MQ(高位在ACC,低位在MQ)

(2) ACC与X(存除数)比较:

若 ACC ≥ X,商1,执行 ACC - X → ACC

若 ACC < X,商0,不减法

(3) ACC与MQ联合左移1位,重复直到商位数足够

(4) 最终商在MQ,余数在ACC

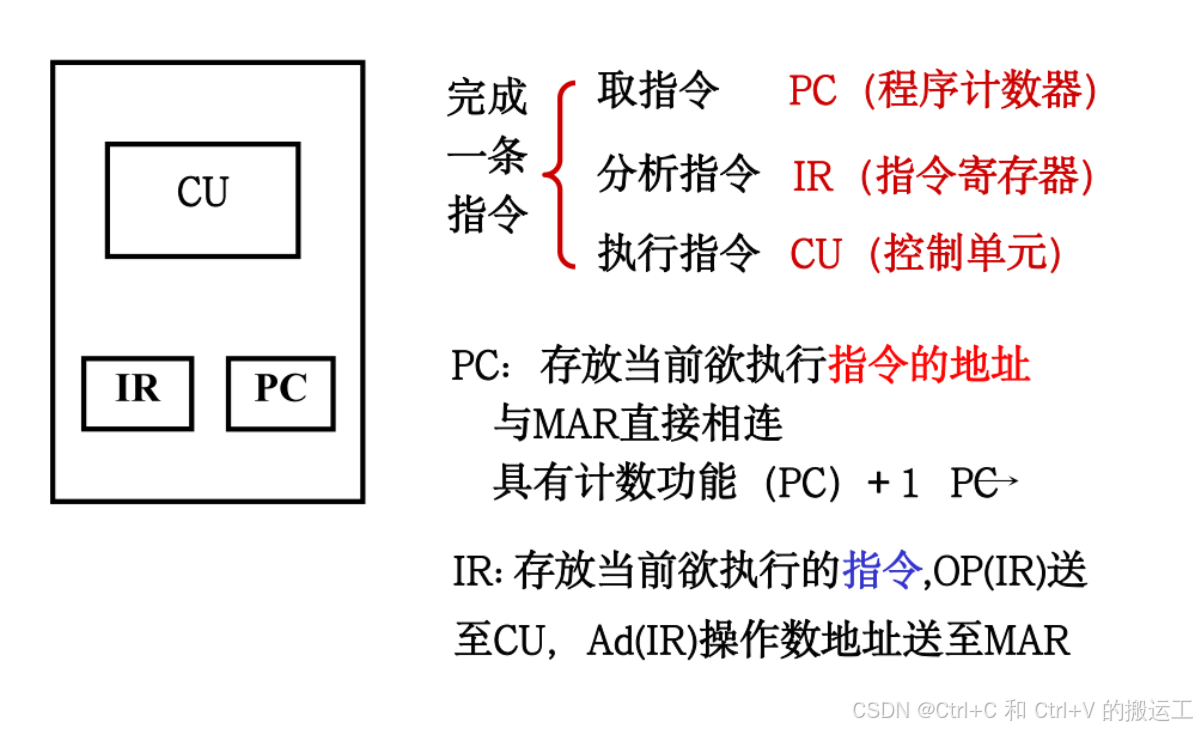

2.2、控制器

| 部件 | 名称 | 核心作用 | 关键特性 |

|---|---|---|---|

| CU | 控制单元 | 解析指令并生成控制信号,协调CPU各部件工作 | - 时序控制(时钟周期管理) - 微操作信号生成(如ALU使能、寄存器读写) |

| IR | 指令寄存器 | 存储当前正在执行的指令 | - 保存操作码(操作类型)和操作数地址 - 直接连接CU,提供解码依据 |

| PC | 程序计数器 | 存放下一条待执行指令的内存地址 | - 自动递增(顺序执行时) - 支持跳转(分支/调用指令时更新地址) |

- CU:CPU的“大脑”,驱动所有操作

- IR:指令执行的“依据”

- PC:程序执行的“导航指针”

三者协同完成取指 → 译码 → 执行 → 更新的循环,构成冯·诺依曼架构的核心控制逻辑。

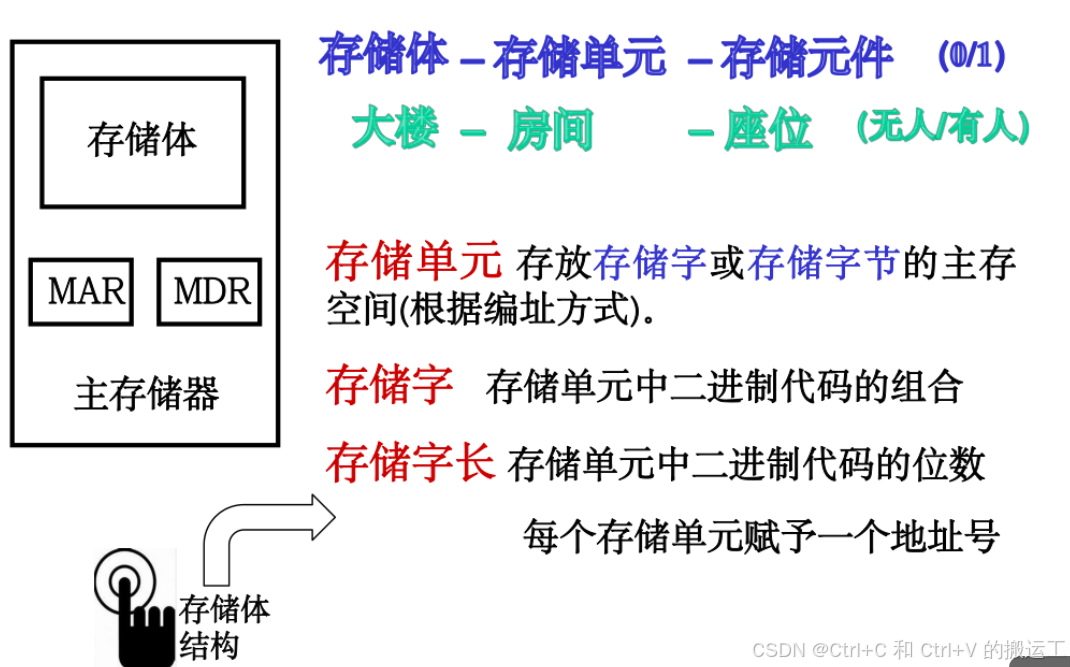

2.3、主存储器

| 部件 | 全称 | 作用 | 关键特性 |

|---|---|---|---|

| 存储体 | 存储体 | 由存储单元组成,存储二进制数据(程序、数据) | 容量由存储单元数量×字长决定 |

| MAR | 存储器地址寄存器 | 存放CPU要访问的存储单元地址,控制存储体寻址 | 位数决定最大可寻址空间(如32位→4GB) |

| MDR | 存储器数据寄存器 | 暂存从存储体读出或写入的数据,作为CPU与存储体间的数据缓冲 | 位数通常与计算机字长一致(如64位) |

工作流程

-

寻址:CPU将目标地址存入MAR→ 存储体根据MAR定位单元

-

读操作:存储体将数据送入MDR → CPU从MDR读取

-

写操作:CPU将数据存入MDR → 存储体按MAR地址写入MDR数据

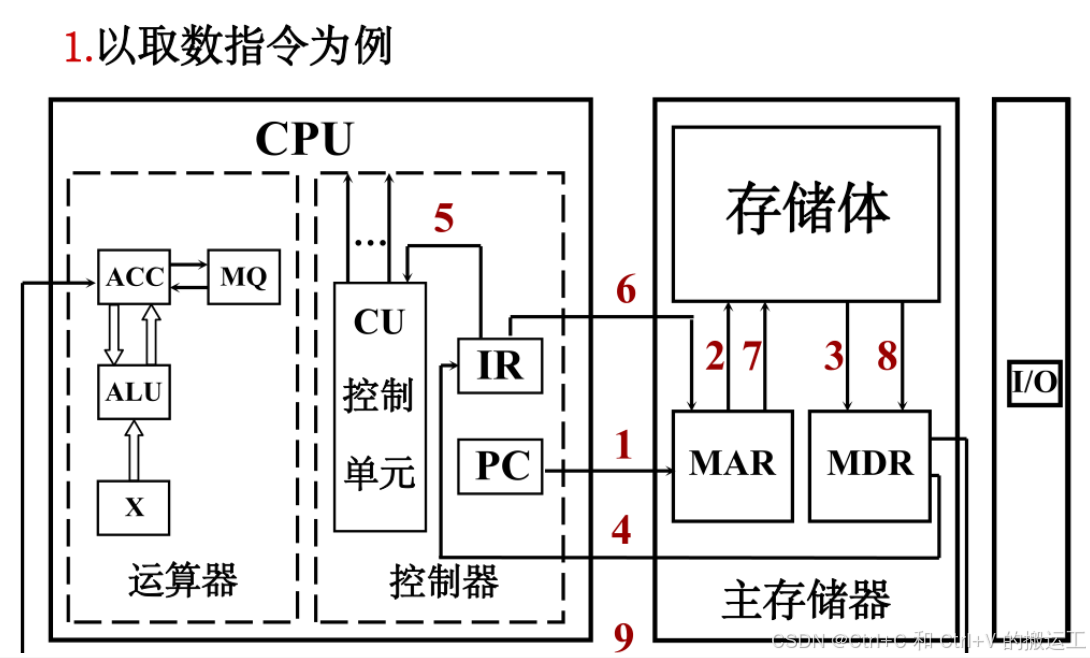

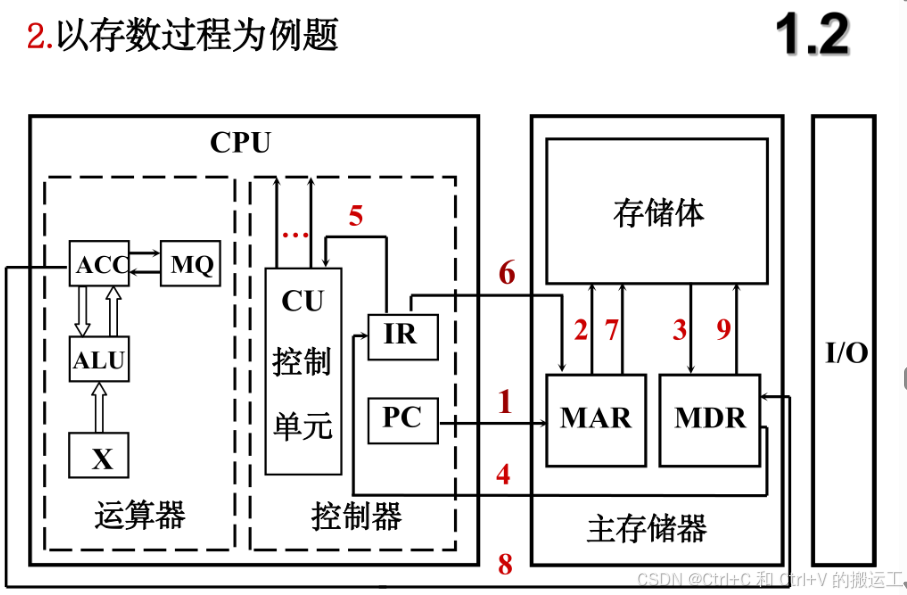

2.4、主机指令过程

3、计算机硬件主要技术指标

3、计算机硬件主要技术指标

3.1、机器字长

定义:CPU一次能处理的二进制位数(单位:bit)。

核心作用:

- 数据精度:字长越长,单次运算的数据范围越大(如32位可表示

个整数)

- 性能影响:字长直接关联寄存器位数、ALU宽度及数据总线宽度

- 兼容性:字长决定操作系统和软件的适配性(如64位系统需64位CPU支持)

| 典型值 | 应用场景 | 示例 |

|---|---|---|

| 32位 | 早期个人电脑、嵌入式 | Intel 80386处理器 |

| 64位 | 现代计算机、服务器 | AMD Ryzen 9 5950X |

| 128位 | 高性能计算、加密运算 | IBM z13大型机 |

3.2、存储容量

定义:计算机存储设备能保存的二进制信息总量,分为主存容量和辅存容量。

| 存储类型 | 单位换算 | 计算公式 | 示例说明 |

|---|---|---|---|

| 主存 | 1GB= | 容量=存储单元数×存储字长 | 16GB内存可存储约16亿字节 |

| 辅存 | 1TB= | 容量=扇区数×磁道数×盘面数 | 1TB硬盘≈1万亿字节存储 |

最大寻址空间:由地址总线位数决定,例如:

- 32位地址总线 → 最大

=4GB寻址空间

- 64位地址总线 → 理论

=16EB(实际受操作系统限制)

3.3、运算速度

定义:计算机单位时间内完成指令或操作的数量,需综合多项指标评估:

| 指标 | 计算公式 | 说明 | 典型值示例 |

|---|---|---|---|

| 主频 | CPU时钟频率(单位:GHz) | 每秒脉冲周期数,决定指令执行节奏 | Intel i7-12700:3.6GHz |

| CPI | 时钟周期数/指令 | 单条指令耗时,CPI越小速度越快 | RISC架构CPU:CPI≈1 |

| MIPS | 百万条指令/秒 | MIPS=主频CPIMIPS=CPI主频 | 3.6GHz CPU:≈3600 MIPS |

| FLOPS | 浮点运算次数/秒 | 衡量科学计算能力 | NVIDIA A100:19.5 TFLOPS |

速度提升技术:

- 流水线技术:并行处理多条指令(如5级流水线)

- 多核并行:多核CPU同时执行任务(如8核16线程)

- 缓存优化:L1/L2/L3缓存减少内存访问延迟

总结(综合性能关系)

| 指标 | 对性能影响方向 | 典型瓶颈场景 |

|---|---|---|

| 字长长 | ↑ 精度/并行度,↑ 硬件成本 | 大规模数据处理、加密解密 |

| 容量大 | ↑ 可运行程序规模,↓ 响应速度 | 多任务操作、大型软件加载 |

| 速度快 | ↑ 实时性,↑ 功耗与发热 | 游戏渲染、AI模型训练 |

注:实际性能需三者协同优化,例如64位CPU(字长)配合32GB内存(容量)和5GHz主频(速度)可满足高端图形设计需求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?