本文主要记录我的ADS1299芯片学习笔记,供日后复习使用。

文章目录

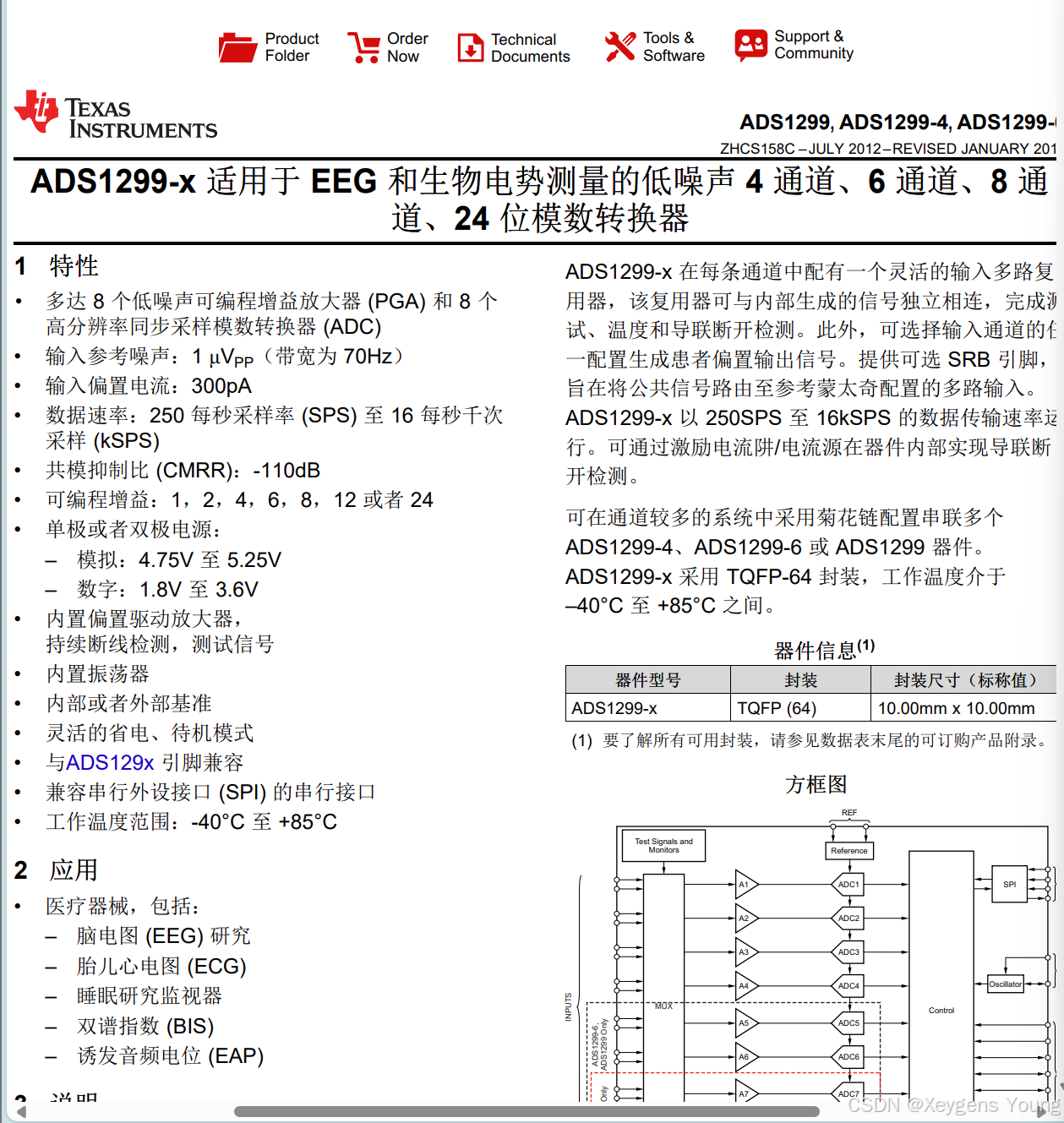

前言:ADS1299是什么?

提示:这里可以添加本文要记录的大概内容:

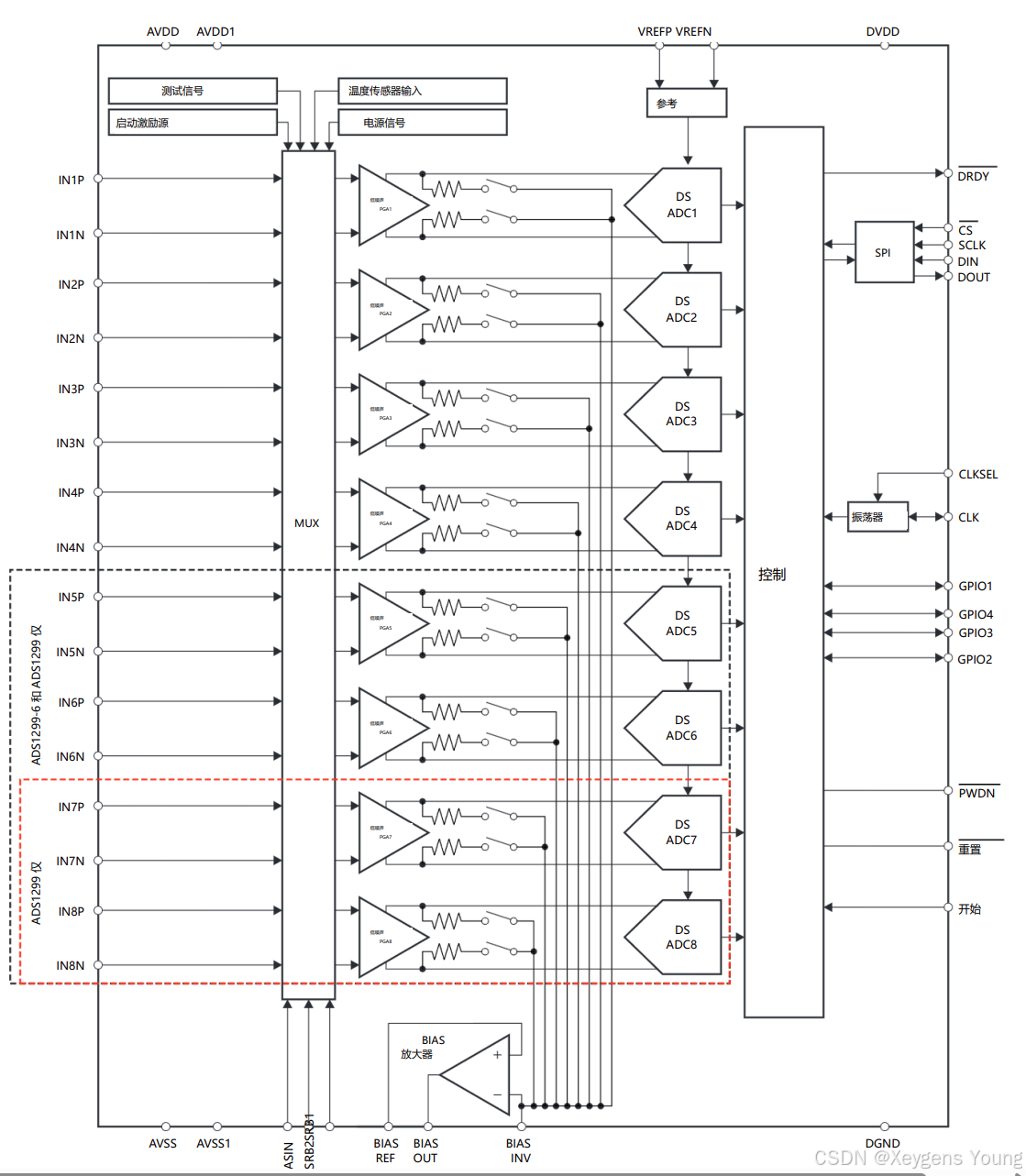

ADS1299适用于 EEG 和生物电势测量的低噪声 8通道24 位模数转换器, 其24位高分辨率和低噪声特性,能够精确采集脑电信号,确保数据的高质量。

特性

- 低噪声 PGA:增益:1 /2/4/6/8/12/24。

- 高分辨率 ADC:采样率:250 SPS 至 16 kSPS

- 内置参考电压源:4.5V 内部参考电压源,可选择内部或外部参考。

- 时钟:内部时钟/外部时钟

- 偏置驱动放大器:减少共模干扰,提高测量精度。

- 脱落检测:支持DC和AC脱落检测。

- 灵活的MUX:支持多种输入信号源,包括测试信号、温度传感器信号等。

- 两种转换模式:Continuous/single-shot

一、目录

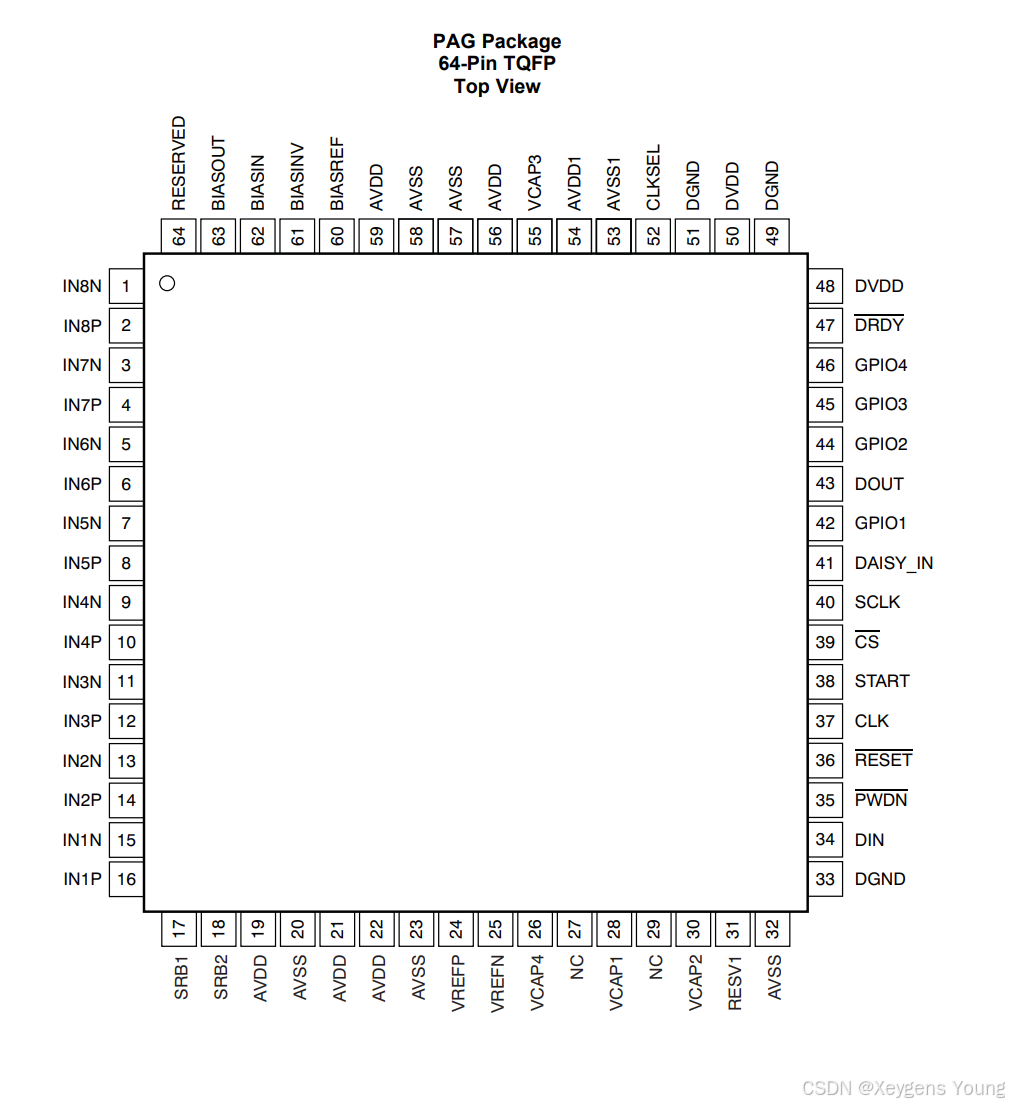

1. 引脚分布及使用

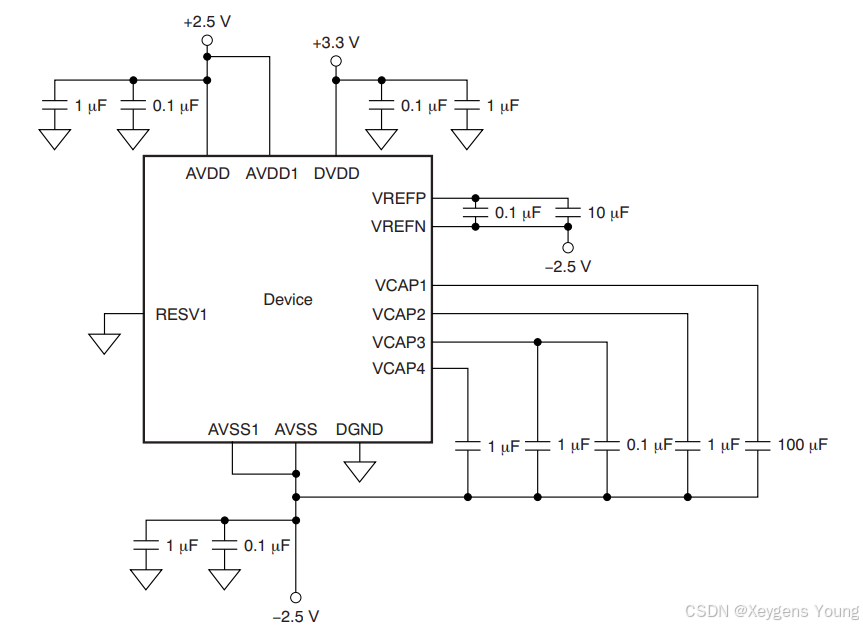

1. 电源

AVDD:模拟正极 +2.5V

AVDD1:为电荷泵提供电源,与AVDD相连

AVSS:模拟地-2.5V

AVSS: 同AVDD1

DVDD 3.3V

DGND 数字地

VREFP:参考电压正

VREFN:参考电压负

VCAP1 VCAP2 VCAP3 VCAP4:与旁路电容相连,有助于稳定电压

2. 电极:

INXP:差分模拟真输入

INXN:差分模拟负输入

3. BIAS偏置

BIASIN:偏置输入至MUX

~INV:反向输入

~OUT:驱动输出

~REF:参考电压输入

4. GPIOX:

GPIOA GPIOB GPIOC GPIOD

5. 串口:

DIN:串行数据输入

DOUT:串行数据输出

CS:芯片选择

START:开机

RESET:重启

DRDY:data ready,低电平表示数据可读

SCLK:串口时钟

CLKSEL:时钟选择引脚

PWDN:Power Down 省电模式引脚

6. 其他引脚:

DAISY_IN:菊花链引脚

SPB1 SPB2:刺激参考偏置多功能引脚

7. 保留引脚:

NC REERVED:保留引脚

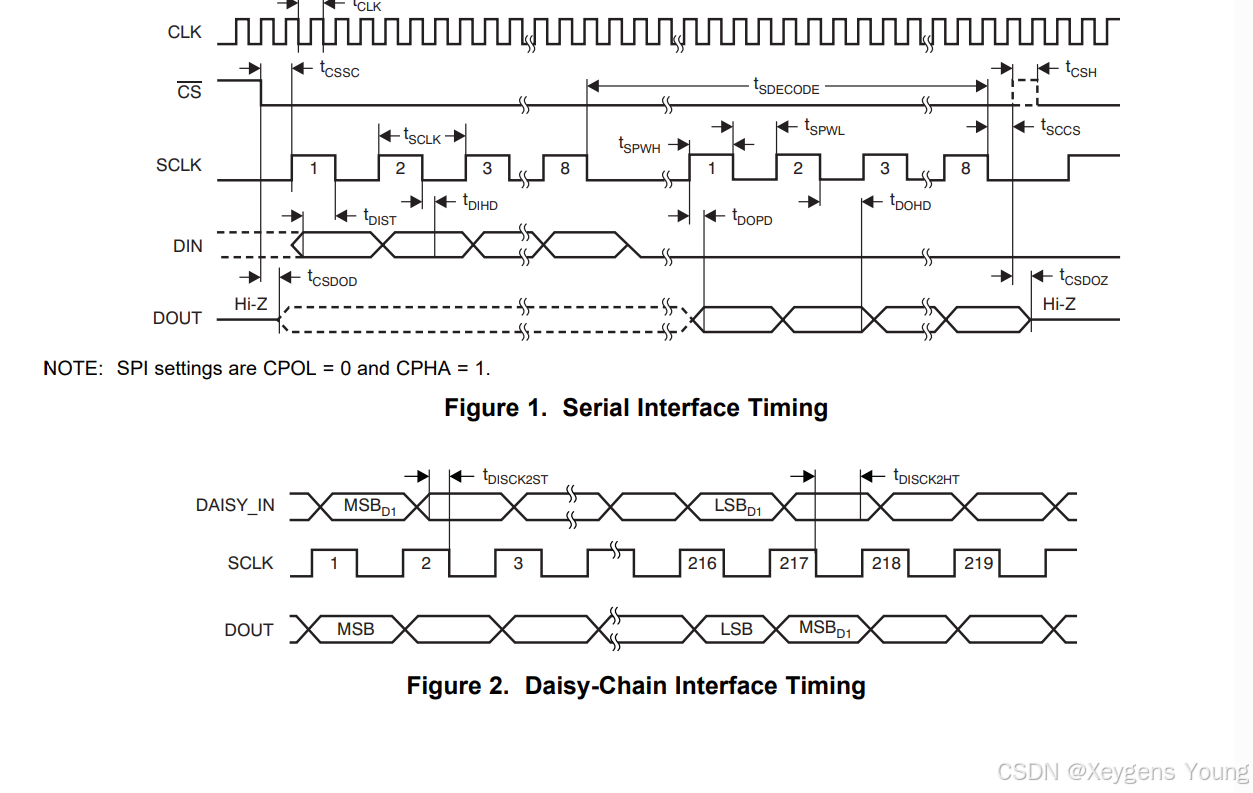

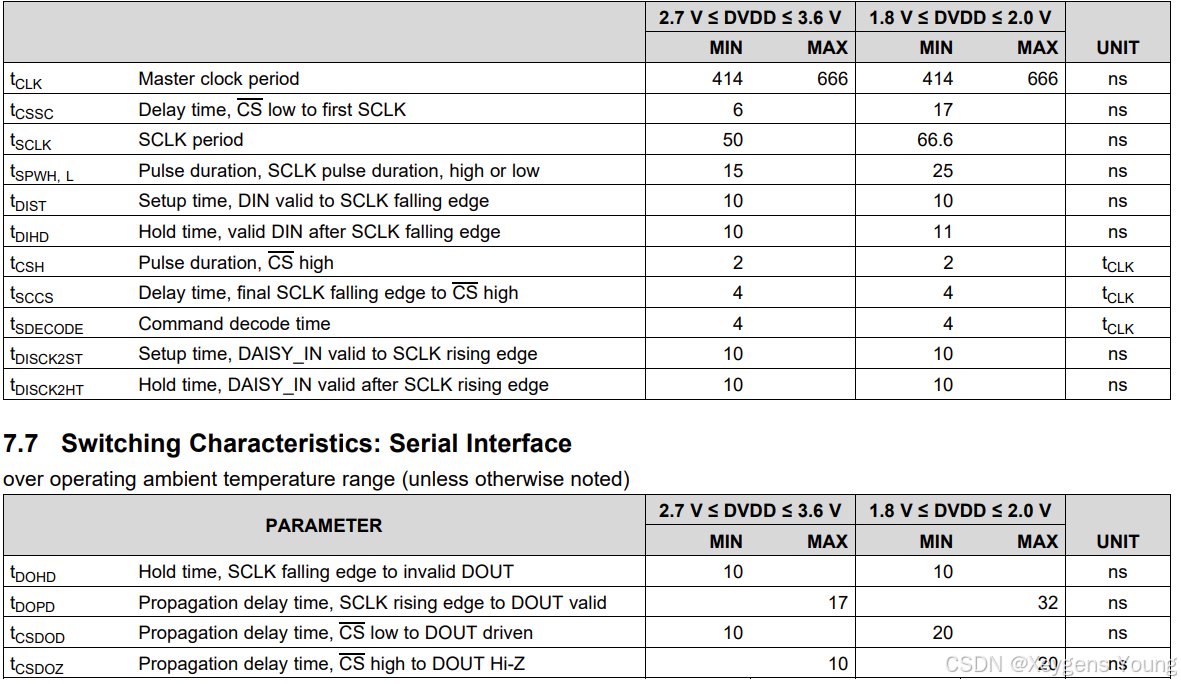

2.时序

1. 上电复位时序

1. 上电复位时序

tPOR:上电后到复位信号的时间,通常为218个时钟周期(tCLK)。

tRST:复位信号的低电平持续时间,通常为2个时钟周期(tCLK)。

tBG:内部参考电压稳定时间,通常在VCAP1电压达到1.1V后开始计算。

tSTART:复位后到可以开始使用的延时,通常为18个时钟周期(tCLK)。

2. 启动转换时序

START信号:通过将START引脚拉高或发送START命令来启动转换。

tSETTLE:转换开始到数据准备好的稳定时间,具体取决于数据速率和滤波器设置。

DRDY信号:数据准备好后,DRDY引脚会拉低,表示数据已准备好可以读取。

3. 数据读取时序

RDATAC模式:连续读取模式,设备会不断输出数据,直到发送SDATAC命令停止。

RDATA命令:按需读取数据,每次发送RDATA命令后,设备会输出最新的一组数据。

SCLK时序:串行时钟信号用于同步数据输出,数据在SCLK的上升沿输出,下降沿采样。

4. SPI通信时序

CS信号:芯片选择信号,低电平有效,用于选择当前通信的设备。

DIN信号:串行数据输入,用于发送命令和配置数据。

DOUT信号:串行数据输出,用于读取转换结果和状态信息。

命令解码时间:命令在SPI接口上的解码时间,通常需要4个时钟周期(tCLK)。

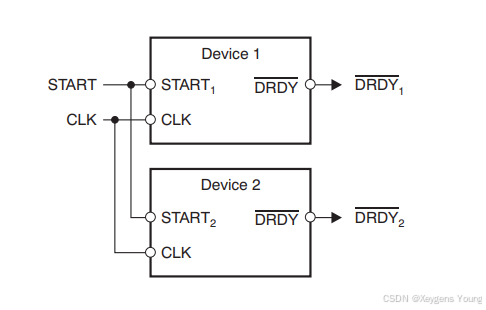

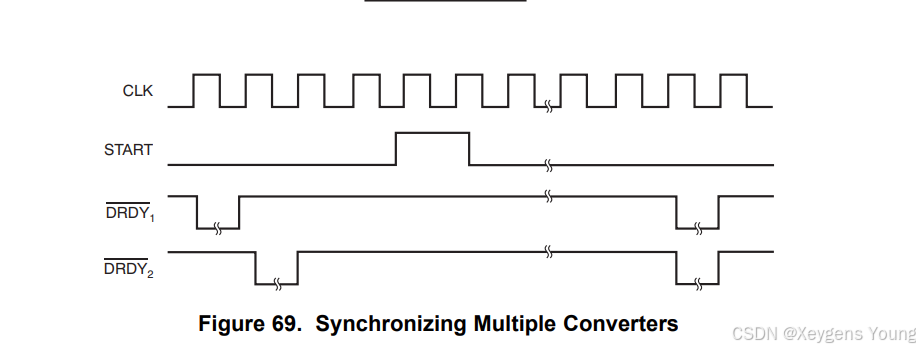

5. 多设备同步时序

START信号同步:多个设备可以通过共享START信号来同步转换。

DRDY信号同步:每个设备的DRDY信号会指示其数据准备好状态,便于主机同步读取数据。

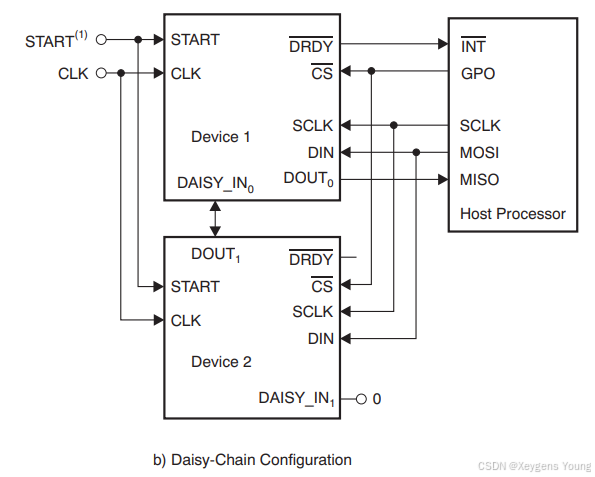

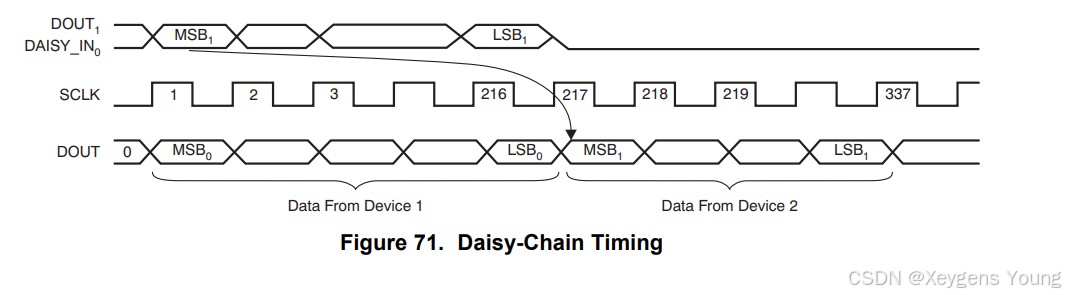

菊花链模式:在菊花链模式下,设备通过DAISY_IN和DOUT引脚连接,形成一个链式结构,便于级联多个设备。

6. 时钟信号时序

内部时钟:当CLKSEL引脚设置为1且CLK_EN位设置为1时,内部时钟信号会输出到CLK引脚。

外部时钟:当CLKSEL引脚设置为0时,设备使用外部时钟信号。

时钟精度:内部时钟在室温下的精度为±0.5%,但在整个温度范围内可能有±2.5%的误差。

7. 电源管理时序

PWDN引脚:将PWDN引脚拉低可以进入低功耗模式,拉高则退出低功耗模式。

STANDBY模式:通过发送STANDBY命令进入低功耗待机模式,此时大部分电路关闭,仅保留参考电压部分。

8. 复位时序

RESET引脚:将RESET引脚拉低可以复位设备,复位后所有寄存器恢复默认值。

复位命令:通过SPI接口发送RESET命令也可以复位设备,效果与RESET引脚相同。

9. 寄存器配置时序

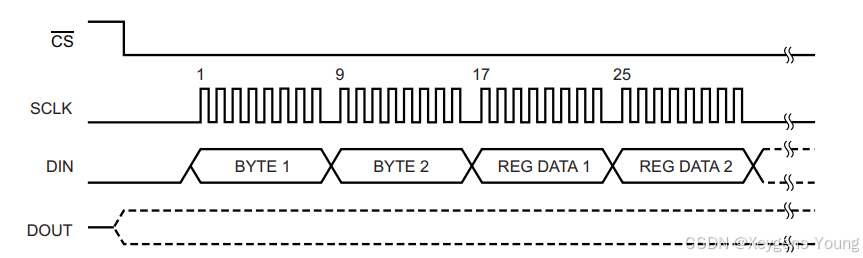

WREG命令:用于写入寄存器配置数据,需要指定起始地址和写入的数据。

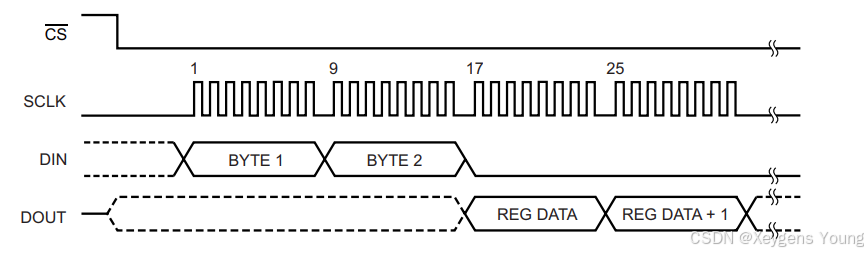

RREG命令:用于读取寄存器配置数据,需要指定起始地址和读取的数据长度。

命令执行时间:寄存器读写命令的执行时间取决于命令的长度和SCLK的速率。

10. 数据输出时序

数据格式:每个通道的数据为24位,按二进制补码格式输出,MSB在前。

数据输出速率:取决于配置的DR[2:0]位,不同设置对应不同的数据输出速率。

3.模拟功能

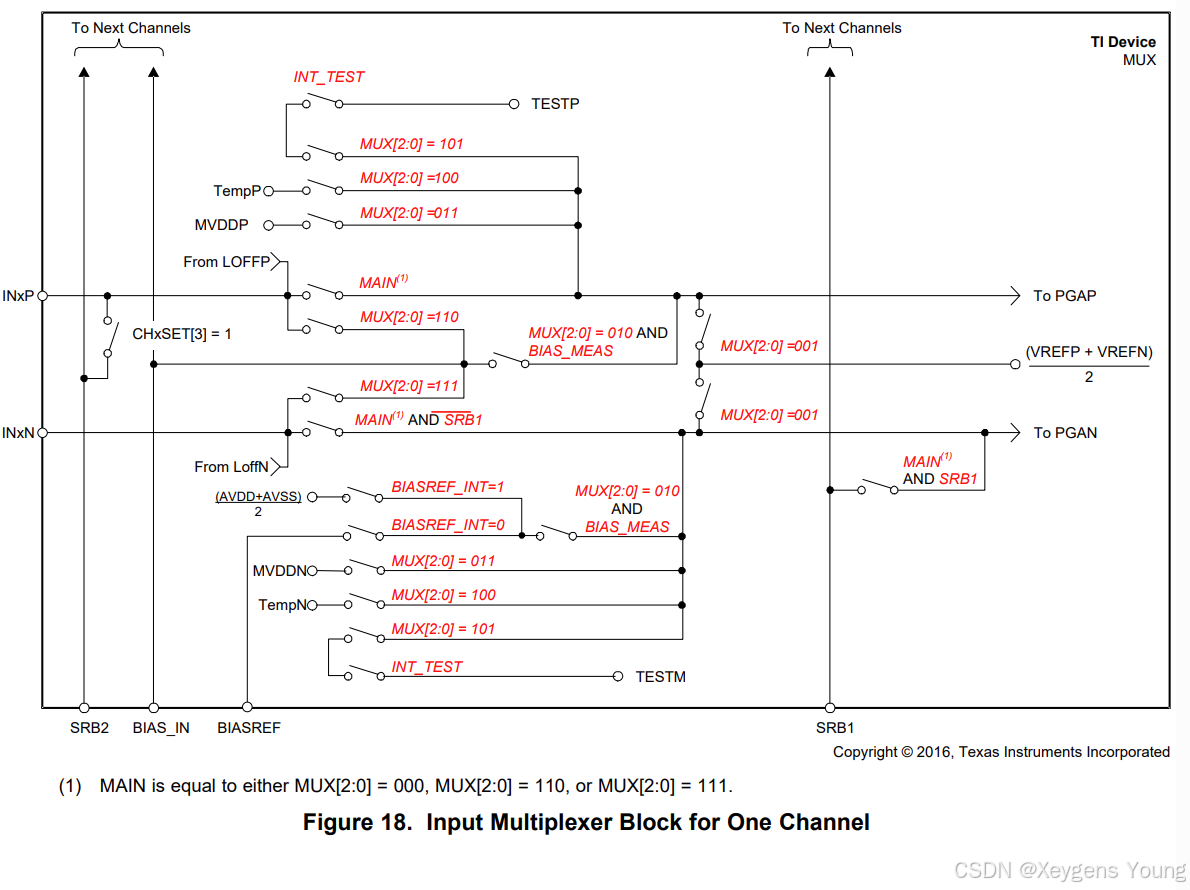

1. MUX(多路复用器)

多路复用器可以通过设置CHxSET3寄存器独立选择不同的信号源,包括正常电极输入、内部测试信号、温度传感器信号、电源测量信号等。

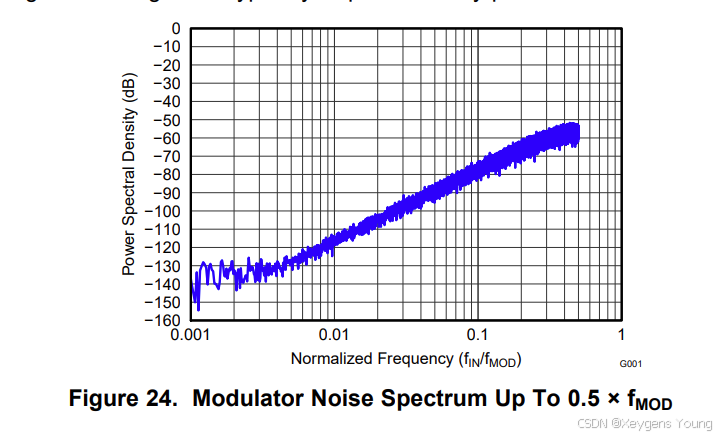

2. Δ-Σ 调制器

每个 ADS1299通道都配备了一个 24 位的ΔΣ模数转换器。该转换器使用一个针对低噪声应用优化的二阶调制器。调制器以**(fMOD = fCLK / 2)**的速率采样输入信号。与任何ΔΣ调制器一样,设备噪声在 f/2 处被整形,如图 所示。下一节中解释的片上数字抽取滤波器可用于滤除更高频率的噪声。这些片上抽取滤波器还提供抗混叠滤波。

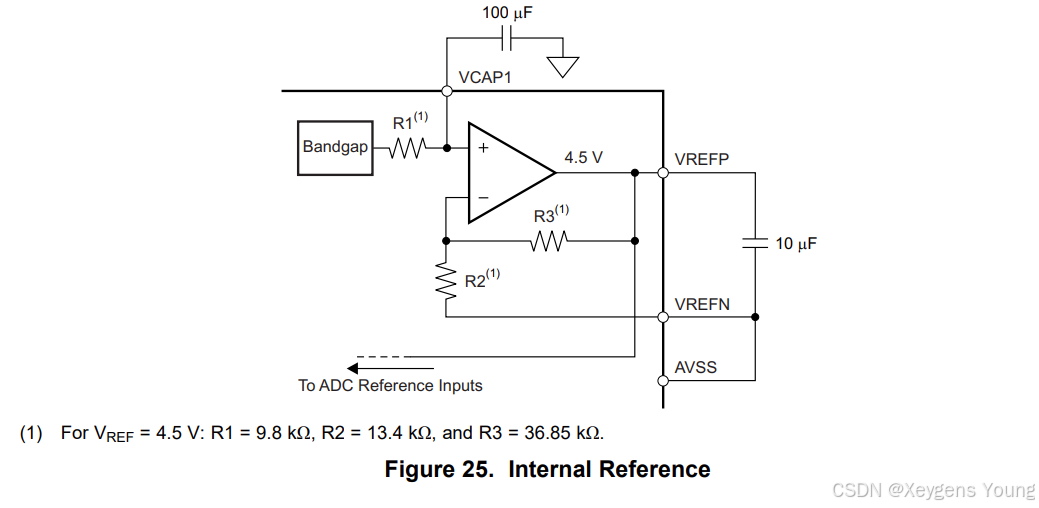

3. 参考

Reference分为内部参考和外部参考

当使用内部参考电压时,内部电路会产生一个4.5V的电压(相对于AVSS)。这个电压通过电阻网络和运算放大器进行缓冲和放大,以提供稳定的参考电压。

当使用内部参考电压时,内部电路会产生一个4.5V的电压(相对于AVSS)。这个电压通过电阻网络和运算放大器进行缓冲和放大,以提供稳定的参考电压。

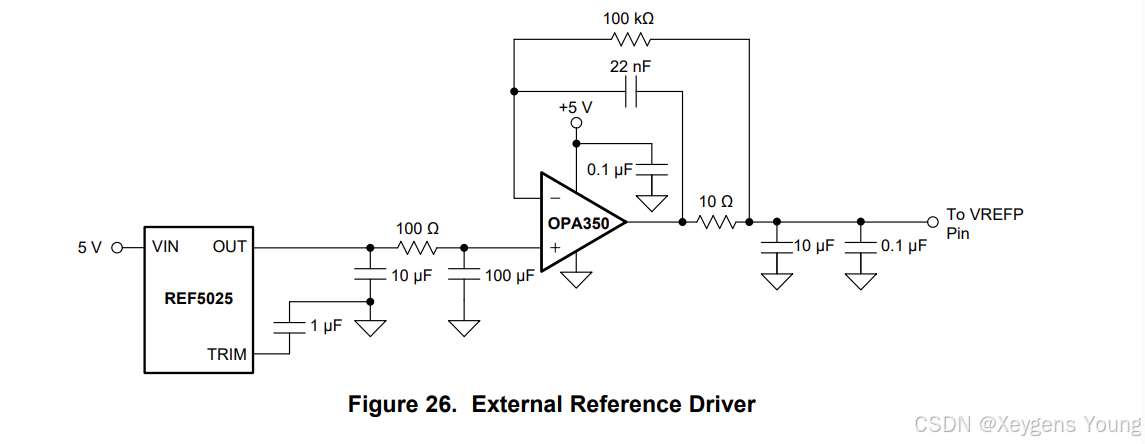

当使用外部参考电压时,参考电压源提供一个稳定的5V参考电压。OPA350运算放大器用于缓冲和驱动参考电压信号,确保信号的稳定性和低噪声。电阻和电容网络进行滤波,减少噪声和纹波,确保参考电压的稳定性,连接到VREFP引脚。

4. 模拟输入

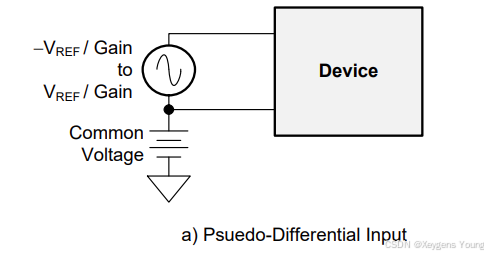

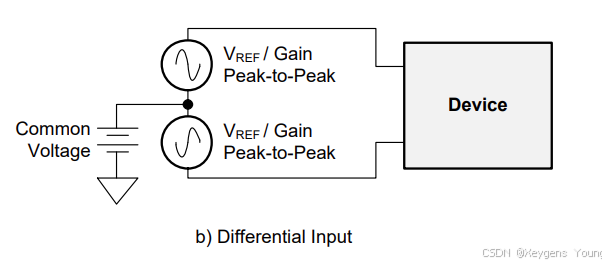

驱动 ADS1299-x 模拟输入有两种一般方法:伪差分或全差分

将公共电压设置为模拟电源的中点[(AVDD + AVSS) / 2]=0V

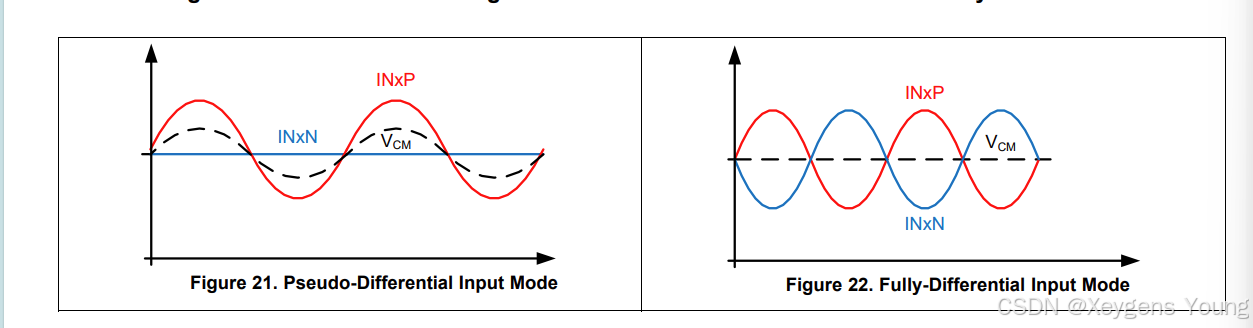

伪差分

将 INxN 引脚保持在公共电压0v,以配置全差分输入为伪差分信号。将 INxP 引脚围绕-5V/增益到+5V/增益摆动,并保持在绝对最大规格内。当输入信号配置为伪差分模式时,共模电压(VCM)会随着信号电平的变化而变化。因此,需要确保在信号的最小和最大点,差分信号仍然满足输入共模范围(Input Common-Mode Range)的要求。这是为了保证ADC在整个信号范围内都能正确地对输入信号进行采样和转换。

全差分

配置 INxP 和 INxN 信号,使其围绕公共电压中心 180°反相,以使用全差分输入方法。INxP 和 INxN 输入从公共电压+½ VREF/增益摆动到公共电压-½ VREF/增益。,并围绕固定的共模电压(V)中心。使用ADS1299-x 进行差分配置,以最大化数据转换器的动态范围。

使用:设置MUX寄存器的相应位,将INxP和INxN管脚连接到实际的信号源。

例:uint8_t mux_config = 0x03// 通道0和通道1为全差分输入

5. PGA 设置和输入范围

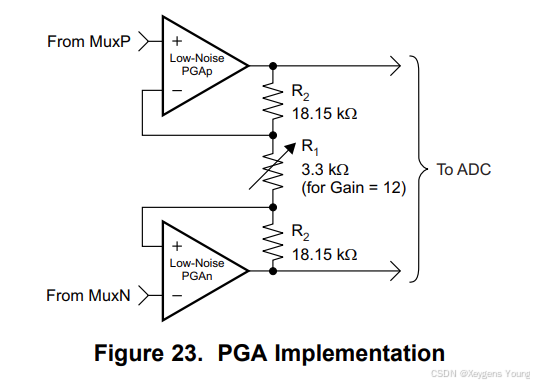

低噪声 PGA 是一种差分输入输出放大器,如图 23 所示。PGA 具有七个增益设置(1、2、4、6、8、12 和 24),可以通过写入 CHnSET 寄存器来设置

6. 输入共模范围

放大器在图 23 中的输出不能比电源(AVSS 和 AVDD)更接近,不超过 200 mV。如果放大器的输出驱动到接近电源轨的 200mV 以内,则放大器将饱和,从而变得非线性。为了防止这种非线性工作状态,输出电压不得超出前端共模范围。

Full-Scale Range =2VREF/Gain.

7. 噪声测量,测试信号,温度传感器,供电测量等略。

4.数字功能

1. 数字滤波器与Sinc 滤波器

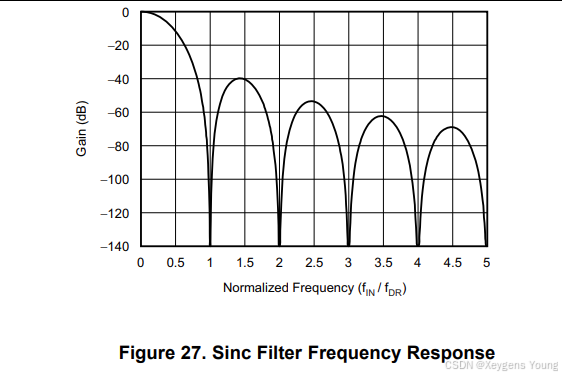

数字滤波器:通过调整滤波量在分辨率和数据速率之间进行权衡,滤波越多分辨率越高,滤波越少数据速率越高。ADS1299-x 每个通道的数字滤波器包含一个三阶 sinc 滤波器,其抽取比率可通过 CONFIG1 寄存器中的 DR (DATA RATE)位进行调整。

Sinc 滤波器:是一种可变抽取率的三阶低通滤波器,数据以 fMOD 的速率从调制器传输到滤波器,滤波器衰减高频噪声并抽取数据流形成并行数据,抽取率影响整体转换器数据速率。sinc 滤波器在输出数据速率及其倍频处有凹槽,可实现无限衰减,其频率响应和滚降特性与数据速率(DR)相关。

2. 时钟

ADS1299-x 提供两种设备时钟方法,即内部时钟和外部时钟。时钟选择由 CLKSEL 引脚和 CLK_EN 寄存器位控制。CLKSEL 引脚选择内部或外部时钟。CONFIG1 寄存器中的 CLK_EN 位启用和禁用在 CLK 引脚输出的振荡器时钟,

在菊花链配置中使用多个设备时,CLK_EN 位很有用。->CLK_EN 位是 ADS1299-x 的一个配置位,位于 CONFIG1 寄存器中。它的主要作用是控制内部时钟信号是否输出到 CLK 引脚。通过将主设备的 CLK_EN 位设置为 1,可以使其内部时钟信号输出到 CLK 引脚,从而为主设备和其他从设备提供时钟信号。从设备则需要将 CLKSEL 引脚设置为 0,以使用外部时钟信号(即主设备提供的时钟信号)

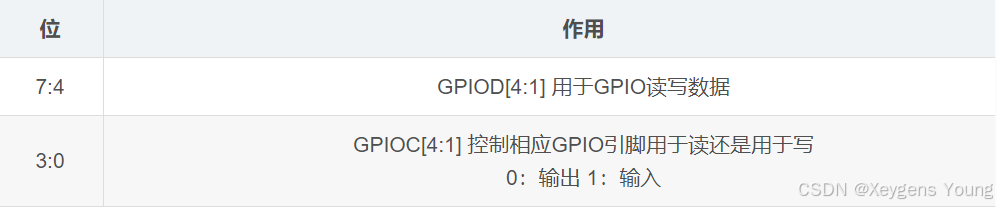

3. GPIO

ADS1299-x 正常工作模式下有四个通用数字 I/O 引脚,在电源管理、信号路由等方面为用户提供灵活的控制选项,可通过 GPIOC 位进行输入输出配置,GPIOD 位控制引脚电平。

4. 脱落检测

-

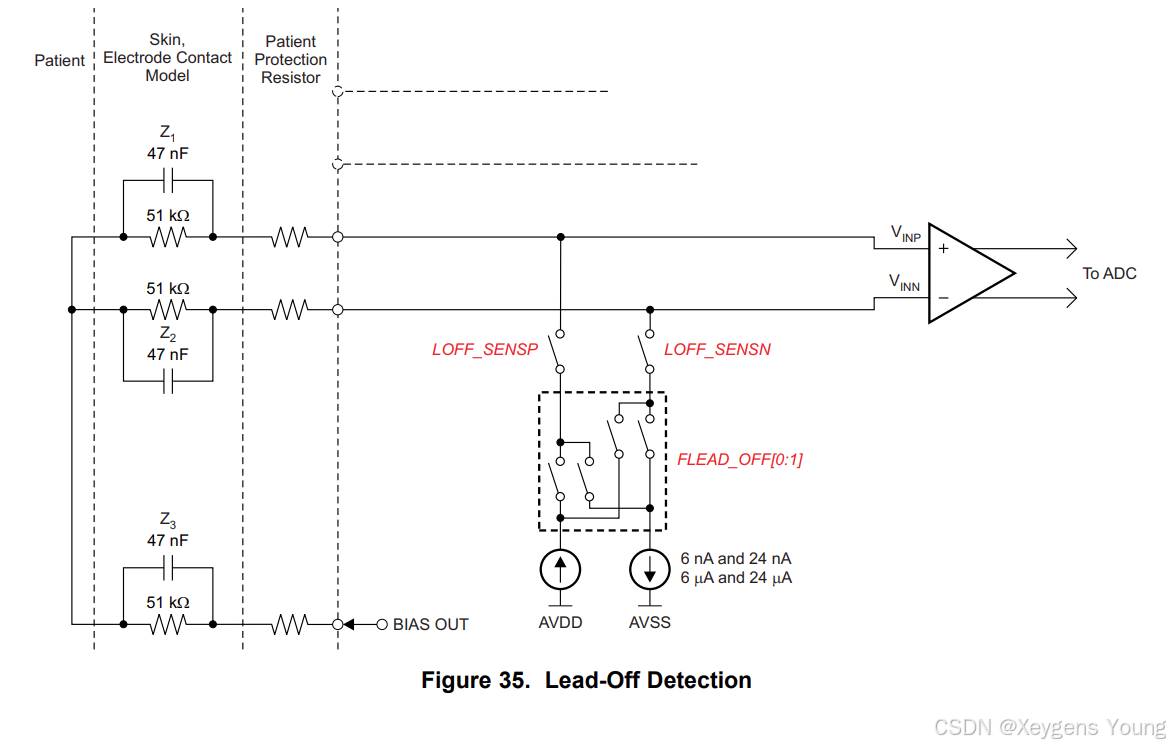

概念: 患者电极阻抗会随时间衰减。这些电极连接必须持续监控,以验证存在合适的连接。ADS1299电极脱落检测功能模块为用户提供了从各种引出线检测策略中选择的重要灵活性。

-

基本原理:注入激励电流并测量电压以确定电极是否断开。如图 35 所示的断开检测功能框图所示,该电路提供了两种确定患者电极状态的方法。这两种方法在激励信号的频率内容上有所不同。可以通过 LOFF_SENSP 和 LOFF_SENSN 寄存器在每通道的基础上选择性地执行断开。此外,可以禁用内部激励电路,仅启用传感电路。

-

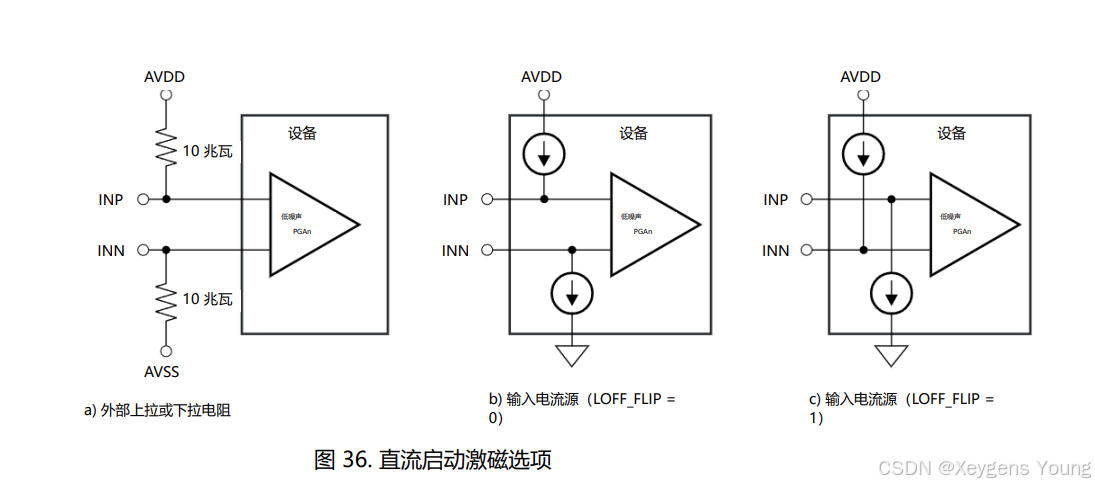

DC启动:在此方法中,起始激励采用直流信号。直流激励信号可以选择外部上拉或下拉电阻、内部电流源或汇流,如图 36 所示。通道的一侧被拉向供电,另一侧被拉向地。通过设置 LOFF_FLIP 寄存器中的位,可以交换上拉和下拉电流(如图 36b 和图 36c 所示)。如果是电流源或汇流,可以通过 LOFF 寄存器中的 ILEAD_OFF[1:0]位设置电流的大小。与 10-MΩ的上拉或下拉电阻相比,电流源或汇流提供更大的输入阻抗。

-

AC启动:在此方法中,使用带内交流信号进行激励。交流信号通过在输入端交替提供电流源和汇,以固定频率生成。频率可以通过 LOFF寄存器中的 FLEAD_OFF[1:0]位选择。激励频率选择为两个带内频率选择之一(7.8 Hz 或 31.2 Hz)。此带内激励信号通过通道并测量在输出端。

交流信号检测是通过将信号通过待数字化通道并然后在输出端进行测量来完成的。交流激励信号在感兴趣频带内引入。信号可以单独过滤并处理。通过测量激励信号频率下的输出幅度,可以计算出电极阻抗。

对于连续引出,必须外部施加一个带外交流电流源或汇到输入端。然后,该信号可以数字处理以确定电极阻抗。

5.BIAS偏置电路

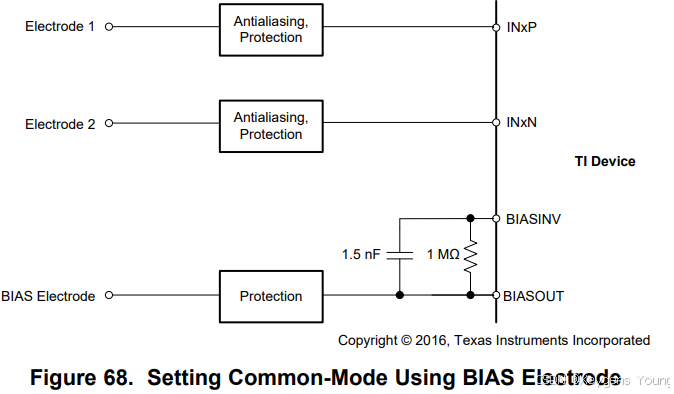

1. BIAS 引脚功能

-

BIASOUT

- 输出偏置驱动信号,用于将公共参考电压(如人体基准)反馈至电极系统,抑制共模干扰。 BIASIN

- 输入外部偏置信号,用于多设备级联时同步偏置电压。 BIASINV

- 偏置放大器的反相输入端,需外接反馈网络(如电阻和电容)以稳定偏置环路。 BIASREF

- 设置偏置参考电压。可通过寄存器选择内部生成((AVDD + AVSS)/2)或外部输入。

2. 相关寄存器配置

CONFIG3 寄存器(地址 03h)

BIAS_MEAS(位 4)

1: 允许通过特定通道(MUX 设置为 010)测量 BIASIN 信号(相对于 BIASREF)。

BIASREF_INT(位 3)

1: 使用内部生成的参考电压((AVDD + AVSS)/2);

0: 使用外部输入的 BIASREF 电压。

PD_BIAS(位 2)

1: 启用偏置放大器;0: 关闭偏置放大器以省电。

BIAS_LOFF_SENS(位 1)

1: 启用偏置电极的导联断开检测功能。

BIAS_SENSP 和 BIAS_SENSN 寄存器(地址 0Dh、0Eh)

控制哪些通道的输入信号参与偏置电压的生成(例如,选择通道 1-3 的输入信号生成平均偏置电压)。

3. BIAS 功能模式

-

偏置驱动(Bias Drive)

功能描述:用于抵消EEG系统中的共模干扰,通过内部多路复用器选择电极组合并生成反馈信号,将患者身体偏置到特定电压,以减少共模干扰。

实现方式:通过设置BIAS_SENSP和BIAS_SENSN寄存器,选择作为偏置驱动输入的电极组合;通过CONFIG3寄存器的BIASREF_INT位,选择内部或外部参考电压;通过PD_BIAS位控制BIAS放大器的开启和关闭。

相关寄存器:BIAS_SENSP、BIAS_SENSN、CONFIG3。 -

电极脱落检测(Lead-Off Detection)

功能描述:通过在电极上施加偏置电压,检测电极与皮肤之间的阻抗变化,判断电极是否脱落。

实现方式:通过设置LOFF_SENSP和LOFF_SENSN寄存器,选择进行电极脱落检测的电极;通过LOFF_FLIP寄存器,设置电流源的极性;通过LOFF寄存器,设置脱落检测的电流大小和频率。

相关寄存器:LOFF_SENSP、LOFF_SENSN、LOFF_FLIP、LOFF。 -

偏置电极脱落检测(Bias Electrode Lead-Off Detection)

功能描述:在上电时,使用电流源和比较器判断BIAS电极连接状态,检测BIAS电极是否脱落。

实现方式:通过CONFIG3寄存器的BIAS_LOFF_SENS位,启用BIAS电极脱落检测功能;通过BIAS_STAT位读取BIAS电极的连接状态。

相关寄存器:CONFIG3、BIAS_STAT。 -

偏置信号测量(Bias Signal Measurement)

功能描述:可以将BIASOUT信号路由到某个通道进行测量,以便监测偏置信号的状态和质量。

实现方式:通过设置通道的MUX[2:0]位为特定值,将BIASIN信号路由到该通道进行测量。

相关寄存器:CHnSET。 -

偏置状态监测(Bias Status Monitoring)

功能描述:通过BIAS_STAT位,监测BIAS电极的连接状态,判断BIAS电极是否脱落。

实现方式:在CONFIG3寄存器中设置BIAS_LOFF_SENS位,启用BIAS电极脱落检测功能;通过BIAS_STAT位读取BIAS电极的连接状态。

相关寄存器:CONFIG3、BIAS_STAT。 -

偏置参考电压设置(Bias Reference Voltage Setting)

功能描述:可以选择内部生成的参考电压或外部提供的参考电压作为BIAS功能的参考电压。

实现方式:通过CONFIG3寄存器的BIASREF_INT位,设置BIAS参考电压的来源。

相关寄存器:CONFIG3。 -

偏置放大器电源控制(Bias Amplifier Power Control)

功能描述:可以控制BIAS放大器的电源状态,以节省功耗。

实现方式:通过CONFIG3寄存器的PD_BIAS位,开启或关闭BIAS放大器。

相关寄存器:CONFIG3。 -

偏置测量(Bias Measurement)

功能描述:可以启用BIAS测量功能,将BIAS_IN信号路由到指定通道进行测量。

实现方式:通过CONFIG3寄存器的BIAS_MEAS位,启用BIAS测量功能;通过设置通道的MUX[2:0]位,将BIAS_IN信号路由到该通道。

相关寄存器:CONFIG3、CHnSET。 -

偏置信号路由(Bias Signal Routing)

功能描述:可以将BIASOUT信号路由到任意输入电极,实现动态改变用作参考信号驱动患者身体的电极。

实现方式:通过设置通道的MUX[2:0]位,将BIASOUT信号路由到指定电极。

相关寄存器:CHnSET。 -

偏置功能在多设备配置中的应用(Bias Function in Multiple Device Configuration)

功能描述:在多设备菊花链配置中,BIAS驱动放大器可以级联,通过设置DAISY_EN位,启用菊花链模式,实现多个设备的BIAS功能协同工作。

实现方式:通过CONFIG1寄存器的DAISY_EN位,启用菊花链模式;通过BIAS_SENSP和BIAS_SENSN寄存器,设置各设备的BIAS信号输入。

相关寄存器:CONFIG1、BIAS_SENSP、BIAS_SENSN。

4. SRB

- 概念

SRB是ADS1299模数转换器中的一个引脚,主要用于连接参考电极,实现对患者身体的偏置驱动和参考信号的引入。 - 功能.

参考信号引入:SRB引脚可以连接到参考电极,将参考信号引入到ADC中,为各通道的测量提供一个共同的参考点。

偏置驱动:与BIAS功能协同工作,通过SRB引脚将偏置信号施加到患者身体,使各测量电极的共模电压保持在ADC的可测量范围内,实现直流耦合测量。

信号路由:SRB信号可以被路由到各个通道的反相输入端,实现对测量信号的参考和偏置。

6.两种转换模式

-

Continuous(连续转换模式)

1.概念:DS1299的默认工作模式,设备在启动后会持续进行数据转换和输出,直到被停止。

在此模式下,数据转换以固定的速率进行,数据准备就绪后可通过SPI接口连续读取。

2.工作原理

当发送START命令或START引脚被拉高时,设备开始转换,DRDY引脚变为高电平。转换完成后,DRDY引脚变为低电平,表示数据已准备好。设备会持续进行转换,DRDY引脚会按照设定的数据速率周期性地变为低电平,指示新数据准备好。数据可通过RDATAC命令以连续模式读取,或通过RDATA命令按需读取。

3.配置步骤

发送START命令或拉高START引脚。

等待设定的转换时间。

通过RDATAC或RDATA命令读取数据。

如需停止转换,发送STOP命令或拉低START引脚。 -

Single-Shot(单次转换模式)

1.概念:单次转换模式允许设备进行一次单独的转换,转换完成后自动停止。此模式适用于需要非连续或特殊数据速率的应用。

2.工作原理

配置设备进入单次转换模式后,发送START命令或拉高START引脚,设备进行一次转换。

转换完成后,DRDY引脚变为低电平,表示数据已准备好。

设备不会自动进行下一次转换,需重新发送START命令或拉高START引脚才能进行新的转换。

3.配置步骤

在CONFIG4寄存器中设置SINGLE_SHOT位为1,进入单次转换模式。

发送START命令或拉高START引脚,启动单次转换。

等待转换完成,DRDY引脚变为低电平。

通过RDATA命令读取数据。

如需再次转换,重复步骤。

7.寄存器

-

寄存器表

-

CONFIG1

-

CONFIG2

-

CONFIG3

-

LOFF lead-off控制寄存器

-

CHnSET 通道配置

-

BIAS_SENSP

-

BIAS_SENSN

-

LOFF_SENSP/LOFF_SENSN

-

LOFF_STATP

-

LOFF_STATN

-

MISC1 杂项寄存器1

-

MISC2 杂项寄存器2

-

CONFIG4 配置寄存器4

详情略。

8.命令

-

系统控制命令

WAKEUP :退出待机模式。

STANDBY :进入待机模式,此时大部分电路关闭,仅保留参考电压部分。

RESET:复位设备,使所有寄存器恢复默认值。

START :启动AD数据转换,若转换已进行,此命令无效。

STOP :停止AD数据转换,允许当前转换完成。 -

数据读取命令

RDATAC (启用连续数据读取模式):设备默认模式,可在数据准备就绪时连续读取数据。

SDATAC (停止连续数据读取模式):停止RDATAC。

RDATA (单次读取指令):读取单次数据转换结果。 -

寄存器操作命令

RREG (读取寄存器):读取指定寄存器的值,需指定起始地址和读取长度。(双字节)

WREG (写入寄存器):写入配置数据到寄存器,需指定起始地址和写入数据。(双字节)

- 数据格式

24bit head + 24bit * n channel

24bit head包括1100 + LOFF_STATP + LOFF_STATN + bits[4:7] of the GPIO register

二、ADS1299的使用

1.单独使用

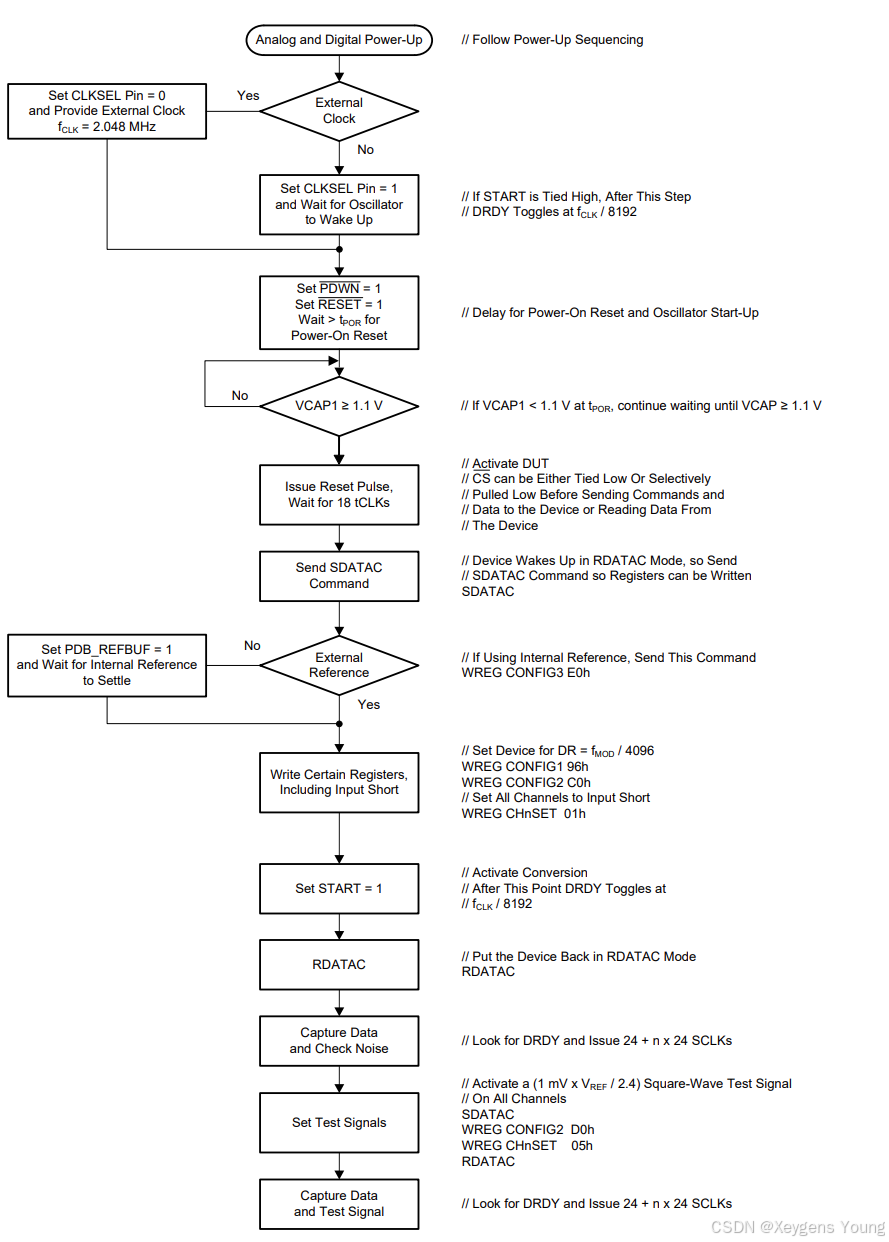

1. 基本步骤

- 模拟与数字上电

- 判断是否使用外部时钟:

如果使用外部时钟(f=2.048 MHz),设置CLKSEL引脚为0并提供外部时钟。

如果不使用外部时钟,设置CLKSEL引脚为1并等待振荡器唤醒。 - 设置PDBN=1和RESET=1,等待上电复位时间(tPOR)。

- 判断VCAP1是否大于等于1.1V:

如果否,继续等待。

如果是,进行下一步。 - 等待18个时钟周期(tCLK)。

- 发送SDATAC命令。

- 判断是否使用外部参考:

如果使用外部参考,进行相关设置。

如果不使用外部参考,发送WREG CONFIG3 E0h命令以设置内部参考。 - 设置PDB_REFBUF=1,并等待内部参考稳定。

- 写入特定寄存器,包括输入短路设置。

- 设置START=1,开始转换。

- 发送RDATA C命令。

- 捕获数据并检查噪声。

- 设置测试信号。

- 捕获数据并测试信号。

2.典型配置

- 采集电极+参考电极+驱动电极

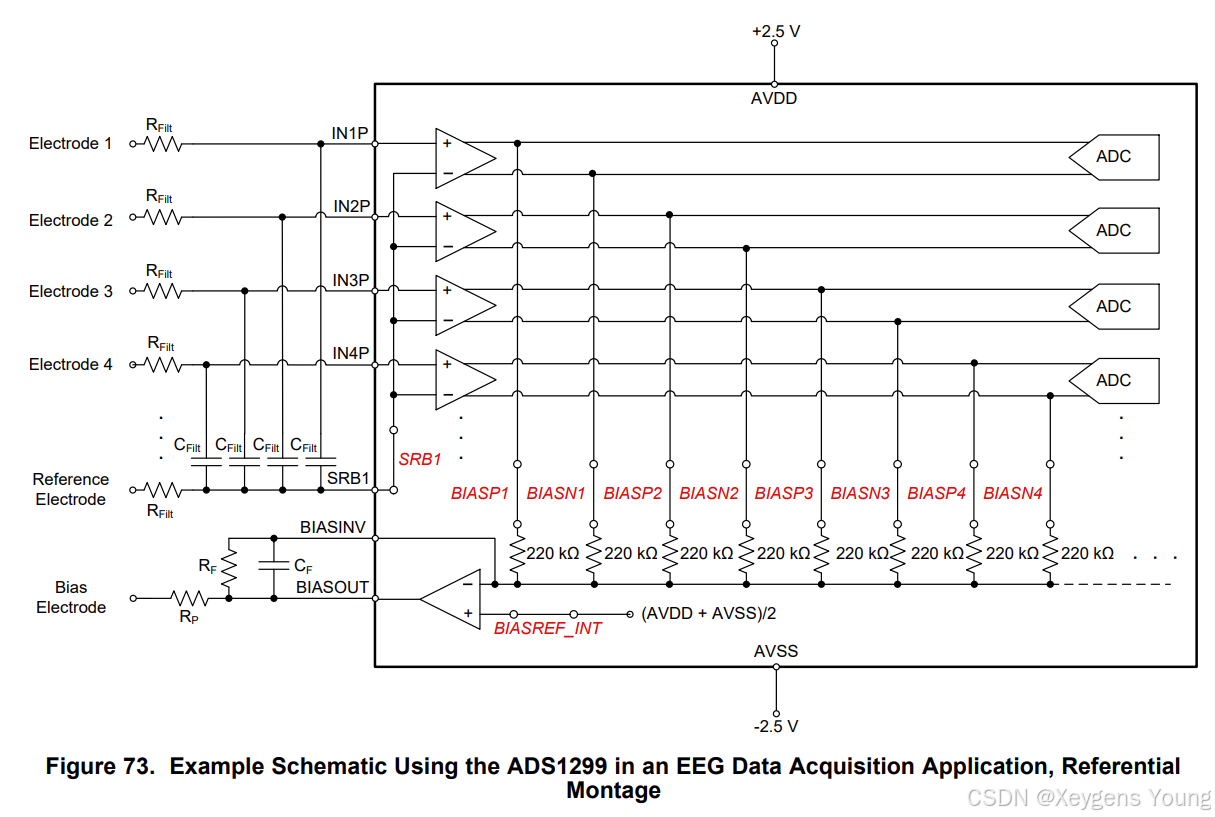

eg:下图ElectrodeX为采集电极,Reference Electrode 为参考电极,Bias Electrode 为驱动电极。

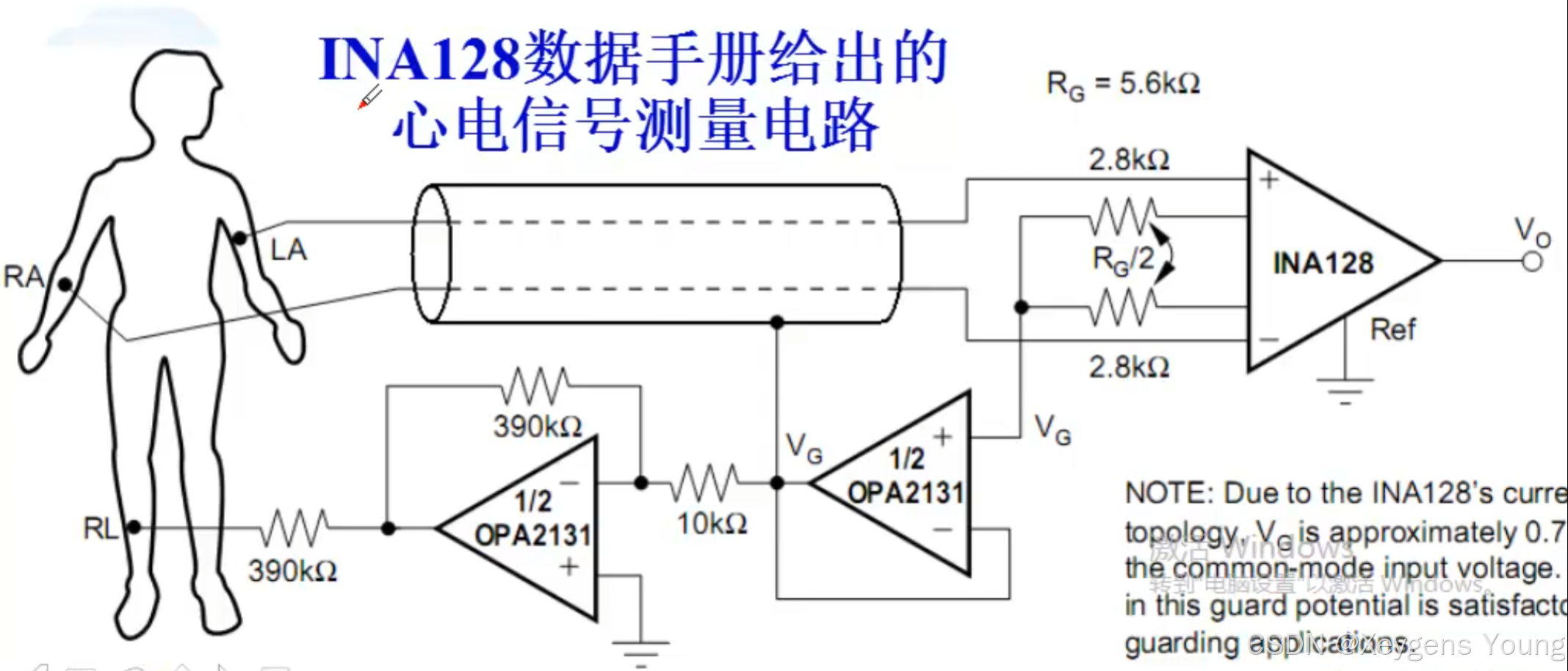

2.1.右腿驱动电极(共模输入)

-

概念:通过一个接在右腿的电极来达到去除50Hz/60Hz共模干扰的效果。右腿驱动电路通常用于生物信号放大器,以减少共模干扰 。 心电图(生物信号放大器等心电图 ),脑电图( 脑电图 )或肌电电路所发出的电子信号十分微小,通常只有几个微伏(万分之一伏 )。而由于病人的身体也可以作为天线能受到电磁干扰特别是50/60Hz的家用供电噪音,这种干扰可能会掩盖的生物信号,使得信号难以测量。 因此,可以通过添加右腿驱动电路用来消除干扰噪声。

————————————————版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/qq_42580947/article/details/122044761

-

原因:ADS1299测量全差分信号,其中共模电压点位于正负模拟输入的中点。内部 PGA 由于操作所需的余量而限制了共模输入范围。人体容易产生共模漂移,因为噪声容易耦合到人体上,类似于天线。这些共模漂移可能会将 ADS1299输入共模电压推离ADC 的可测量范围。

-

原理:负反馈

-

使用:如果系统使用患者驱动电极,ADS1299-x 包括一个片上偏置驱动(BIAS)放大器,该放大器连接到患者驱动电极。BIAS 放大器的作用是偏置以保持其他电极共模电压在有效范围内。当开启电源时,放大器使用模拟中点电压或 BIASREF 引脚上的电压作为参考输入,驱动患者达到该电压。ADS1299-x 提供了使用输入电极电压作为反馈到放大器的选项,通过在 BIAS_SENSP 和 BIAS_SENSN 寄存器中设置相应的位,更有效地稳定输出到放大器参考电压。

3. 硬件连接

连接设备至双极(±2.5 V 和 3.3 V)电源

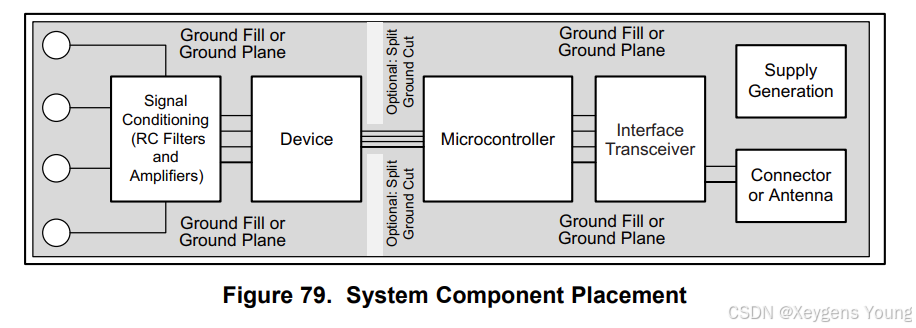

4. 布局指南

2.多设备级联用法(DAISY_EN)

通过菊花链实现八电极拓展为16电极。

1. 硬件连接

-

连接SPI信号

将两个ADS1299设备的SCLK、DIN、CS信号连接在一起。

对于DOUT信号,将第二个设备的DOUT连接到第一个设备的DAISY_IN引脚,形成菊花链结构。

-

时钟同步

如果使用内部时钟,设置主设备的CLK_EN位为1,使内部时钟信号输出到CLK引脚,从设备的CLKSEL引脚设置为0,使用外部时钟信号。

如果使用外部时钟,确保所有设备的CLK引脚连接到同一时钟源。

-

偏置同步:

主设备的 BIASOUT 连接至从设备的 BIASIN,确保多设备共享同一偏置参考电压。 -

连接其他信号

将两个设备的DRDY信号连接到微控制器的不同引脚,以便区分每个设备的数据准备状态。

如果需要同步启动转换,将START信号连接在一起。

2. 寄存器配置

-

启用菊花链模式

在主设备的CONFIG1寄存器中设置DAISY_EN位为1,启用菊花链模式。 -

配置从设备

确保从设备的CLKSEL引脚设置为0,使用外部时钟信号。

如果使用内部时钟,从设备的CLK_EN位应设置为0。 -

同步配置

通过主设备的SPI接口发送命令和数据,确保两个设备的配置寄存器设置一致,包括数据速率、增益、输入多路复用器设置等

3. 数据读取

- 连续读取模式(RDATAC)

在主设备上发送RDATAC命令,启动连续数据读取模式。

按照设备数量和通道数量计算总的数据位数,从主设备的DOUT引脚读取数据,数据顺序为主设备数据在前,从设备数据在后。

7134

7134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?