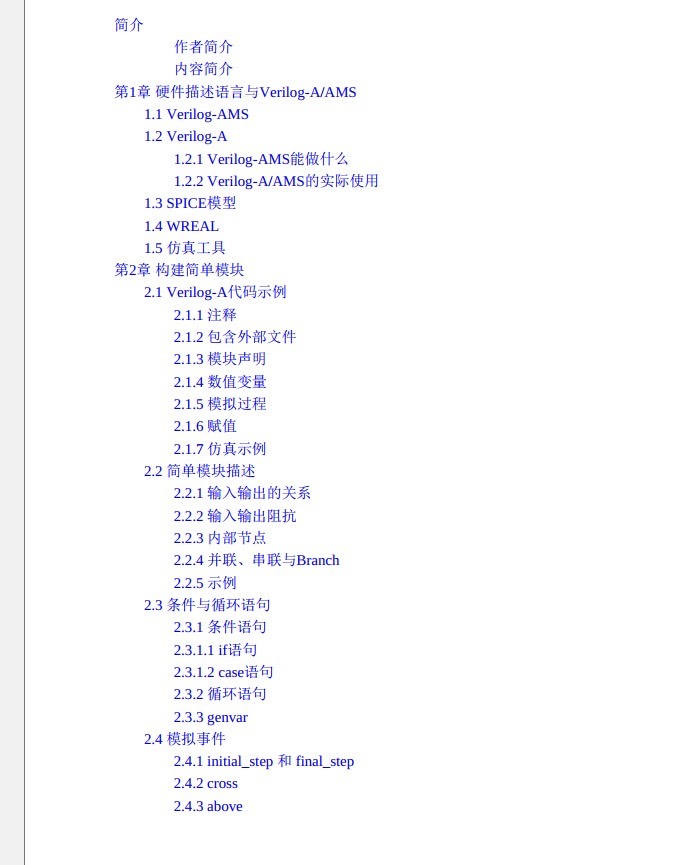

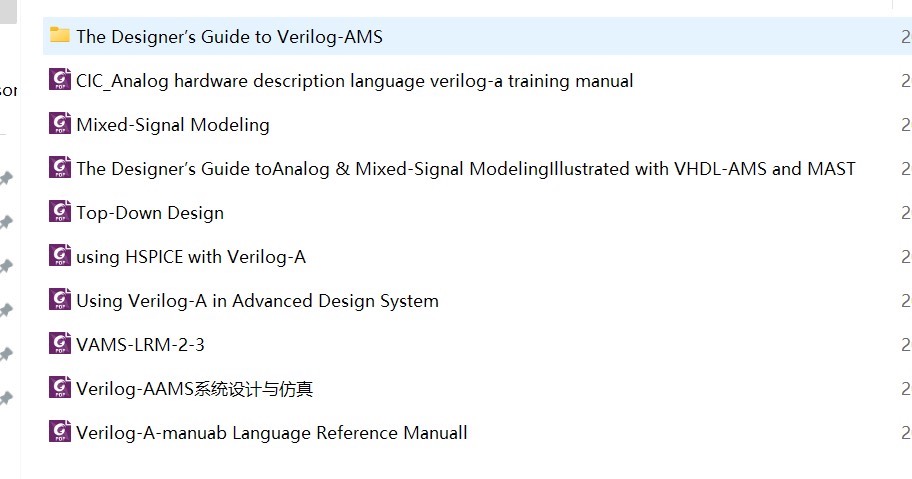

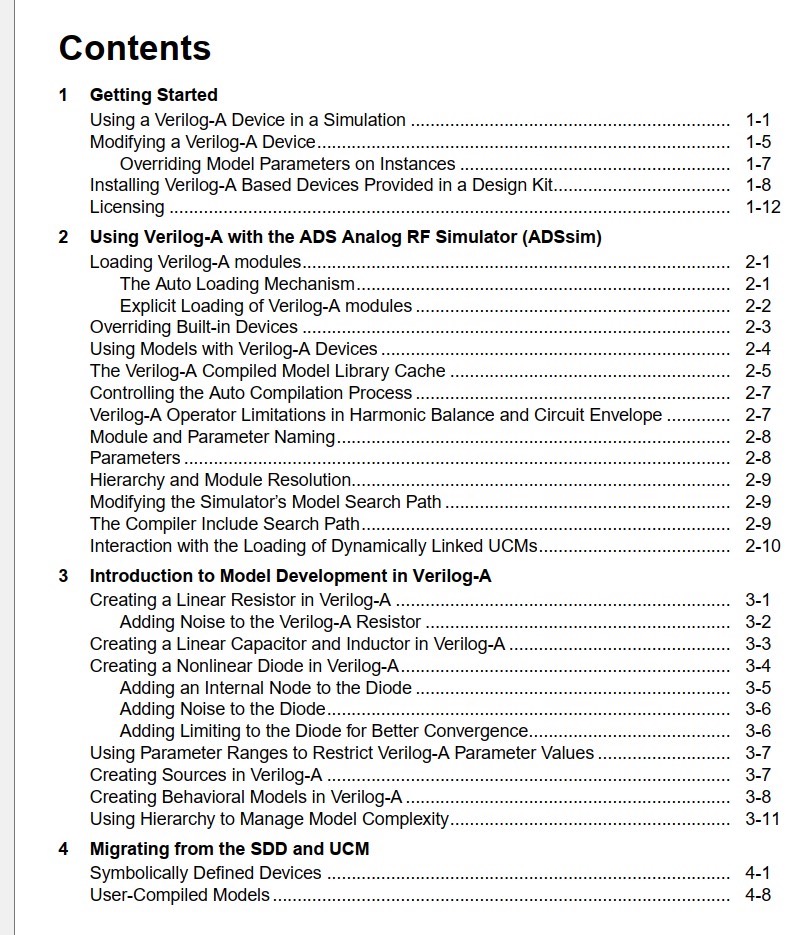

Verilog-A 学习资料 SAR ADC 模数转换器 混合信号IC设计 模拟IC设计 包含现成常用的Verilog-A器件代码,可以直接拿来用 Verilog-A 一种使用 Verilog 的语法来描述模拟电路的行为

搞电路设计的兄弟应该都懂,Verilog-A这玩意儿就像模拟工程师的瑞士军刀。特别是做混合信号芯片的时候,没有个趁手的建模工具真能把人逼疯。今天咱们来聊聊怎么用Verilog-A快速搭建SAR ADC模型,手头正好有几个现成的代码模块可以直接套用。

先说说SAR ADC的基本结构。这货就是个带数字回路的模数转换器,核心就三个部分:比较器、DAC(数模转换器)和逐次逼近寄存器。用Verilog-A建模最大的好处是能同时处理模拟和数字行为,比如下面这个比较器的模型:

`include "constants.vams"

module comparator (vin, clk, dout);

input vin, clk;

output dout;

electrical vin, clk;

reg dout;

analog begin

@(cross(V(clk) - 0.5, +1)) begin

if (V(vin) > 0.5)

dout = 1'b1;

else

dout = 1'b0;

end

end

endmodule这段代码亮点在时钟沿检测的骚操作——用cross函数捕捉时钟上升沿。注意这里的0.5其实是工艺相关的阈值电压,做先进工艺时得换成实际值。迟滞功能可以在这个if判断里加个偏移量实现,改天专门开一篇讲这个。

SAR逻辑部分用Verilog-A的数字行为建模特别方便。比如这个3位SAR控制逻辑:

module sar_logic (clk, cmp_out, digital_out);

input clk, cmp_out;

output [2:0] digital_out;

reg [2:0] digital_out;

integer bit_counter;

analog begin

@(initial_step) begin

digital_out = 3'b100; // 初始MSB置1

bit_counter = 2;

end

@(cross(V(clk)-0.5, +1)) begin

if (bit_counter >=0) begin

if (cmp_out == 1)

digital_out[bit_counter] = 1;

else

digital_out[bit_counter] = 0;

digital_out = digital_out >> 1;

bit_counter = bit_counter -1;

end

end

end

endmodule这里用位移操作实现逐次逼近,注意数字信号的赋值要用非阻塞方式。实际项目中要加复位逻辑,不然仿真时容易卡在奇怪的状态。

开关电容DAC是SAR ADC建模的难点,这里有个简化版的电荷重分配模型:

module cap_dac (d, vout);

input [2:0] d;

output vout;

electrical vout;

parameter real C_unit = 10e-15;

integer i;

real charge;

analog begin

charge = 0;

for(i=0; i<3; i=i+1) begin

if (d[i])

charge += C_unit * V(vref);

else

charge += C_unit * V(gnd);

end

V(vout) <+ charge / (7*C_unit); // 7=2^3-1

end

endmodule这个模型考虑了电容阵列的电荷守恒,用for循环处理数字输入位。注意实际应用中要考虑寄生电容和开关电荷注入,可以通过增加probe节点来建模。

最后说几个实战技巧:1)用$bound_step()控制仿真步长,避免开关切换时的数值震荡;2)带隙基准这类模块建议直接调用厂家提供的模型;3)做蒙特卡洛分析时记得在模型里加随机偏移量。Verilog-A建模就像搭乐高,关键是模块间的接口要定义清楚,剩下的就是排列组合的功夫了。

217

217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?