一种基于物联网实现树莓派与现场可编程门阵列接口的鲁棒性图像处理技术

摘要

随着物联网的发明,图像处理正达到一个全新的水平,因为物联网正成为每个人生活中重要的一部分。这些系统在图像处理领域创造了众多应用,例如图像滤波和处理。该系统的实现通过低成本的ZedBoard Zynq 7000 FPGA和树莓派完成。对输入图像经过多种图像处理滤波器(如高斯滤波器、锐化滤波器和平滑滤波器)处理后的输出已获得,并将结果显示在VGA显示器上。此外,还对尺寸为256x256的Lena图像进行了边缘检测和灰度操作。同时记录了芯片利用率。

关键词

现场可编程门阵列, 物联网, 图像处理

I. 引言

三十年前,现场可编程门阵列由赛灵思公司 [1] 开发。如今,这些现场可编程门阵列被用于各种用途,例如图像处理、自动灌溉系统等。基于现场可编程门阵列的物联网系统在许多研究领域得到了广泛应用。随着物联网设备的增加,各种设备相继被开发出来,从而减少了人力投入[2]。

在当前场景下,基于Web服务器的Verilog\VHDL代码被设计用于实现基于物联网的超大规模集成电路设计,如图1所示。

II. 相关工作

用于图像处理的硬件由数字信号处理器构成,这些硬件被基于Web服务器应用的图像滤波过程所需求。广泛使用的数字信号处理器倾向于在算法中保持最常见的因素,而无需针对特定逻辑。因此,由于这种倾向,数字信号处理器具有最大的现有字宽、典型的内存寻址技术以及常规算术运算 [3]。

图像处理的应用偶尔需要大量的数据类型,例如使用浮点运算进行像素操作 [4]。现场可编程门阵列提供了一种显著的可重配置方案,即速度快,且现场可编程门阵列比数字信号处理器更便宜。

在基于物联网的图像处理中,当DSP无法正常工作时,现场可编程门阵列可用于卷积操作[5, 6]。本文使用了两种硬件平台,即ZedBoard Zynq 7000 FPGA和树莓派。

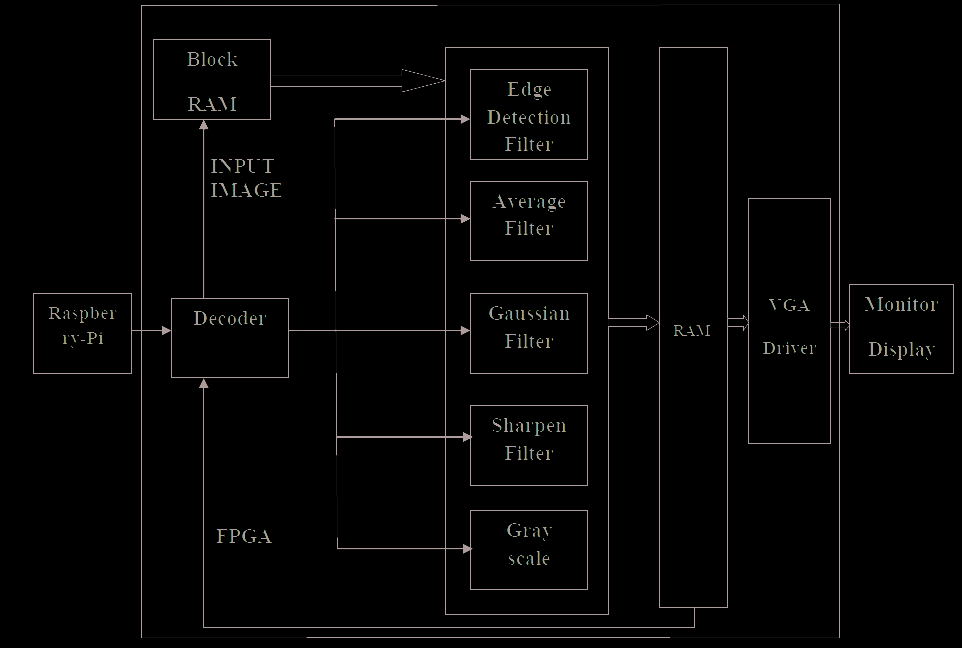

所提出的相关工作如图2所示。

本研究提出的主要目标是基于现场可编程门阵列实现的图像处理系统能够通过Web服务器应用轻松访问。

III. 系统架构

系统架构由多个逻辑模块组成,用于对像素相关的信息执行点运算。块RAM用于恢复这些数据。大小为256x256的输入图像已作为.coe文件加载到 ZedBoard Zynq 7000 FPGA中。编写了解码逻辑,用于选择从树莓派发送到ZedBoard Zynq 7000 FPGA的图像上应应用哪种类型的滤波器。处理后的图像存储在块RAM中,并输出至VGA显示器。系统架构如图3所示。

A. FPGA设计:

解码逻辑连接到ZedBoard Zynq 7000的PMOD引脚,这些引脚可用作通用输入/输出(GPIO)引脚。所提出的用于平均滤波器、高斯滤波器、边缘检测、灰度和锐化滤波器的图像处理算法是使用Verilog硬件描述语言(HDL)设计的。滤波所使用的窗口大小为3x3。

B. 显示接口:

使用VGA驱动和现场可编程门阵列实现水平和垂直同步。发送到VGA驱动的输入数据来自RAM。

C. 树莓派接口:

使用树莓派接口来实现基于物联网的图像处理滤波器将是一种独特技术。最终用户可以通过树莓派接口远程使用基于物联网的图像处理系统的功能。

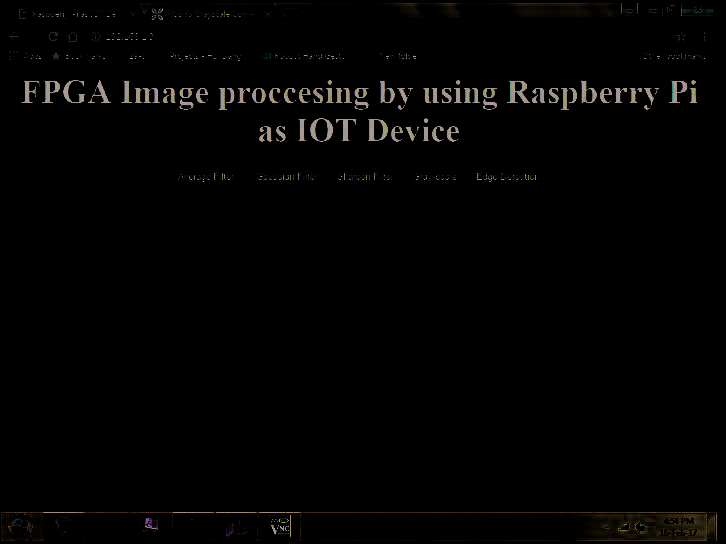

用户提供了基于Web服务器应用的图像处理系统,可以通过提供树莓派的IP地址从任何网络浏览器进行访问,并通过树莓派的GPIO引脚发送相应的二进制消息(已编码)来执行选定的任务。

D. 解码逻辑:

解码器用于选择适当的滤波器以满足用户的选择。为了激活所需的逻辑块,解码器生成一个标志 [8]。系统框图如图5所示。

IV. 实验结果

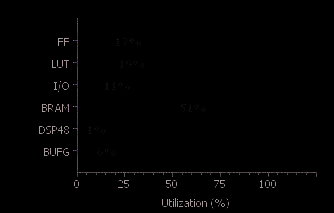

使用Xilinx Vivado软件对用Verilog硬件描述语言编写的代码进行仿真,以获得各种滤波器的输出,包括高斯滤波器、锐化滤波器和平滑滤波器。本文所采用的设计实现使用了ZedBoard Zynq 7000 FPGA开发板。整个系统所使用的块RAM占总可用块RAM的51.43%。

下表展示了系统芯片利用率的表格表示:

| 资源 | 利用率 | 可用 | 利用%率 |

|---|---|---|---|

| FF | 18557 | 106400 | 17.44 |

| LUT | 9879 | 53200 | 18.57 |

| I/O | 21 | 200 | 10.50 |

| BRAM | 72 | 140 | 51.43 |

| DSP48 | 3 | 220 | 1.36 |

| BUFG | 2 | 32 | 6.25 |

芯片利用率的图形表示如下所示:

输入图像和从VGA显示器捕获的输出图像如图6所示:

:输入图像)

:输入图像)

:高斯滤波输出)

:高斯滤波输出)

:锐化滤波输出)

:锐化滤波输出)

:灰度输出)

:灰度输出)

:边缘检测滤波输出)

:平均滤波输出)

结论

基于网络服务器的图像滤波过程已通过树莓派‐FPGA接口成功完成。该基于物联网的图像处理系统使用Verilog编码设计而成。在此设计中,占用了可用块RAM总量的51.43%。我们观察到,实现基于网络服务器的图像处理滤波器所需的执行时间显著减少。

21

21

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?