理解代数重写在算术电路验证中的应用:一种比特流模型

摘要

—本文研究基于代数重写的算术电路验证的理论方面。其目标是增进在符号计算机代数背景下对算术电路验证中代数技术的理解。本文通过将电路执行的计算视为数字数据流,为算术电路验证问题提供了新的见解。在所提出的位流模型中,电路被建模为满足位流守恒定律的逻辑组件网络。我们证明了电路中数据流的值在整个电路中保持不变,并利用这一点独立于计算机代数论证来证明该重写技术的可靠性和完备性。该方法的效率通过在大型整数乘法器上取得的显著结果得以展示。验证系统和基准测试已发布于开源软件环境。

Index Terms —形式验证,代数重写,算术验证。

一、引言

尽管逻辑电路的验证已取得显著进展,算术电路和数据路径验证仍然面临巨大挑战。这可能归因于在不依赖计算成本高昂的布尔方法(如BDDs [1], SAT [2],和SMT [3])的情况下,难以高效地对算术设计进行模型化。基于算术电路实现的多项式表示的计算机代数技术似乎能够规避这一问题,并为分析算术电路和数据路径提供高效的解决方案。

这些技术主要有两种形式主导着该领域:一种基于格罗布纳基(Gröbner basis)的多项式约简;另一种基于代数重写。尽管基于代数重写的技術已提出数年,并被证明是算术电路验证中的领先方法,但其理论尚未得到充分发展。本文的目标是增进对代数重写技术的理解,并将其与成熟的计算机代数方法进行比较,以更清楚地解释其优势和效率。为此,我们提出了一种称为比特流的新模型,该模型将用于独立于计算机代数论证来证明重写技术的优势。同时引入了一个集成到ABC软件中的代数重写开源框架[13]。

本文的组织结构如下:第二节提供问题所必需的数学背景,第三节回顾该领域的先前工作。第四节详细描述了代数重写方案,并将其与Gröbner基多项式约简技术进行了比较。第五节通过引入比特流模型,为算术电路验证提供了新的见解。该模型为重写方案的可靠性与完备性提供了基础。结果和结论分别在第六节和第七节中给出。

II. 理论背景

本文所考虑的算术电路是指其计算可表示为输入变量多项式的电路。这些电路包括加法器、减法器、乘法器以及融合加乘电路。电路被建模为由互连的位级组件构成的网络,每个组件具有一组有限的二进制输入和一个或多个二进制输出。在本研究中,我们将重点关注使用单输出逻辑门的门级整数算术电路。

每个门被建模为一个多项式 $f_i \in \mathbb{Z}[X]$,其变量 $x_i \in X$ 属于 $\mathbb{Z}_2$。这类多项式通常被称为伪布尔多项式,因为它们是基于布尔变量、使用常规乘法和加法运算符的代数表达式。形式上,伪布尔多项式是一个整数值函数$f:{0, 1}^n\rightarrow \mathbb{Z}$。以下方程总结了基本布尔运算符的代数表示:

$$

\neg a= 1 - a \quad a \wedge b= a \cdot b \quad a \vee b= a+ b- a \cdot b \quad a\oplus b= a+ b- 2a \cdot b \tag{1}

$$

根据构造,每个表达式都计算出一个二进制值${0,1}$,因此能够正确地建模逻辑门的布尔函数。对于在标准单元技术中使用的更复杂的AOI(与‐或‐非)门,其模型可由这些基本逻辑表达式直接得到。例如,逻辑门$g= a\vee(b\wedge c)$的代数模型可以推导为$g= a+bc-abc$,等等。类似地,三输入或门可表示为$z= a+b+c-ab-ac-bc+abc$,三输入异或门可表示为$z= a+b+c-2ab-2ac-2bc+4abc$,等等。

为了系统地操纵多项式,需在单项式上引入一种项序“>”。设$f, g$为多项式,并令$lt(g)$表示在此序下多项式 $g$的首项。如果$t$是$f$的一个非零项,且可被$g$的首项整除,则称$f$模$g$约简为$r$,记作

$$

f \xrightarrow{g} r

$$

其中$r= f - \frac{t}{lt(g)} \cdot g$。类似地,$f$可以关于一组多项式$B={f_1,…, f_s}$进行约简,这称为模$B$的多项式约简。它被符号化地表示为$f \xrightarrow{+}_{B} r$,其中$r$是余式(也称为标准型),使得$r$中没有任何项能被$B$中任意多项式的首项整除。符号$+$表示该约简过程是迭代的,逐个使用$B$中的多项式。

设 $B={f_1,…f_s}$为表示电路元件的一组多项式,并设 $R$为多项式环 $R= \mathbb{Z}[X]$。那么,由 $f_i$生成的所有多项式的集合

$$

J= \langle f_1,…, f_s \rangle \quad (\text{其中 } f_i \in \mathbb{Z}[X])

$$

称为一个理想,其定义为

$$

J= \langle f_1,…, f_s \rangle= h_1f_1+…+ h_sf_s: h_i \in R \tag{2}

$$

多项式$f_1,…, f_s$称为理想$J$的基,或生成元。在本例中,每个生成元都是一个电路模块的多项式模型,而生成元的集合可被视为该电路的实现。给定一个理想$J$,方程组$f_1(x_1,…, x_n)= 0; …, f_s(x_1,…, x_n)= 0$的所有公共解的集合称为簇,记作$V(J)$。从电路的角度来看,簇包含了由任意主输入集合在所有可能输入组合下产生的电路的所有信号值。

该电路的功能规范也被定义为 $\mathbb{Z}[X]$中的一个多项式。例如,乘法器电路 $R= A \cdot B$的规范可以写成关于输入和输出变量的多项式 $F= R−A·B$。其中,$A$,$B$和 $R$是符号化的位向量变量,每个都表示为一个多项式,例如$A=\sum_{i=0}^{n−1} 2^ia_i$等。

在计算机代数的术语中,算术电路验证问题可以表述如下[6][7][8][9]:给定一个由一组生成元(实现)$B={f_1,…, f_s}$表示的电路和规范 $F$,功能验证的目标是证明该实现($B$)满足规范($F$)。这意味着$F= 0$的解与 $V(J)$一致,或者等价地说,$F$在 $V(J)$上消失¹。因此,该问题被建模为一个理想成员测试,用于判断多项式 $F$是否属于由 $B$生成的理想$J$,即是否成立 $F \in J$[14][6][7]。

给定一个理想$J= \langle f_1,…, f_s \rangle$,要测试是否$F \in J$,将多项式$F$依次除以$f_1,…, f_s$。目标是使用$f_1,…, f_s$中的某个首项来消去 $F$的首项(s)。这种约简会得到一个多项式余式$r= F - \frac{lt(F)}{lt(f_i)}$,其中首项$()$已被消去。如果余式,则实现满足规范。然而,如果,则无法得出此结论:仍可能属于,但不能被中的多项式整除。也就是说,生成元集合可能不足以约简,但电路仍可能是正确的。为了检查在给定理想下是否可约简为零,必须计算一个规范的生成元集合$G={p_1 ,…, p_t}$,称为Gröbner基,使得

¹多项式$f$在集合$V$上消失,如果$\forall a \in V, f(a)= 0$。

$$

\langle p_1,…,p_t \rangle= \langle f_1,…, f_s \rangle

$$

集合 $G$是理想 $J$的Gröbner基,当且仅当 $\forall F \in J, F \xrightarrow{+}_{G} 0$[15]。简而言之,Gröbner基对于明确回答 $F \in J$这一问题至关重要。

一种已知的用于计算Gröbner基的算法称为布赫伯格算法[16]。给定某个基 $B={f_1,…, f_s}$,它生成另一个基$G={p_1,…,p_t}$,使得理想$\langle p_1,…,p_t \rangle= \langle f_1,…, f_t \rangle$,因此 $V(\langle G \rangle)= V(\langle B \rangle)$。布赫伯格算法在计算上非常昂贵,因为它通过在 $B$中的所有多项式对上执行昂贵的约简操作来计算所谓的S-polynomials。人们已经开发出多种用于计算Gröbner基的算法,包括F4[17],但总体而言,该过程仍然计算代价高昂。

III. 相关工作

算术电路验证方面的工作由[4]和[5]率先开展,他们将计算机代数与代数几何中的概念应用于建模核心验证问题。在[5]中,算术电路被建模为一个由算术运算符组成的网络,例如从门级实现中提取出的半加器和全加器、比较器以及乘积生成器。这些运算符使用算术位级(ABL)表达式进行建模,即 $B={B_j}$。[5]的作者(以及[7])表明,对于任意组合电路,如果门方程 $B$的项按照逆拓扑序排列({输出}>{输入}),则 $B$中多项式的首项互素。因此,相应的集合 $B$已经构成一个Gröbner基(GB),从而避免了完整规范基的计算。验证问题通过将规范对 $B$取模约简为标准型,并检测其是否在 $\mathbb{Z}

2^n$上消失来解决。在[6]中,通过施加布尔约束 $\langle x^2 - x \rangle$将解限制于二元变量,并在商环 $Q= \mathbb{Z}_2^n[X]/\langle x^2 - x \rangle$上使用流行的计算机代数系统Singular[18]求解该问题。然而,这种方法仅限于完全由半加器和全加器组成的电路,且这些组件必须首先从门级实现中提取出来。在实践中,这通常是整个过程中最耗时的部分,而且并不总是可行的,尤其是在高度位优化的实现中。在[7]中,验证问题同样被表述为理想成员测试,但应用于伽罗瓦域(GF或 $\mathbb{F}

{2^q}$)算术电路。研究表明,在GF中,当规范 $F$和电路实现的理想 $J$位于 $\mathbb{F}_{2^q}$时,该问题可归约为测试 $F \in (J+ J_0)$是否属于更大的理想$(J+ J_0)$,其中

$$

J_0 = \langle x^2 -x \rangle

$$

是 $\mathbb{F}_2$中消失多项式的理想。添加 $J_0$本质上是将簇 $V$限制在$\mathbb{F}_2$中的解,即限制为 $V(J) \cap V(J_0)$[19]。$J_0$的多项式随后被称为域多项式。类似于[5],[7]的作者根据电路的拓扑结构导出项排序,从而使多项式集合 $B$(电路实现)成为一个Gröbner基,从而

IV. 多项式重写与格罗布纳基约简

在本节中,我们分析了用于整数算术电路形式验证的两种主要技术之间的关系:[12]的代数重写与基于计算机代数的[6][8][9]技术。

算术电路计算的功能表示为主输入变量中的一个规范多项式,记为 $F_{spec}$。例如,一个 $n$位无符号整数乘法器的规范,其输入为 $Z= A·B$和$A=[a_0, · · ·, a_{n−1}]$,可由

$$

F_{spec}=\sum_{i=0}^{n−1} \sum_{j=0}^{n−1} 2^{i+j}a_ib_j

$$

描述。计算的结果存储在主输出位中,也以一个多项式形式表示,称为输出特征,记为 $S_{out}$。通常,该多项式是线性的,由设计者提供的输出 $m$比特编码唯一确定。例如,对于具有 $m$个输出位的有符号二进制补码算术电路,其输出特征为

$$

S_{out}= −z_{m−1}2^{m−1}+\sum_{i=0}^{m−2} 2^iz_i

$$

该电路被实现为一个逻辑门网络$G$,每个逻辑门被建模为一个从公式(1)导出的多项式 $g_i$。表示给定门的多项式在其所有满足该门输入和输出组合的情况下求值为零。

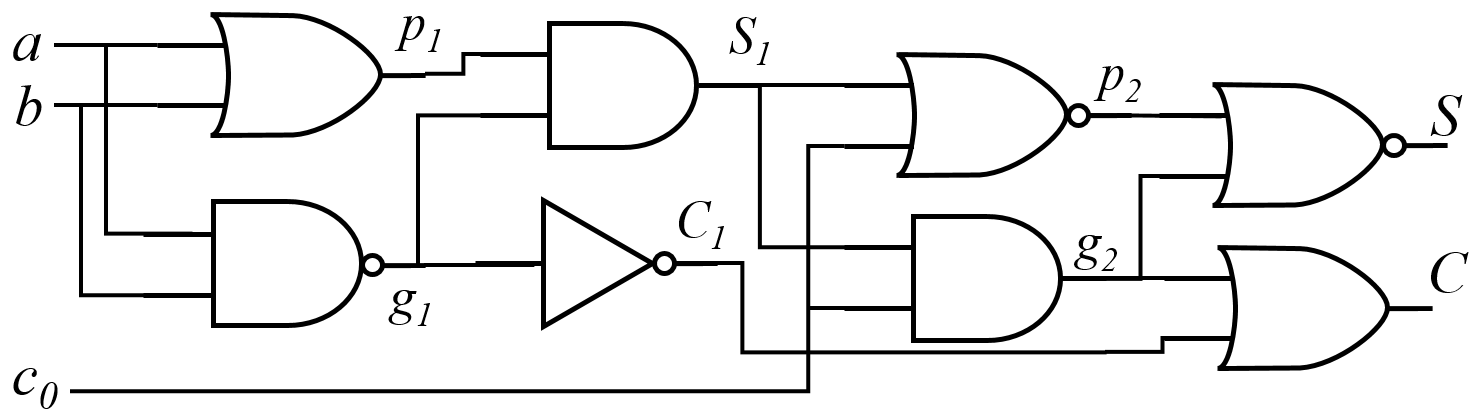

本节其余部分比较两种类型的多项式约简:1)基于Gröbner基(GB)约简,以及2)基于代数重写的约简。结果表明,尽管这两种方法在最坏情况下都具有指数复杂度,但重写方法更高效。这一点将通过图1所示的全加器的一种(非标准)门级实现来说明。

以下多项式集合$G={f_i}$表示该电路的门级实现。我们称此集合为$G$,以表明其构成一个Gröbner基。每个多项式的项按顺序排列,使得首项项是门的输出,这自动使其成为Gröbner基。

$$

\begin{aligned}

f_1 &= p_1 −(−ab+ a+ b) \

f_2 &= g_1 −(−ab+1) \

f_3 &= S_1 −p_1g_1 \

f_4 &= C_1 −(−g_1+1) \

f_5 &= p_2 −(S_1c_0 − S_1 − c_0+1) \

f_6 &= g_2 − S_1c_0 \

f_7 &= S −(p_2g_2 −p_2 − g_2++1) \

f_8 &= C −(−C_1g_2+ C_1+ g_2) \

f_9 &=(a^2 − a) \

&\cdots \

f_{17}&=(g_2^2 − g_2)

\end{aligned}

\tag{3}

$$

每个门多项式满足关系$f_i= 0$。门多项式$f_1,…,f_8$具有形式$f_i= v_i −tail(f_i)$,其中首项$lt(f_i) = v_i$是门$f_i$的输出,而$tail(f_i)$是该门关于其输入的逻辑规范。在此排序下,这些首项互素,从而使$G$构成一个格罗布纳基[6][7][9]。这一特性对于格罗布纳基约简和重写技术都至关重要。

$f_9$,…,$f_{17}$所表示的最后一组多项式代表域多项式 $J_0=\langle x^2 − x\rangle$,其中 $x$是信号 ${a, b, c_0,p_1, g_1, S_1, C_1,p_2, g_2}$之一。它们在约简过程中起着重要作用,在格罗布纳基约简中与代数重写方法中的处理方式不同。

A. 格罗布纳基多项式约简

在此方法中,对 $F$模 $G$的约简是通过使用高斯消元法,依次用某个多项式 $f_i \in G$的首项逐个消去 $F$中的项来实现的。该约简是在由 $G$和域多项式$J_0$导出的格罗布纳基上进行的。从数学角度来看,这意味着计算将在商环$\mathbb{Z}[X]/\langle x^2 − x\rangle$中进行:$x \in X$,即电路的所有变量(信号)的集合。

格罗布纳基约简算法如算法1所示。首先,多项式基 $G={f_1 ,…, f_m}$通过公式(1)从$N$导出,其中 $m$是$N$中逻辑组件的数量。电路中的所有变量按逆拓扑顺序排列,即从主输出到主输入,并且每个门的多项式从门输出到其输入进行排序。此外,依赖于共同变量(扇入)的门输出信号应彼此相邻排列,因为这将最大化潜在的项消去机会,并最小化中间多项式的大小。

例如,考虑在包含由一个与门$C= ab$和一个异或门 $S= a+ b−2ab$构成的半加器的电路中,对多项式$F= 2C+ S+....$进行约简。由于 $C$和 $S$都依赖于公共变量 $a, b$,连续地对它们进行约简将从多项式中消去乘积项 $ab$,从而得到 $F= a+ b+.....$。这在继续约简多项式的剩余项之前是有利的。

考虑到这两个基本排序规则,图1所示电路的多项式环的一种可能项序如下所示,其中花括号中的变量可以具有任意相对顺序。

$$

{S, C}>{p_2, g_2}>{S_1, C_1}>{p_1, g_1}>{a, b, c_0}\tag{4}

$$

待约简的表达式 $F$用输出特征 $S_{out}$与 $F_{spec}$之间的差值进行初始化。

算法1 Gröbner Basis Polynomial Reduction

输入:规范多项式 $F_{spec}$;以及门级网表 $N$

输出:余式 Rem

1: 使用公式(1)创建 $N$的基 $G={f_1,…,f_m}$

2: 从$N$生成$S_{out}$

3: 定义环并指定项序

4: 初始化$F \leftarrow S_{out} − F_{spec}$

5: 当$F \neq 0$时执行循环

6: 如果$\exists f_i \in G:lt(F)/lt(f_i) \neq 0$则

7: / 存在$f_i$,其首项可被$lt(F)$整除 /

8: $F \leftarrow F − \frac{lt(F)}{lt(f_i)} \cdot f_i$ // 多项式除法

9: else

10: / 没有$f_i$的首项能整除$F$,将$lt(F)$移动到$Rem$ /

11: $F \leftarrow F − lt(F)$

12: $Rem \leftarrow Rem+ lt(F)$

13: 结束如果

14:保持施加在环上的项序

15: 结束循环

16: 返回 Rem

格罗布纳基约简的主要部分在第5‐15行给出。该算法搜索 $G$中的一个多项式 $f_i$,使得 $f_i$的首项能整除当前 $F$的首项 $lt(F)$。如果存在这样的多项式,则会用它来约简 $F$,如第8行所示。否则,$lt(F)$将被移至余式 $Rem$(第 11 − 12行)。任何时候,当向多项式 $F$中添加新项(含中间变量)时(第8行),过程必须保持环上规定的项序。当 $F$变为空(无论是被约简还是被移至 $Rem$)时,约简过程终止。零余式是正确实现的证据,如第三节所述。

我们通过图1中的示例说明格罗布纳基约简过程。该电路的初始多项式为:

$$

F= 2C+ S −(a+ b+ c_0)

$$

公式(5)给出了一组步骤,用于通过图1电路中的门多项式 $f_i \in G$来约简$F$。在每一步中,$F$表示由前一个约简步骤得到的已约简多项式。为简洁起见,代换同时展示一对变量。例如,$F/(C, S)$表示使用 $C$和 $S$这两个变量进行约简

$$

\begin{aligned}

F &= 2C+ S −(a+ b+ c_0) \

1)\ F/(S, C)&= 2(−C_1g_2+ g_2+ C_1)+(p_2g_2 −p_2 − g_2+1)−(a+ b+ c_0) \

&= p_2g_2 −p_2 − 2g_2C_1+ g_2+2C_1 −(a+ b+ c_0)+1 \

2)\ F/(p_2, g_2)&=(S_1c_0 − S_1 − c_0+1)S_1c_0 −(S_1c_0 − S_1 − c_0+1)− 2S_1C_1c_0+ S_1c_0+2C_1 −(a+ b+ c_0)+1 \

&= S_1^2c_0^2 + S_1c_0 − 2S_1C_1c_0+ S_1+2C_1 −(a+ b) \

3)\ F/(S_1^2 − S_1)&= −2S_1C_1c_0+ S_1+2C_1 −(a+ b) \

4)\ F/(S_1, C_1)&= −2(p_1g_1)(−g_1+1)c_0+ p_1g_1+2(−g_1+1)−(a+ b) \

&= −2(−p_1g_1^2+ p_1g_1)c_0+ p_1g_1 − 2g_1 −(a+ b)+2 \

5)\ F/(g_1^2 − g_1)&= p_1g_1 − 2g_1 −(a+ b)+2 \

6)\ F/(p_1, g_1)&=(−ab+ a+ b)(−ab+1)− 2(−ab+1)−(a+ b)+2 \

&= a^2b^2 − a^2b − ab^2+ ab \

7)\ F/(a^2 − a)&= 0

\end{aligned}

\tag{5}

$$

多项式$f_8, f_7$。在环上规定的项序,参见公式(4),在整个约简过程中保持不变。

域多项式 $J_0=\langle x^2 − x\rangle$的作用是保持每个变量为布尔值,在步骤2、4和6中(以粗体显示)可以观察到该效果。约简的结果为 $Rem= 0$,表明该电路实现了规范中指定的功能,即一个全加器。

B. 代数重写

代数重写是利用电路内部组件(逻辑门)的代数模型,将输出特征$S_{out}$转换为输入特征$S_{in}$的过程。该重写按逆拓扑序进行:从主输出(PO)到主输入(PI);因此也被称为逆向重写[12]。重写过程中得到的中间表达式也表示为关于表示电路内部信号的变量的多项式,这些多项式称为特征。根据构造方式,给定特征中的每个变量(从$S_{out}$开始)代表某个逻辑门的输出。重写变换只需将该变量替换为对应逻辑门的代数表达式。如果该变量属于包含其他变量的单项式,则将该表达式乘以其余项并展开为析取范式。随后通过合并相同单项式的项进行标准的多项式化简。

代数重写过程在算法2中进行了总结。首先,多项式基 $G={f_1,…,f_m}$通过公式(1)从 $N$导出,如同格罗布纳基约简中的做法。然后,$G$中的多项式按照逆拓扑顺序进行排序(第1‐2行)。在多种可能的拓扑顺序中,选择能够在重写过程中最大化早期消去数量的顺序。这样做可以最小化重写过程中中间多项式的规模(即“胖肚子”效应)[12]。其实现方式是将那些首项(门输出)依赖于共同变量的多项式保持在一起,如同格罗布纳基规约。待重写的表达式 $Sig$使用给定的输出特征 $S_{out}$进行初始化,该输出特征属于 $N$(第3‐4行)。

算法2 代数重写

输入:规范多项式 $F_{spec}$;以及门级网表$N$

输出:$(S_{in}== F_{spec})$,或计算出的特征值$S_{in}$

1: 使用公式(1)从 $N$推导出 $G={f_1,…,f_m}$

2: 对 $G$进行排序以最大化消去 // 预处理

3: 从$N$生成 $S_{out}$

4: 初始化$Sig \leftarrow S_{out}$

5: 对于$f_i$在 $G$中执行

6: $v \leftarrow lm(f_i)$ // $f_i$的首项是某个门的输出

7: 如果 $v \in Sig$则

8: / 在$Sig$中用$tail(f_i)$替换$v$ /

9: $Sig \leftarrow Sig(v \leftarrow tail(f_i))$

10: $x \leftarrow x^2$ // 对于所有$x$属于$Sig$

11: 结束if

12: 结束for

13: / 终止时,$Sig$仅由PIs组成 /

14: 如果$Sig == F_{spec}$返回True

15: 否则返回$S_{in} = Sig$

重写的主要部分(第5‐12行)遍历多项式 $f_i \in G$并执行所需的代换。具体而言,$Sig$中所有出现的 $v= lt(f_i)$都被替换为 $tail(f_i)$,随后可能对所得项进行展开。为了保持变量的布尔值,在重写过程中将 $Sig$中每个变量的次数降至1(第10行)。最后,该算法返回 $S_{in}= Sig$作为电路的导出签名。如果 $G$中多项式的项按逆拓扑序排列,则返回的多项式 $S_{in}$仅包含主输入(PI)变量,因此可以与 $F_{spec}$进行比较。

关于该重写方法的可靠性和完备性的详细证明见第五节。

虽然代数重写(如算法2所述)的主要目标是确定电路所实现的算术函数,但它也可用于根据已知规范验证电路。这可以通过重写 $F= S_{out} −F_{spec}$并检查其是否产生零来简单实现。我们将在第四节A部分使用这种重写模式,以将其与GB约简方法进行比较。

我们使用图1中的门级全加器电路示例来说明重写过程。输出

$$

F= 2C+ S −(a+ b+ c_0)

$$

1) $F/(S, C)= 2(C_1+ g_2 − C_1g_2)+(1 −(p_2+ g_2 −p_2g_2))−(a+ b+ c_0) = 2C_1+ g_2 − 2C_1g_2 −p_2+ p_2g_2+1 −(a+ b+ c_0)$

2) $F/(p_2, g_2)= 2C_1+ S_1c_0 − 2S_1C_1c_0 −(1 −(S_1+ c_0 − S_1c_0))+(1 −(S_1+ c_0 − S_1c_0))S_1c_0+1 −(a+ b+ c_0)$

$= 2C_1 − 2S_1C_1c_0+ S_1+ S_1c_0 − S_1^2c_0 − S_1c_0^2 −(a+ b) = 2C_1 − 2S_1C_1+ S_1 −(a+ b)$

3) $F/(S_1, C_1)= 2(1 − g_1)− 2(1 − g_1)(p_1g_1)c_0+ p_1g_1 −(a+ b)$

$= 2 − 2g_1 − 2(p_1g_1 − p_1g_1^2)+ p_1g_1 −(a+ b) = 2 − 2g_1+ p_1g_1 −(a+ b)$

4) $F/(p_1, g_1)= 2 − 2(1 − ab)+(a+ b − ab)(1 − ab)−(a+ b)$

$= ab − a^2b − ab^2+ a^2b^2= 0$

$$

\tag{6}

$$

电路的签名为 $S_{out}= 2C+ S$,由输出的二进制编码和规范$F_{spec}= a+ b+ c_0$确定。根据[12]中描述的排序规则,能够最小化中间多项式大小的最佳重写顺序为${(S, C),(p_2, g_2),(S_1, C_1),(p_1, g_1)}$,这与格罗布纳基约简中的顺序一致。括号中显示的信号可以按任意顺序进行重写,因为它们依赖于公共输入。公式(6)展示了该电路的重写步骤。以粗体显示的项表示在多项式化简过程中被约简为零的项。为简洁起见,每次变量代换对成对变量同时进行展示。例如:$F/(C, S)$表示使用多项式 $f_8, f_7$中的 $C$和 $S$变量对 $F$进行重写。

在重写过程中,可以观察到两种类型的化简:

合并相同单项式的项;例如,步骤1中的 $2g_2 −g_2= g_2$。这种简化也常用于格罗布纳基约简中。

将项$x^2$约简为$x$,因为信号变量是二进制的。这一点在以粗体显示的步骤2、步骤3和步骤4中可以看出。例如,在步骤2中有:

$$

S_1c_0 − S_1^2 c_0 − S_1c_0^2 + S_1^2 c_0^2 = S_1c_0 − S_1c_0 − S_1c_0+ S_1c_0= 0

$$

类似地,在步骤3中有:$(p_1g_1 −p_1g_1^2) = p_1g_1 − p_1g_1 = 0$,等等。这种简化比通过相应的域多项式$x^2 − x$对多项式进行除法运算更加简单且执行更快,后者是在计算机代数方法中所采用的方式。这是代数重写相比格罗布纳基约简具有更高效率的主要原因之一。

随后,最终结果将 $F= S_{out} −F_{spec}$归零,表明该电路正确实现了全加器。

需要注意的是,除了上述两种基本化简规则(重写具有公共输入的门,以及 $x^2 \rightarrow x$约简)之外,在重写过程中还可以通过分析门级网络的结构,对运行中的多项式 $Sig$应用一些更复杂的化简方法。例如,识别出某个信号 $g$是具有相同扇入输入的异或门和与门信号的乘积,便可对其进行约简将信号$g$简化为零。这种简化称为XOR-AND消失规则,已被[8]使用,但为了上述示意图的清晰起见,此处未予考虑。

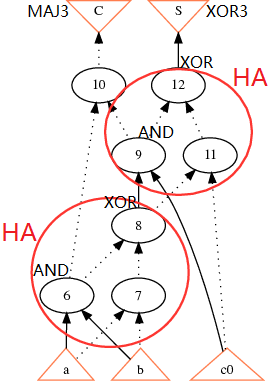

C. AIG重写

上一节中描述的代数重写技术可以通过使用电路的函数AIG(加法器‐反相器图)表示而非其门级结构来进行重写,从而进一步改进。本节简要概述了实现方法,详细信息见[21]。

AIG(与非图)是一种由双输入与门和反相器[13]组成的组合布尔网络。AIG的每个内部节点表示一个双输入与功能;图边带有标签,用于指示信号可能存在的取反。我们使用abc[13]的割枚举方法来检测具有公共变量集的异或门和多数(MAJ)函数;这些函数是加法器树的基本组件,而加法器树以某种形式存在于大多数算术电路中[21]。在检测出加法器AIG中的异或门和多数(MAJ)组件后,重写过程会跳过已检测到的加法器,从而显著加快重写过程。图2展示了来自图1的全加器(FA)电路的处理过程。在图2中,节点组(6,7,8)和(9,11,12)对应于半加器(HA)。以节点6和9为根的函数是多数(与)函数,而以节点12和8为根的函数是异或门。随后,节点12($S$)和节点10($C$)处的函数分别被识别为在共享输入 $a, b, c_0$上的三输入异或门和三输入多数门。

$S_{out} = 2C+S$在提取的XOR3和MAJ3节点上的AIG重写是平凡的,非线性单项式会自动被约去,如下所示:

$$

\begin{aligned}

2C+ S &= 2(ab+ ac_0 + bc_0 − 2abc_0) +(a+ b+ c_o −2ab−2ac_0 −2bc_0 +4abc_0) \

&= a+ b+ c_o

\end{aligned}

$$

最终特征与规范一致,这明显表明该电路是一个全加器。如本例所示,AIG重写所需的项数远少于标准代数重写。

数据结构:AIG重写在abc中通过多项式数据结构 Pln_Man_t实现

D. 两种方法的比较

从上述讨论中可以明显看出,格罗布纳基约简和代数重写这两种方法在执行多项式约简的意义上是等价的。GB约简方案通过除法(高斯消元)实现多项式约简,而代数重写则通过将门的输出变量代入该门的功能的多项式表达式来实现。

尽管GB约简方案的目标是将$F= S_{out} − F_{spec}$对 $G$进行格罗布纳基约简至0,但它也可用于通过将$S_{out}$对 $G$进行约简来提取算术函数,并将结果解释为电路的功能规范 $F_{spec}$。在代数重写方案中,目标是将$S_{out}$重写为$S_{in}$(即主输入中的表达式),并检查其是否与预期的规范$F_{spec}$一致。如果 $S_{in} = F_{spec}$,则电路正确;否则电路有故障。或者,如上所述,代数重写也可以像在GB方法中一样应用于$F= S_{out} − F_{spec}$。

代数重写中的变量代换(算法2的第9行)似乎比格罗布纳基约简中多项式除法的主要步骤(算法1的第 8行)更简单。另一方面,它需要对项进行额外的乘法运算,并展开为积之和。因此,这两个步骤的复杂度相当。这两种方法都避免了显式计算格罗布纳基,但通过不同的方式实现。在格罗布纳基约简中,通过设置环中的变量顺序,使所有变量按逆拓扑序排列,从而使实现集合成为一个格罗布纳基。而在代数重写方案中,多项式按逆拓扑序排序以实现重写。结果,两种方法都确保了多项式基成为格罗布纳基。然而,这两种方法之间存在一些影响其效率的本质差异。

GB约简方案需要将域多项式 $J_0=\langle x^2−x\rangle$添加到基 $G$中,以保持变量为布尔变量。这会增加格罗布纳基的大小,并导致每次迭代中的搜索空间更大。而在重写方案中,通过简单的数据结构将 $\langle x^2 − x\rangle$的约简问题简化为将 $x^2$降为 $x$(见算法2的第10行)。

在代数重写方案中,门多项式$f_i \in G$按照拓扑顺序排列(算法2的第5行),使得每个门多项式$f_i$恰好被使用一次。所选的多项式通过简单的字符串替换执行重写,之后不再需要。相比之下,在格罗布纳基约简的每一次迭代中,必须搜索一个能够整除$F$在约简过程中首项的多项式$f_i$。虽然原则上格罗布纳基约简也可以在门多项式的有序列表上进行,但这不适用于约简所需的域多项式$\langle x^2−x\rangle$。由于中间信号在非线性项$x^k$中的出现是不可预测的,因此无法对格罗布纳基约简中的域多项式列表进行预排序。

V. 比特流模型

本节对算术电路验证问题提供了新的见解,其中将电路执行的计算视为数字数据的流。此处的目标不是引入任何新算法,而是提出一种解释,说明计算在算术电路中的传播方式。这种解释将独立于计算机代数论证,为代数重写方法的可靠性与完备性提供论证。

该电路被建模为通过电信号或导线连接的逻辑和/或算术组件的无环网络。从数学上讲,信号被表示为变量,记作 $X$;它们包括内部信号、主输入(PI)以及主输出(PO)。

术语signals和variables将根据上下文(电路的结构视图与功能视图)互换使用。电路的每个组件都由其characteristic function(特征函数)描述,该特征函数是一种伪布尔多项式函数,用于关联组件的输入和输出。布尔逻辑门的特征函数由方程1给出。例如,或门$z= a \vee b$的特征函数是$z= a+ b − ab$。类似地,半加器(HA)的特征函数是$2C+ S= a+ b$,等等。

术语flow直观上被理解为某种物理实体(如电流或流体)在网络中的移动。在这里,它指的是数字数据(被评估为0或1的电压)的流动,其容量以比特为单位衡量,每个比特为其值贡献一个流单位。该流从主输入开始,向主输出传播,并根据电路组件的特征函数在内部进行分配。例如,一个全加器接收三个比特的输入流,$a, b, c$,并根据其特征函数将此流分配到输出:$a+ b+ c= 2C+ S$。每个变量关联的系数表示其“容量”,即能通过相应信号的流的最大值。在半加器或全加器中,每个输入位的权重为1,输出位 $C$和 $S$的权重分别为2和1。对于一个逻辑门,输入和输出位的权重均为1。

利用流守恒定律来验证算术电路的思想已在[11]中提出。然而,该方法仅适用于由半加器和全加器构成的算术电路,其中电路元件和规范被建模为线性表达式。本文中,我们将此思想扩展到计算作为多项式的算术函数的任意整数算术电路。

电路中流的值通过代数重写过程中生成的多项式(签名)来表示。方程(5)和(6)就是这类多项式的示例。主输入处流的值由规范多项式 $F_{spec}$表示,而主输出处流的值由输出特征 $S_{out}$表示。在电路任意割处(定义见下文)流的值则用与相应信号相关的变量所构成的多项式表示。该值可以从代数重写的每一步生成的多项式计算得到。我们将证明,算术电路中由这些多项式表示的流的value在整个电路中是不变的。

原则上,电路可以由任意组件构成,包括单输出逻辑门以及多输出算术模块,例如半加器和全加器;或任何其输入/输出关系可定义为多项式的模块。本文中,我们将其范围限定在具有单输出逻辑门的门级算术电路。在本节其余部分,对多项式 $S_i$、$S_{in}$、$S_{out}$或 $x$的任何引用均假定它们已在域多项式$\langle x^2 − x\rangle$上被约简,这在代数重写过程中通过将 $x^2$替换为 $x$隐式实现(参见第四节-B)。显然,流的值不会因该变换或任何移除取值为零项的简化而受到影响,因为这不会改变多项式的值。

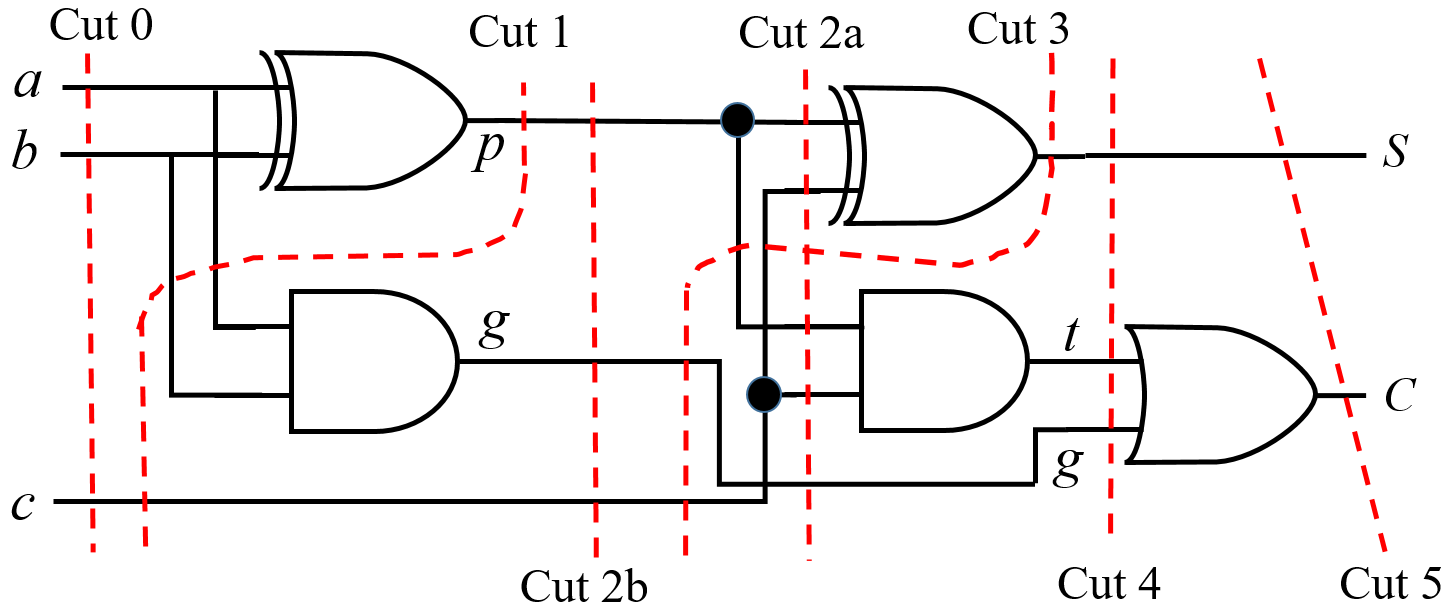

考虑在代数重写过程的步骤 $i$中生成的多项式 $P_i$。可以观察到,位于 $P_i$支撑集中的变量 $X_i$对应于电路中的一个割。使用网络流术语,该割是一组信号,它将电路划分为两个子集:一个包含其输入通过传递方式连接到主输入 PI的门,另一个包含其输出通过传递方式连接到主输出 PO的门。这种分离是逆向重写固有的特性:从输出特征多项式 $P_i= S_{out}$开始,$P_i$中代表某个门$g_k$输出的变量$x_k \in X_i$被其输入上的多项式所替换。从结构观点来看,这相当于将割从门的输出移动到其输入。从这一角度来看,多项式$P_i$也可视为割 $C_i$的特征,记为 $S_i$。

公式(5)和(6)中的多项式表达式是图1中全加器电路的割集特征的示例。之前定义的输入和输出特征 $S_{in}$和 $S_{out}$,分别是与主输入 PI和主输出 PO相关的边界割集的特征。以下示例说明了多项式与割重写之间的关系。

例1

:图3展示了一个带有割集的全加器电路(FA)。与割集${Cut_5 ,...., Cut_0}$相关的特征${S_{out}, S_4, S_3, S_2, S_1, S_{in}}$在公式7中给出。这些特征是通过对 $Cut_5$的输出特征 $S_{out} = 2C+ S$在电路中逐步重写得到的。具体来说,特征 $S_{out}$通过将变量 $C$替换为或门的表达式 $C= g+ t − gt$,从而转换为$Cut_4$的特征 $S_4$,得到特征$S_4 = 2(g+ t−gt)+ S$。然后,该特征通过在与门 $t= cp$上进行重写,进一步转换为 $S_3$,依此类推,直到达到主输入。以下特征是通过对电路进行连续重写得到的,重写的顺序与第四节中讨论的排序规则一致。此外,通过应用[8]的异或-与简化规则(即 $pg= 0$),此处对$S_3$的表达式进行了化简。

$$

\begin{aligned}

S_{out} &= 2C+ S \

S_4 &= 2(g+ t − gt)+ S \

S_3 &= 2(cp+ g − cpg)+ S = 2(cp+ g)+ S \

S_2 &= c+ p+2g \

S_1 &= c+ p+2ab \

S_{in} &= c+ a+ b

\end{aligned}

\tag{7}

$$

注意,与网络流模型不同,[11]某个割 $C_i$的签名 $S_i$不是其信号 $X_i$的线性组合,而通常是变量 $X$的一个非线性多项式 $S_i$。

我们现在引入流值的概念,它是衡量跨越一个割的比特流容量的指标。

定义1 :对于变量的给定赋值 $X_i$,具有签名 $S_i$的割 $C_i$的值是其签名 $S_i$在 $X_i$处求值得到的整数值。记作 $V(S_i)(X_i)$。

需要注意的是,割中变量$X_i$的值不能任意取值,而只能取那些可以从 PI的位值推导出的值。为此,我们引入以下定义。

定义2 :如果 $X_i$中变量的赋值是从主输入 $X_{PI}$的赋值得出的,则称该赋值为合法的,记作$[X_i]$。在这种情况下,我们说$[X_i]$与 $X_{PI}$兼容。

由此,我们将使用符号$V(S_i)[X_i]$来表示仅针对$legal$赋值的$X_i$的割的值。我们可以说两个赋值$[X_i],[X_j]$是$compatible$的,如果它们都源自$相同$的值$X_{PI}$。

引入合法性概念的原因是,只能针对电路实际生成的信号值来推理割集上的流。

示例2 :表I显示了图 6中全加器电路在所有可能的PI赋值下,每个割集处的流值。这些流值通过将给定的$[X_i]$值代入 $S_i$的表达式而得到。

一个重要观察是,对于 $X_{PI}$的给定赋值,所有割集(及其特征)的值都是不变的。

定义3 :两个具有特征$S_i, S_j$的割$C_i, C_j$是同余的,记为$C_i \cong C_j$,如果对于每一对兼容赋值$[X_i] ,[X_j]$,它们的值相同,即$V(S_i)[X_i] = V(S_j)[X_j]$。此时,我们也称相应的特征是同余的,记为$S_i \cong S_j$。

表I 正确电路中割集的流值。

$S_5= S_{out}= 2C+ S;\ S_0= S_{in}= a+ b+ c= F_{spec}$

| c | a | b | p | g | t | C | S | $S_5$ | $S_4$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ | $F_{spec}$ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 3 | 3 | 3 | 3 | 3 | 3 | 3 |

$Cuti$处的流值$V(S_i)$

定理1 :给定一对割$C_i, C_j$,使得$C_i$被转换为 $C_j$,或等价地,$S_i$通过代数重写被重写为$S_j$,则这两个割是同余的。即$S_i \rightarrow S_j \Rightarrow S_i \cong S_j$。

证明 。割$C_i(X_i)$可以通过对逻辑门进行一系列代数重写变换转换为另一割$C_j(X_j)$,每个变换由某个多项式$g= v − tail(g)$描述。在重写过程中,源割中变量$v$的每次出现(最初为$C_i$)都被目标割中的$tail(g)$所替换(最终为$C_j$)。由于多项式$g$满足由公式(1)提供的关系$g= v − tail(g)= 0$,因此有$v= tail(g)$。于是,对于所有满足此关系的变量$v$以及$tail(g)$中的变量取值,均有$V(S_i)= V(S_j)$。因此,对于所有兼容的赋值$[X_i],[X_j]$,均有$V(S_i)[X_i]= V(S_j)[X_j]$,从而根据定义6,它们是同余的,$S_i \cong S_j$。

例3 :定理1指出了算术电路中割集上位流守恒的一个重要性质。表I给出了图3中全加器电路各个割集的取值。我们可以看到,在原始(正确)电路中,每个割集的特征值,包括输入和输出特征,在所有主输入赋值下都相同。

请注意,即使两个割集无法通过重写相互得到,它们也可能是同余的。例如,在图3中,$Cut_3={S, c, p, g}$和割集${p, c, t, g}$(彼此交叉,图中未显示)无法通过重写相互推导,因为不存在能够将其中一个转换为另一个的门;然而,由于它们都可以通过对 $S_{out}$进行重写得到(尽管经过不同的门集合),因此它们也是同余的。对此,我们有以下推论:

推论1 : 电路中的所有割集相互全等。特别是,$S_{out} \cong S_{in}$。

证明 。根据定理1,电路中的任意割 $C_i$都与主输出处的割 PO同余,因为它可以通过从 PO逆向重写得到。任何其他割 $C_j$也与 PO同余。即根据同余的定义,$V(S_i)[X_i] = V(S_{PO})[X_{PO}]$且$V(S_j)[X_j]= V(S_{PO})[X_{PO}]$,因此对于任意割集 $C_i, C_j$(包括 $S_{in}$和 $S_{out}$),均有 $S_i \cong S_j$。因此,所有割集都是同余的,并构成一个等价类。

推论1基本上指出,在电路中任意割处测得的流的值在整个电路中是恒定的。

我们现在需要讨论如何区分功能正确的电路与有故障的电路。如果电路的实现满足规范,则称该电路是功能正确的;或者等价地说,对于所有可能的输入赋值,电路计算出的值与规范所提供的值相同。使用代数重写的术语,我们可以将此定义形式化如下:

定义4 :如果对于每个主输入赋值 $X_{PI}$,主输出中编码的结果 $X_{PO}$满足条件$V(S_{out})[X_{PO}]= V(F_{spec})[X_{PI}]$,则该电路是功能正确的。

以下定理指定了电路功能正确的充分且必要条件。

定理2 : 当且仅当代数重写输出特征 $S_{out}$所计算出的输入签名 $S_{in}$与功能规范相同,即 $S_{in}= F_{spec}$时,该电路才是功能正确的。

证明 . 若部分(可靠性):设 $S_{in}= F_{spec}$,这意味着对于所有可能的主输入赋值 $X_{PI}$,均有 $V(S_{in})= V(F_{spec})$。由于根据推论1,$S_{in} \cong S_{out}$,即 $V(S_{in})= V(S_{out})$,因此对于 $X_{PI}$的所有可能取值,均有 $V(S_{out})= V(F_{spec})$。也就是说,该电路是功能正确的。

仅当部分(完备性):设该电路是功能正确的,即对于$X_{PI}$的所有取值,均有 $V(S_{out})= V(F_{spec})$。由于$S_{out} \cong Sin$,因此对于所有输入 $X_{PI}$的赋值,均有 $V(Sin)= V(F_{spec})$。这反过来意味着 $S_{in}= F_{spec}$。此外,重写过程总是会终止:作为有向无环图的电路没有环路,且重写步骤的数量等于门的数量。因此,该方法也是完备的。

需要强调的是,上述论证仅对在域多项式$J_0$上约简的伪布尔多项式有效。已知此类多项式具有唯一的多项式表示,因此两个多项式只有在完全相同时才会计算得到相同的值。

示例4

:为了说明故障电路的情况,其中$S_{in} \neq F_{spec}$,再次考虑图3中的全加器示例,其中与门 $g= ab$被替换为或门 $g= a+b−ab$。这导致割集的特征发生变化,如下所示(注意,在此电路中与-异或简化$pg= 0$不适用):

$$

\begin{aligned}

S_{out} &= 2C+ S \

S_4 &= 2(g+ t − gt)+ S \

S_3 &= 2(cp+ g − cpg)+ S \

S_2 &= c+ p+2g − 2cpg \

S_1 &= c+ p+2(a+ b− ab)− 2cp(a+ b− ab) \

S_{in} &= c+3(a+ b)− 4ab− 2c(a+ b− 2ab)

\end{aligned}

\tag{8}

$$

通过此重写获得的输入特征现在为:$S_{in}= c+ 3(a+ b)− 4ab− 2c(a+ b− 2ab)$,与电路规范 $F_{spec}= a+ b+ c$不匹配。对于每个赋值 $X_{PI}$,各割集的流值如表II所示。该表证实所有割集 ${S_5, S_4, S_3, S_2, S_1, S_0}$均为同余;并且根据定理1,任意割集处的流值对于任何 PI赋值均为常量。然而,对于某些 $X_{PI}$的赋值,其流值与正确电路中的流值不同(如 $F_{spec}$列所示),证明该电路有故障。

表II 故障电路中的流值($g$的与门被或门替换);

$S_5= S_{out}= 2C+ S; S_0= S_{in} \neq F_{spec}$

| c | a | b | p | g | t | C | S | $S_5$ | $S_4$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ | $F_{spec}$ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 3 | 3 | 3 | 3 | 3 | 3 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 3 | 3 | 3 | 3 | 3 | 3 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 3 | 3 | 3 | 3 | 3 | 3 | 3 |

$Cuti$处的流值$V(S_i)$

总之,在计算多项式的电路中,从 $PI$到 $PO$的流值在整个电路中是常量。在功能正确的电路中,该流的值等于 $F_{spec}$的值;而在故障电路中,流值与 $F_{spec}$的值不同,但所有割集仍保持同余。

如果电路正确,$S_{in}$将与规范$F_{spec}$匹配;否则,该算法将报告电路有故障,并返回计算出的特征值 $S_{in}$。

VI. 结果

我们的代数重写算法已使用C语言实现,并集成到 ABC工具[13]中,该算法在AIG数据结构上执行。我们开发了一个基于ABC[13]作为后端²的代数重写 (ARTi)系统开源框架,用于算术电路验证,以实现开放访问和可重复性。

实验在[9][10]³中发布的基准测试上进行。为了公平比较,我们在我们的平台上重新编译了它们的C语言代码,并使用Singular v4.1.1[18]对其进行评估。实验在配备 Intel(R) Xeon CPU E5-2420 2.20 GHz x24和1 TB内存的PC上进行。内存溢出(MO)限制为100 GB,超时(TO)限制为3600秒。如果电路包含超过32,767个环变量,Singular将报告错误状态(ES)。

乘法器在未进行综合和工艺映射情况下的验证结果包含在表III中,而包含工艺映射的结果列于表四。

ARTi列中的结果是针对三种类型的电路btor, sp-ar-rc以及由abc生成的乘法器,使用以下命令集生成的:

a)

read btorXX.aig;&get; &poly n -v

;

b)

read sp-ar-rcXX.aig; &get; &atree; &poly n -v

;

c)

gen -N XXX -m abcXXX.blif; &get; &poly n -v

;

命令

&polyn

包含多种重写选项,例如使用结构化门级网表、AIG数据结构、有符号或无符号电路、详细级别(-v)、输出信号的自动或手动指定等。更多细节可参考ABC工具中的命令

&polyn − help

。加法器树的提取由命令

&atree

调用。

表III 综合前乘法器的CPU验证时间(单位:秒)。ES = 表示Singular报告的错误状态。

| 设计 | ARTi | [9] | [10] |

|---|---|---|---|

| btor-16 | 0.01 | 0.5 | 0.01 |

| btor-32 | 0.02 | 11.7 | 0.3 |

| btor-64 | 0.1 | 725 | 4.0 |

| btor-128 | 0.5 | ES | ES |

| sp-ar-rc16 | 0.01 | 1.1 | 0.01 |

| sp-ar-rc32 | 0.1 | 35.5 | 0.3 |

| sp-ar-rc64 | 0.4 | 1312 | 4.6 |

| sp-ar-rc128 | 1.6 | ES | ES |

| abc-256 | 0.7 | ES | ES |

| abc-512 | 3.7 | ES | ES |

表四 使用不同库的综合及工艺映射乘法器的CPU验证时间(单位:秒)。# GT =门类型数量。FI≥5=具有扇入≥5的门的数量。

| 设计 | ARTi | #GT | FI≥5 | [9] | [10] |

|---|---|---|---|---|---|

| btor64-resyn3-nomap | 0.1 | - | - | 711 | 4.2 |

| abc64-resyn3-nomap | 0.1 | - | - | 801 | 4.0 |

| btor128-resyn3-nomap | 0.3 | - | - | ES | ES |

| abc128-resyn3-nomap | 0.1 | - | - | ES | ES |

| btor64-resyn3-map-简单 | 0.3 | 7 | 0 | 1073 | 418 |

| abc64-resyn3-map-简单 | 0.1 | 7 | 0 | 1071 | 415 |

| abc128-resyn3-map-简单 | 1.8 | 7 | 0 | ES | ES |

| abc64-resyn3-map-14纳米 | 29 | 15 | 17 | TO | TO |

| abc64-resyn3-map-7纳米 | MO | 24 | 9,791 | TO | TO |

| abc128-resyn3-map-14nm | 400 | 15 | 1,008 | ES | ES |

| abc128-resyn3-map-7nm | MO | 23 | 26,600 | ES | ES |

ARTi [9] [10]

我们无法直接将我们的结果与[20]的结果进行比较,因为缺乏基准测试以及无法访问他们的代码。这篇发表于 1995年的论文指出,一个64位门级乘法器可以通过重构为*BMD,在SPARCstation 10/51上用3至6小时完成验证,这在当时是一个令人印象深刻的结果。我们尝试表示具有规范表示(如*BMD或TED)的大型算术电路并未成功。

七、结论

该论文探讨了基于符号计算机代数上下文中的代数重写进行算术电路验证的理论方面。文中对两种方法进行了详细比较,并解释了为何重写方案比GB约简方案更高效。引入了位流模型以形式化证明该重写方法。

代数重写有两种模式:1)针对已知规范的验证;以及2)从电路结构中提取规格。如果电路的规范是已知的,则需要将计算出的输入特征与该规范进行比较。虽然可以使用标准多项式表示(如TED或BMD)来进行这种比较,但也可以通过重写输出和输入特征之间的比较,即重写 $S_{out} − F_{spec}$而不是 $S_{out}$,从而完全避免比较。对于正确的电路,此类重写的结果应为零。非零结果则表明存在缺陷。当规范未知时,计算出的输入特征提供了电路的功能(无论是否有缺陷)。对于有故障的电路,在重写过程中中间多项式的大小可能变得大到难以接受,有时甚至导致计算无法完成。这本身就可以作为电路可能有故障的警告信号。通常,断定电路不正确并识别缺陷是一个具有挑战性的问题。

已有若干尝试通过比较反向和正向重写的结果[22],或通过分析计算出的输入特征与给定规范之间的差异[23]来识别缺陷。除有限域(GF)算术电路[24][25]这一显著例外之外,算术电路的调试仍然是一个开放性问题。

本文提出的位流验证模型本身并未提供任何特定的算法方法,但它对电路执行的计算给出了一个有趣的解释。它还为基于重写的验证正确性提供了证明依据:借助位流模型,代数代数重写被证明是可靠且完备的。该方法可用于验证任意算术电路,在任意抽象层次上(不仅限于门级),只要其功能规范 $F_{spec}$和输出编码 $S_{out}$可以表示为多项式。一个包含多种逆向重写选项的开源框架已公开发布。

²源码和示例:https://github.com/ycunxi/abc

³http://fmv.jku.at/algeq/

55

55

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?