作者的话

早就想写点这方面内容了,14PIN的JTAG设计,是ADI从2000年至今一直延续下来的一个JTAG标准设计,很多兄弟在做硬件设计的时候,最常问的一个问题就是:JTAG接口定义是什么?更多的只知道抄原厂评估板的参考设计,而并不是非常了解这个JTAG,导致设计的JTAG不能正常使用,所以我觉得有必要写一下了。

硬件示范

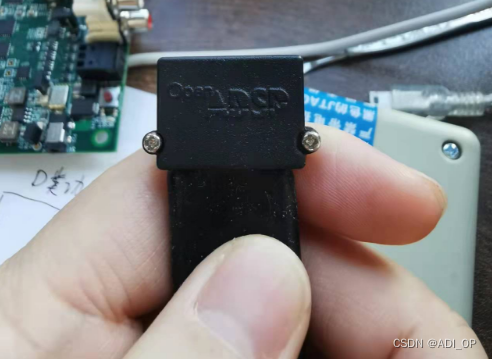

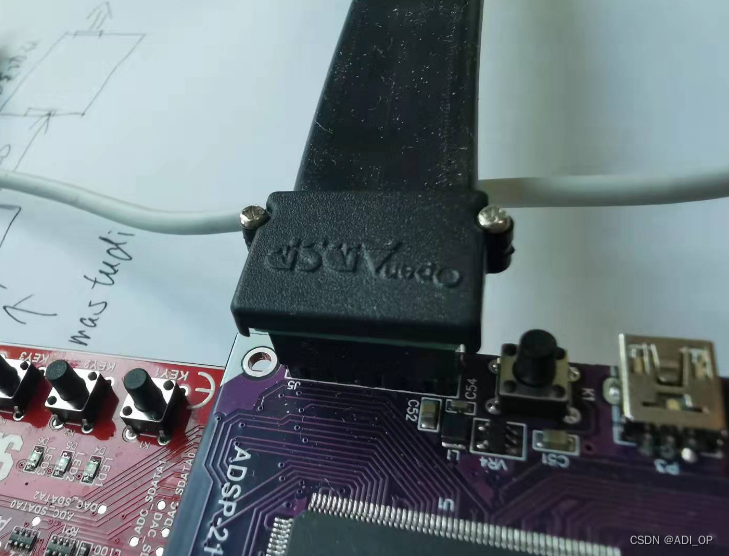

仿真器型号:AD-HP530ICE(ADI DSP专用仿真器)

产品链接:https://item.taobao.com/item.htm?spm=a1z10.5-c.w4002-5192690539.11.4e02bfa3AJxg1C&id=38007242820

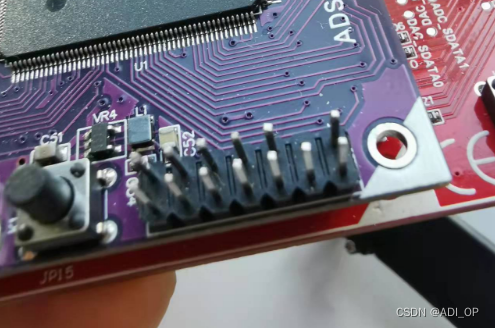

目标板:ADSP-21489EVB

产品链接:https://item.taobao.com/item.htm?spm=a1z10.5-c.w4002-5192690539.13.6c1269383xEOab&id=539694123232

JTAG 仿真器接口设计

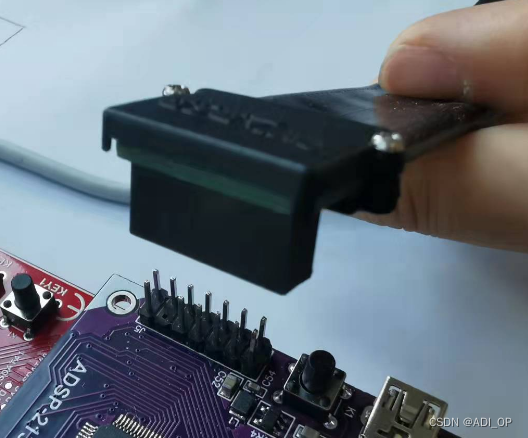

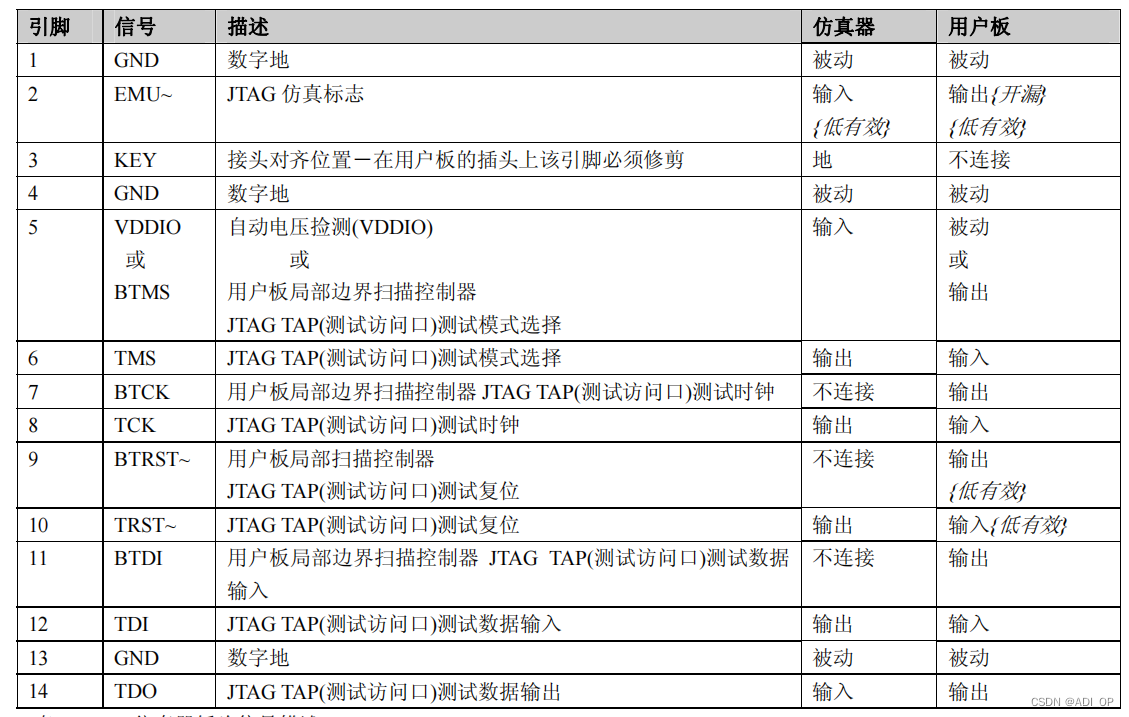

ADI JTAG 仿真器与 DSP 的接口是一个有 14 个引脚的 JTAG 仿真器插头。它与 JTAG 仿真器接头相连。

疑问

新手在做ADI DSP的时候,设计JTAG基本上有一个算一个,都有这种疑问,为什么仿真器堵了一个眼?你的DSP板上的JTAG接口,14个针怎么断了一根?把这两个问题分开来看,不理解,但是你看我把他们合在一起,是不是就看懂了?JTAG接口公口断一根针,仿真器的JTAG接口堵一根针,这其实就是ADI设计的最简单的防反插呀。堵的口和断的针都是无功能性的接口,这样的设计,你想反插都反不了啦。

所以从2000年甚至更早开始,我们用ADI的DSP做JTAG设计,都是14针掰断一根制定好的,仿真器堵一个眼,没别的意思,防反插。

仿真器的接口定义

看到这个黑色的3了吧,这个NO PIN的接口,就是板子上掰断,仿真器堵口的地方了。

仿真器的插头信号描述

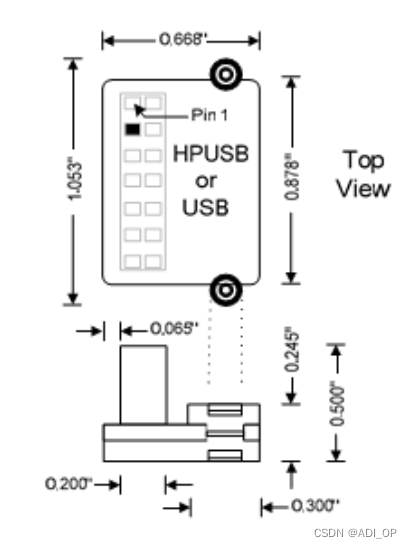

JTAG 仿真器接头机械特性规范

简单的来讲,插针就是2.54间距的。

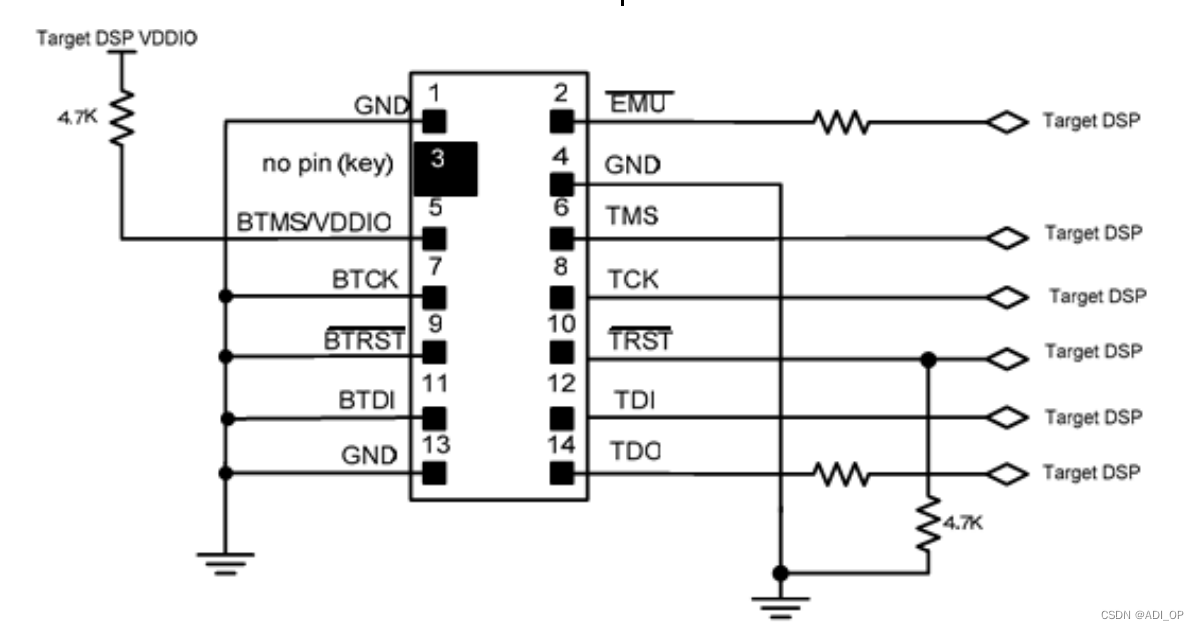

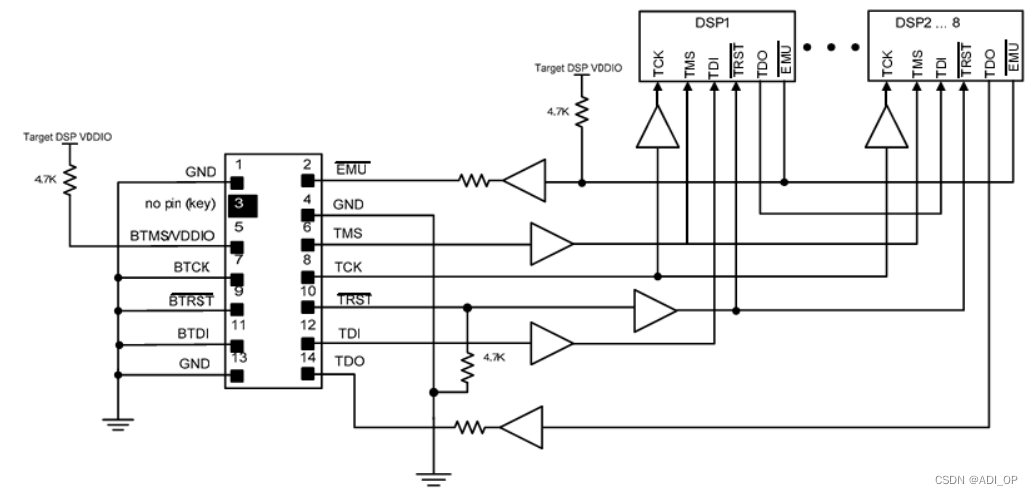

仿真器的关键信号线路

所有的 JTAG 仿真器信号(TCK, TMS, TDI, TDO, EMU~和 TRST~)都作为关键路径信号。在用户板上对这些信号进行布线时要特别注意。控制阻抗指定为 50 欧和 75 欧。采用固化共地使串扰最小。布线时让 JTAG 仿真器的信号远离高频网络,尤其是时钟线。布线越短越好,布线长度尽可能相等。

这些线路不能受到其它信号的干扰,当 TDO 和EMU~的路径非常长时可能需要串联端接电阻器。

JTAG 仿真器接头 I/O 特性

JTAG 仿真器接头可以耐高达 5V 的直流电。这对所有的 Analog Devices JTAG 系列 JTAG I/O 电压为 5V、3.3V、2.5V 和 1.8V 的 DSP 处理器都适用。仿真器接头可以适用于 5V 的用户板,其逻辑电平为 3.3V,这同时也满足了阈值电压不能超过 5V 的要求。

DSP JTAG设计参考原理图-单DSP

DSP JTAG设计参考原理图-多DSP

参考文献

ADI官方提供的JTAG设计文档,文档名为:EE68

ADI JTAG 设计指南

ADI JTAG 设计指南

6255

6255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?