事情是这样的,我们,替换了原来的 microchip 的 ksz8041 ,使用了一颗更便宜的TI phy 芯片 dp83822i , 硬件设备上使用相同的两个 phy , 一个通信正常,LED 显示也正常,另一个通信不正常,LED显示也不正常。硬件工程师查了图,看两颗芯片外围电路是一样的,

那做过嵌入式软件工程师的都知道,驱动一般都是通用的,一般不会区分对待两个phy, 那这就很奇怪了。。。。。

来吧,搞,一探究竟!

先看下我们期望的配置

- RMII 模式 (由参考时钟决定)

- 两个网口,支持10M/100M 半双工/全双工 4种模式,可自动协商。

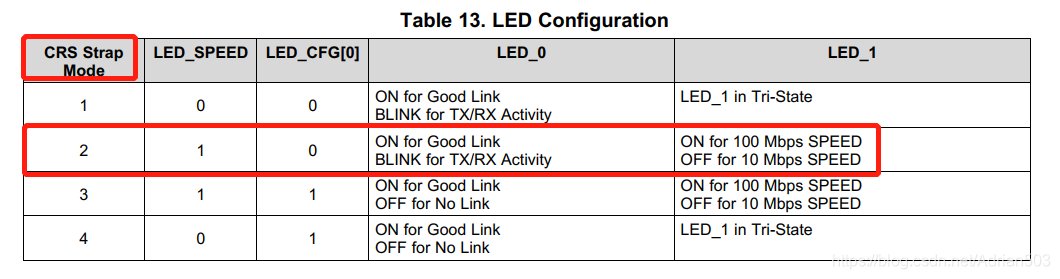

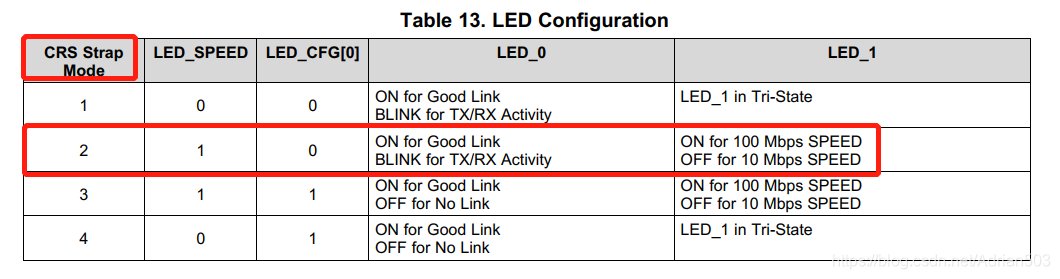

- 两个网口,LED0 ( Link & Actitvity) LED1 ( speed, 100M ON, 10M OFF)

这三种配置,都可以通过stap pin 配置,这样的优势就是,可使用通用的驱动,适用各种不同配置的硬件设备,而不用每一套设备,都去改一版对应的驱动。

当然也可以通过 寄存器配置,不过一般都不建议使用寄存器配置,因为设计模式要求我们驱动要尽可能做成通用的,这样有违我们的初衷。

1 首先明确一下硬件配置

SOC : AM3352 (cpu 带有2个MAC接口)

PHY : DP83822I

接法如下:

RMII1 ------ PHY1

RMII2 ------ PHY2

分析来看,其实在 linux 驱动上要做的工作并不多,只需要将CPU 的两个 EMAC 接口的引脚的复用正确配置,然后配置好DP82822的驱动(linux 内核已经集成)即可。

所以出现两个phy 的不应该有不同的表现。

看了下 内核中的DP82822 驱动 (drivers/net/phy/dp83848.c) 里面可知,里面的初始化操作,并没有配置 LED 和 工作模式的代码,看来这些配置都是硬件来做的,那到底是如何做的呢?

来看看 phy 的数据手册!

2 Dp83822 phy 芯片 strap pin 的接法

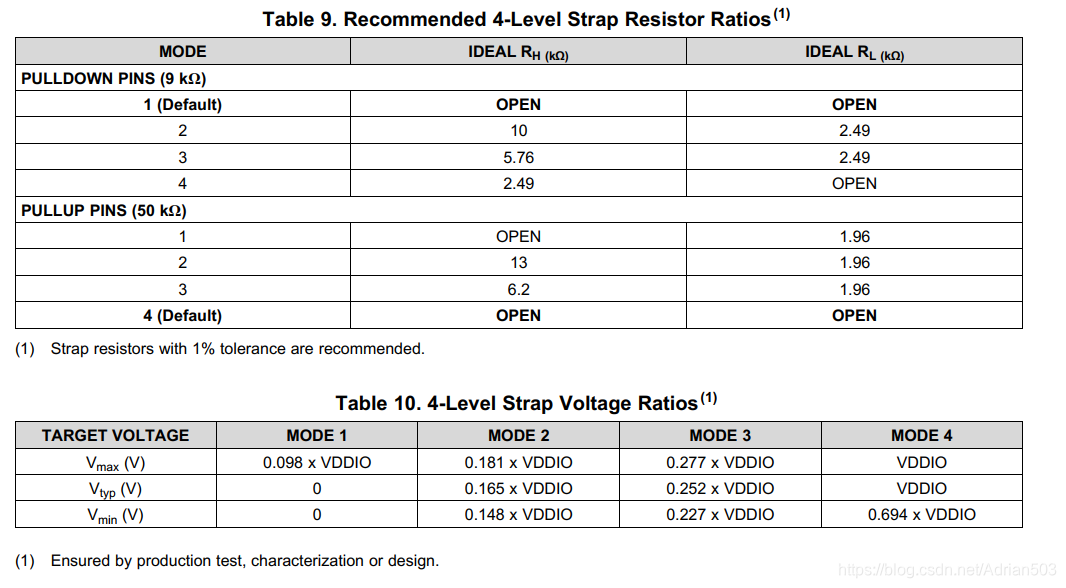

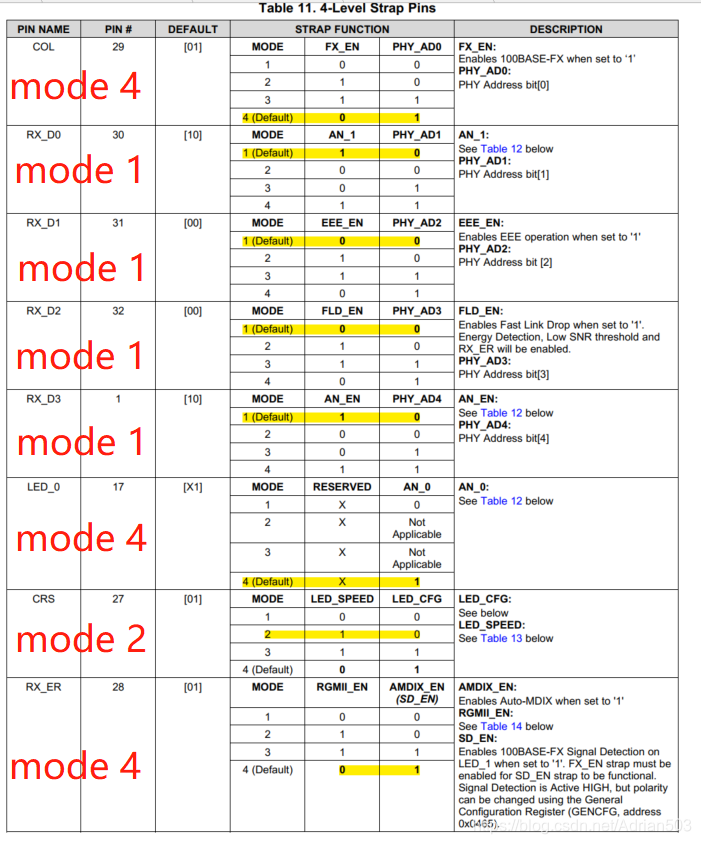

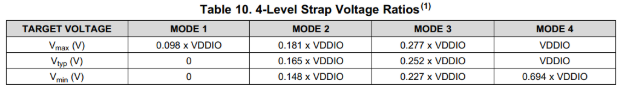

看手册可发现,它的 上拉pin有4种模式,下拉pin 也有4种模式

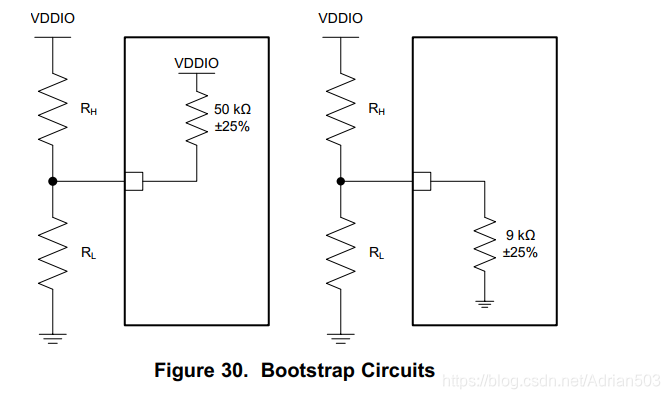

具体的接法如下:

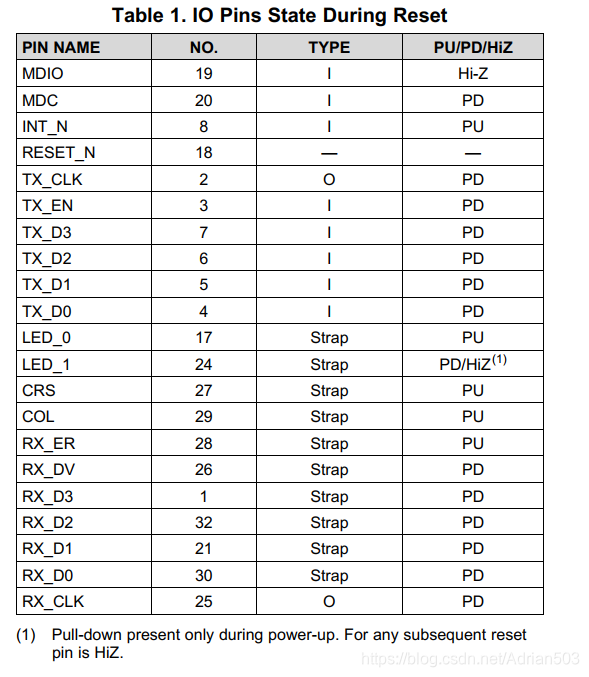

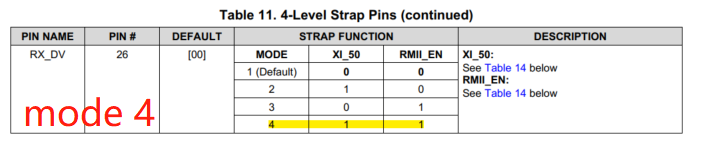

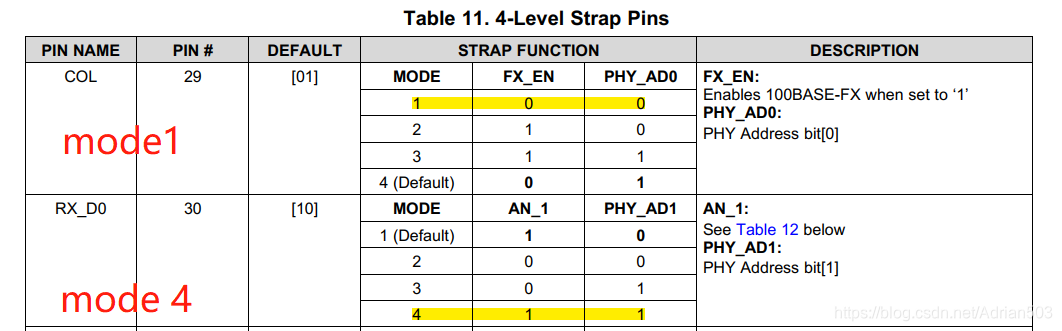

现在我们要做的就是要确认,RMII 模式下的几个 pin 都是上拉,还是下拉,分别都是哪一个mode。

下面的表里说明了哪些 pin 是 Pull up 的 ,哪些是 pull down 的,只需要确定哪个 mode 就可以确定电阻值的大小啦。

注意上面的 OPEN 是指什么都不接。

3 phy 芯片 的 strap pin 配置工作模式、LED模式

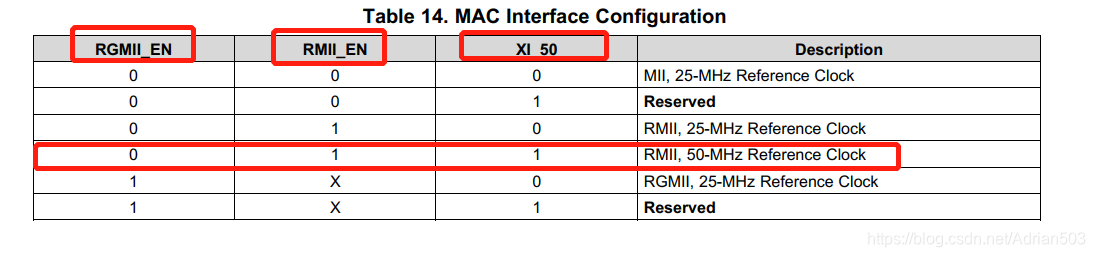

参考时钟决定PHY 工作在 RMII 模式

CRS pin 可配置 LED 模式

需求确定 ---》 工作模式确定 ----》 stap pin 接法确定

注意,从上面的表中我们要用到的值

RGMII_EN = 0

RMII_EN = 1

XI_50 = 1

FX_EN = 0

AN_EN = 1

AN_1 = 1

AN_0 = 1

LED_SPEED = 1

LED_CFG[0] = 0

第1个 phy 地址为 AD4:AD3:AD2:AD1:AD0 00001

第2个 phy 地址为 AD4:AD3:AD2:AD1:AD0 00010

两个phy 由于地址不同,pin strap mode 配置可能会不同,

我们先看第1个phy 的配置 ,根据上面的值,很容易就可以确定下面 pin 的 strap mode

第2个phy 的配置, 只有下面两个不一样。

模式已经确定,把这个新的配置电阻,更新到板子上,测试发现:

两个网口通信均正常了,第一个phy 的LED 显示正常,第二个phy 的LED 还是不对。

通过读 phy1 的 寄存器0x19 发现,phy 的 LED 工作在上图的 mode 2 , 第二个phy 的LED 还是工作在 Mode 3

好吧,继续查,软件工程师又开始和硬件工程师打架了

软件工程师认为是硬件配置的问题,因为从寄存器读出来的模式都是错的,寄存器的值是直接从pin的状态映射来的。

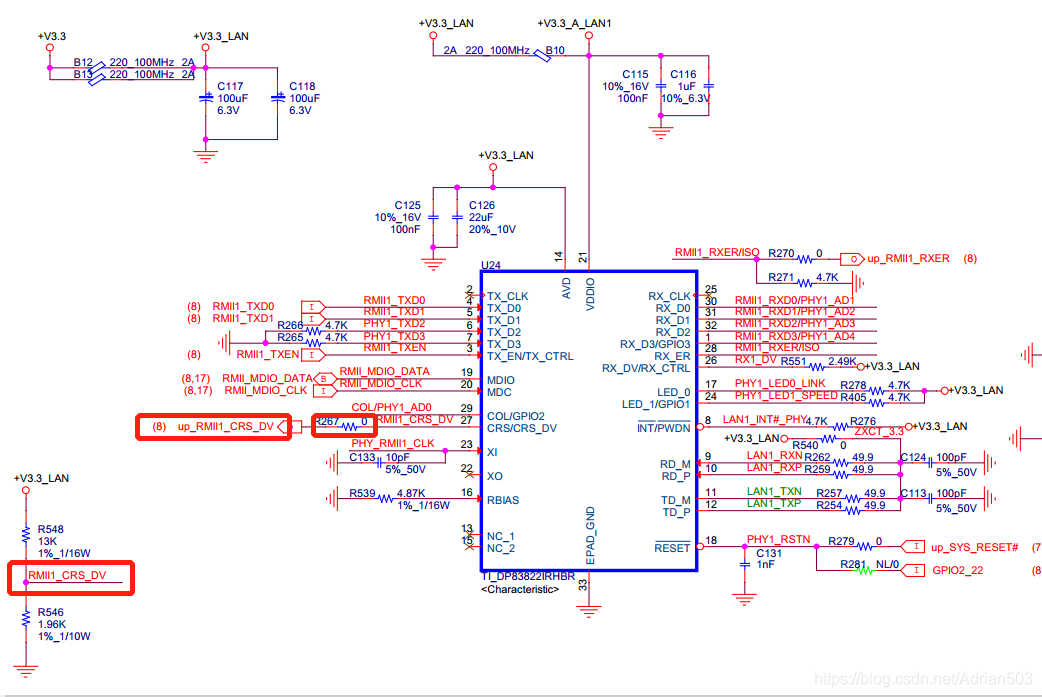

硬件工程师说,CRS这个pin 还接到 PHY1 PHY2 的 strap mode 是一样的,为什么一个正常,一个不正常,这个pin 还连着CPU ,是不是你单独对这个pin 配置了!

好吧,先 量一下 系统上电时候 CRS 的电平状态 ,PHY2的电平值竟然比 PHY1 电平高250mV

断开 R267, 再测一次,两个phy 的CRS 引脚电平值一样了,

我去,,真的是软件哪里不对???

看了下 AM335X 的手册,

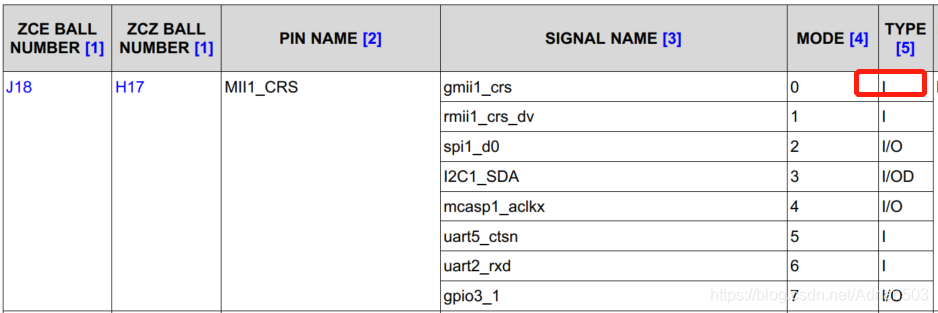

PHY1_CRS <----> GPIO3_1

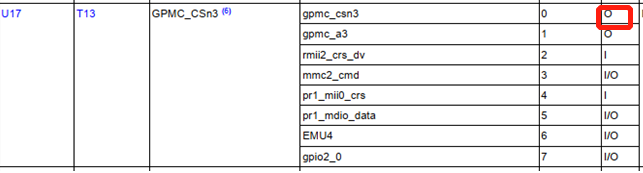

PHY2_CRS <----> GPIO2_0

上电的时候,CPU 的这两个pin 都还没有配置,那就是默认的配置,看了手册,默认配置应该是 复用的 MODE0

从下图可知,PHY1_CRS 上电时,默认状态为 输入状态,不会对 CRS pin 造成影响。

从下图可知,PHY2_CRS 上电时,默认状态为 输出状态,可能会对 CRS pin 造成影响

这个问题是 CPU 对 phy 芯片造成的影响,那这还有解吗 ?

答案当然是有 , 1种是通过修改寄存器来配置 LED mode , 另外一种是调整电阻。当然推荐用第二种啦

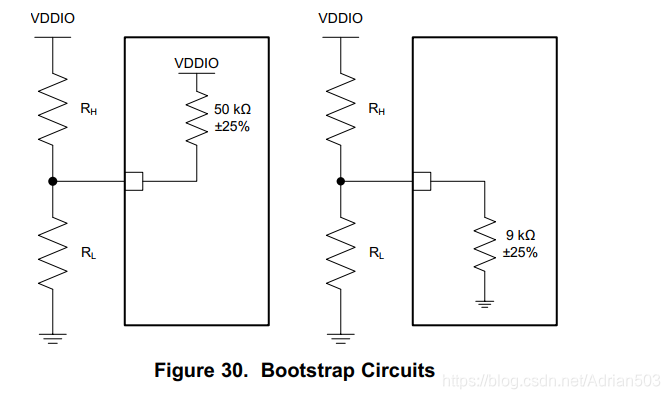

在 第2节的 strap 接法中的几种模式,其实是通过 pin 的电压值来确定的,通过修改电阻当然是可以实现的

现在的电阻值如下:

将R546 改成 小一点的电阻即可,这个可以计算出来的。

修正过后,完美解决!

16万+

16万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?