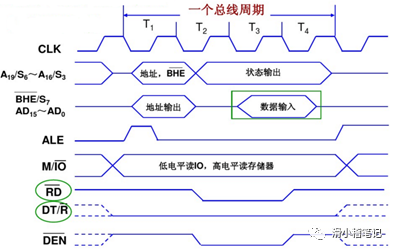

一、 8086的总线周期概念:一个基本的总线周期由4个时钟周期组成,时钟周期是CPU的基本时间计量单位,他由计算机主频决定,时钟周期等于主频的倒数,习惯上将4个时钟周期分别称为4个状态,即T1、T2、T3、(Tw等待状态)、T4状态

1.在T1状态,CPU发出20位物理地址。

2.在T2状态,总线的最高四位A19~A16用来输出本总线周期状态信息,低16位浮置成高阻状态,为传输数据做准备。

3.在T3状态,当CPU需要等待时,可以插入1个或多个等待状态Tw。READY信号线发出准备好信号,为1时状态为T4,为0时状态为Tw。

4.在T4状态,总线周期结束。

在两个总线周期之间执行空闲周期。

二、8086的引脚信号和工作模式

1.最小模式:系统中只有8086一个微处理器。

最大模式:包含两个或多个微处理器,其中一个主处理器是8086,和两个协处理器,分别是,数值运算协处理器8087,输入/输出协处理器8089。

8086工作在最大模式还是最小模式由硬件连线决定。

2.8086的引脚信号和功能

注 1.8086的数据线和地址线是复用的

2.8086有16根数据线(8088有8根数据线)

1.GND地-负极,Vcc电源-正极,

8086用单一的+5V电压。

**2.**地址/数据复用AD0~AD15

在T1状态,AD0引脚传送的地址信号必定为低电平,在其他状态,则用来传送数据。

AD0–低8位–偶地址

3.BHE/S7高8位数据总线允许/状态复用引脚

AD15~AD8上的高8位数据有效

头上有横线指低电平有效,没有指高电平有效。

4.NMI非屏蔽中断引脚,输入

非屏蔽中断不受中断允许标志IF的影响,也不能用软件进行屏蔽,只执行对应中断类型为2的非屏蔽中断处理程序。

5.INTR可屏蔽中断请求信号,输入

高电平有效。CPU在每条指令执行到最后一个时钟周期时会对INTR引脚信号进行采样。若IF=1,CPU则会响应中断,并且有收到INTR信号,则CPU停止当前的操作,响应中断请求,执行一个中断处理子程序。

6.RD读信号,输出;WR写信号,输出

低电平有效

7.M/IO存储器/输入输出控制信号,输出

如为高电平,表示CPU和存储器之间进行数据传输;如为低电平,表示CPU和I/O接口进行数据传输。

8.最大最小工作模式选择端MN/MX:高电平为最小工作模式,低电平为最大工作模式;

9.准备就绪信号READY:高电平有效;

10.CLK时钟

1/3周期为高电平,2/3周期为低电平

11.RESET复位信号

最小模式

1.ALE地址锁存允许信号

在T1状态,高电平有效

2.DT/R数据收发信号

DT/R–高电平–数据发送–WR–写

DT/R–低电平–数据接收–RD–读

BHE+A19A16)+AD15AD0 )=21位地址信息–>3片地址锁存器8282

ALE、DEN、DT/R从CPU直接送出

最大模式

状态信号S2,S1,S0打包以上信号发送给总线控制器8288

8086的操作和时序

复位:8086要求RESET信号起码维持4个时钟周期的高电平,CS置1其他清零

总线读/写操作时序

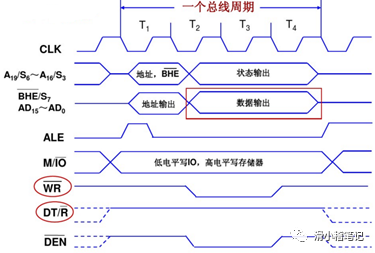

在8086CPU中,一个最基本的总线周期由4个时钟周期组成,即T1,T2,T3,T4一共4个状态,当CPU需要等待时,可以插入1个或多个等待状态Tw。

最小工作模式下的读时序

最小工作模式下的写时序

总线写操作时序与读操作时序基本相似,但是存在几个不同点:

(1)CPU不是输出RD信号,而是输出WR信号;

(2)DT/R整个总线周期都是高电平,表示总线周期为写周期,在接有数据总线收发器的系统中,用来控制数据传输方向;

(3)AD15~AD0在T2到T4状态输出数据,输出地址与输出数据为同一方向,无需像读周期那样要高阻态做缓冲,所以T2状态无高阻态。

部分图文源自网络

375

375

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?