6.4 总线的定时和数据传送模式

6.4.1 总线的定时

总线的信息传送过程:请求总线、总线仲裁、 寻址、信息传送、状态返回

定时:事件出现在总线上的时序关系

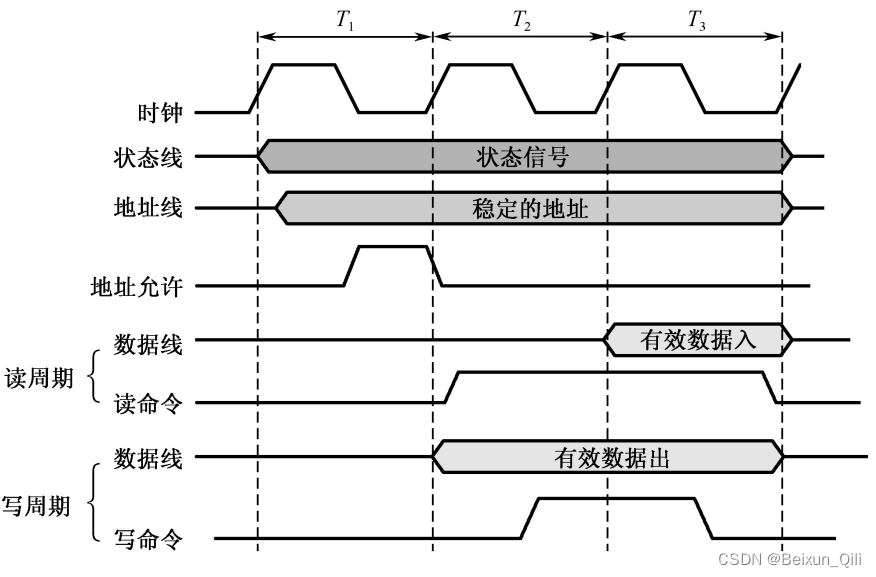

(1)同步定时

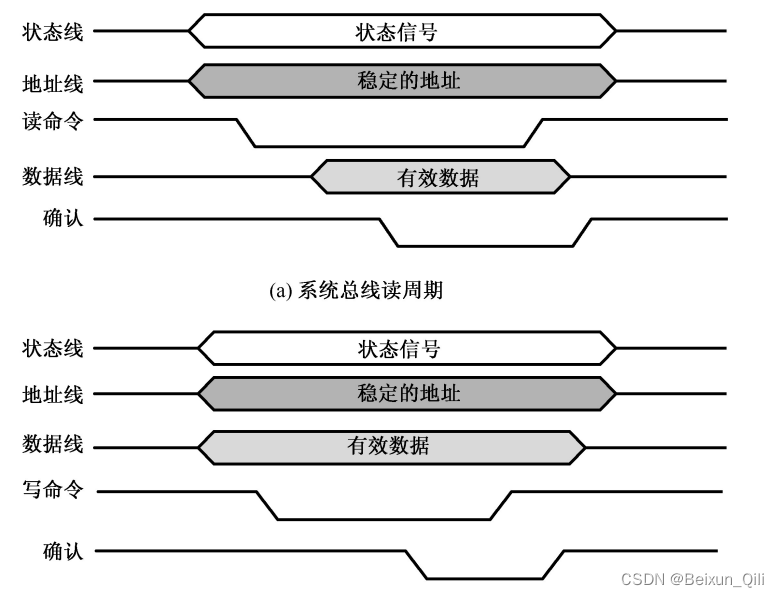

(2)异步定时

6.4.2 总线数据传输模式

(1)读、写操作

读操作是由从方到主方的数据传 送

写操作是由主方到从方的数据传送

一般, 主方先以一个总线周期发出命令和从方地址, 经过一定的延时再开始数据传送总线周期

(2)块传送操作

只需给出块的起始地址,然后对 固定块长度的数据一个接一个地读出或写入

(3)写后读、读修改写操作

这是两种组合操作。 只给出地址一次(表示同一地址),或进行先写后读操作,或进行先读后写操作

(4)广播、广集操作

一般而言,数据传送只在一 个主方和一个从方之间进行

广播:但有的总线允许 一个主方对多个从方进行写操作

广集:将选定的多个从方数据在总线上完成AND或OR操 作,用以检测多个中断源

6.5 PCI总线和PCIe总线

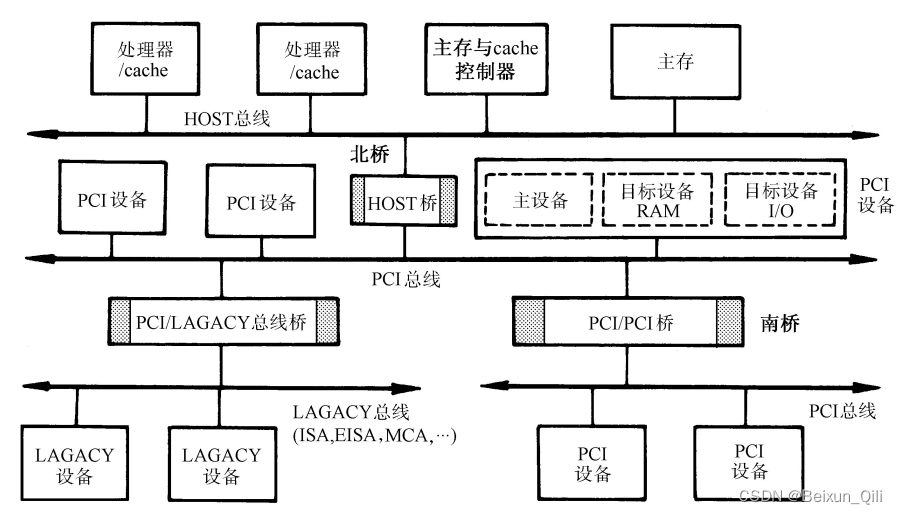

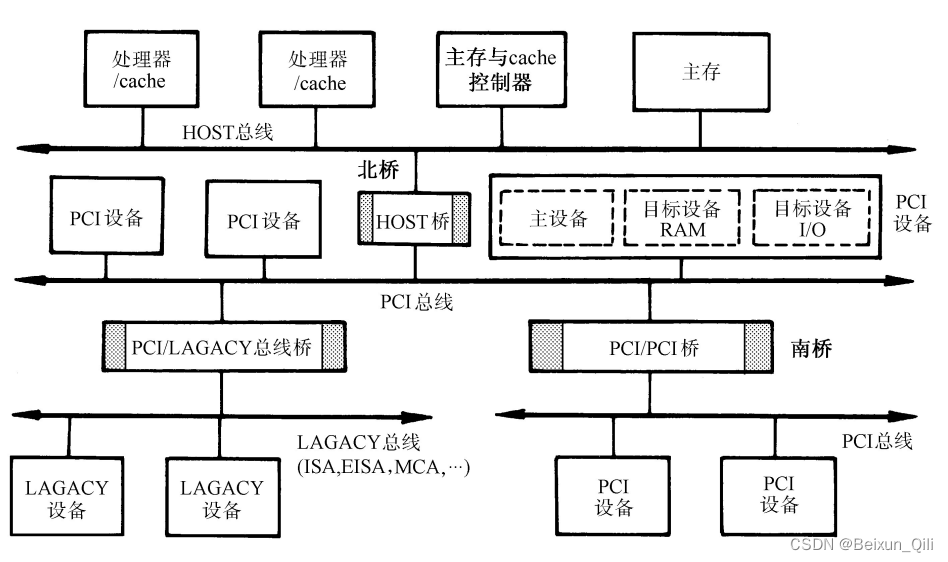

6.5.1 多总线结构

(1)HOST总线(连接“北桥”芯片与CPU之间的信息通路)

该总线有CPU总线、系统总线、主 存总线、前端总线等多种名称,各自反映了总线功能的一个方面。这里称“宿主”总线,也许更全面,因为HOST总线不仅连接主存,还可以连接多个CPU

(2)PCI总线(连接各种高速的PCI设备)

一个与处理器无关的高速外围总线,又是至关重要的层间总线

采用同步时序协议和集中式仲裁策略,并具有自动配置 能力

PCI设备可以是主设备,也可以是从设备,或兼而有之

(3)LAGACY总线

可以是ISA,EISA,MCA等这类性能较低的传统总线,以便充分利用市场丰富的适配器卡, 支持中、低速I/O设备

(4)桥

本身的结构可以十分简单,如只有信号缓冲 能力和信号电平转换逻辑,也可以相当复杂, 如有规程转换、数据快存、装拆数据等

6.5.2 PCI总线信号

PCI总线的基本传输机制是猝发式传送,利用 桥可以实现总线间的猝发式传送

写操作时, 桥把上层总线的写周期先缓存起来,以后的时 间再在下层总线上生成写周期,即延迟写

读 操作时,桥可早于上层总线,直接在下层总线 上进行预读。无论延迟写和预读,桥的作用可 使所有的存取都按CPU的需要出现在总线上

6.5.3 PCI总线周期类型

存储器读/写总线周期

存储器写和使无效周期

特殊周期

配置读/写周期

6.5.4 PCI总线周期操作

特点:

(1)采用同步时序协议。总线时钟周期以上跳沿开始,半个周期高电平,半个周期低电平。总线上所有事件,即信 号电平转换出现在时钟信号的下跳沿时刻,而对信号的采 样出现在时钟信号的上跳沿时刻

(2)总线周期由被授权的主方启动,以帧FRAME#信号变 为有效来指示一个总线周期的开始

(3)一个总线周期由一个地址期和一个或多个数据期组成。 在地址期内除给出目标地址外,还在C/BE#线上给出总线 命令以指明总线周期类型

(4)地址期为一个总线时钟周期,一个数据期在没有等待 状态下也是一个时钟周期。一次数据传送是在挂钩信号 IRDY#和TRDY#都有效情况下完成,任一信号无效(在时 钟上跳沿被对方采样到),都将加入等待状态

(5)总线周期长度由主方确定。在总线周期期间FRAME# 持续有效,但在最后一个数据期开始前撤除。即以 FRAME#无效后,IRDY#也变为无效的时刻表明一个总线 周期结束。由此可见,PCI的数据传送以猝发式传送为基 本机制,单一数据传送反而成为猝发式传送的一个特例。 并且PCI具有无限制的猝发能力,猝发长度由主方确定, 没有对猝发长度加以固定限制

(6)主方启动一个总线周期时要求目标方确认。即在 FRAME#变为有效和目标地址送上AD线后,目标方在延 迟一个时钟周期后必须以DEVSEL#信号有效予以响应。 否则,主设备中止总线周期

(7)主方结束一个总线周期时不要求目标方确认。目标方 采样到FRAME#信号已变为无效时,即知道下一数据传送 是最后一个数据期。目标方传输速度跟不上主方速度,可 用TRDY#无效通知主方加入等待状态时钟周期。当目标 方出现故障不能进行传输时,以STOP#信号有效通知主 方中止总线周期

6.5.5 PCI总线仲裁

PCI总线采用集中式仲裁方式,每个PCI主设 备都有独立的REQ#(总线请求)和GNT# (总线授权)两条信号线与中央仲裁器相连

由中央仲裁器根据一定的算法对各主设备的申 请进行仲裁,决定把总线使用权授予谁。但 PCI标准并没有规定仲裁算法

6.5.6 PCIe总线

PCIe总线全称为PCI-Express,是基于PCI总线技 术发展起来的总线标准

对PCI总线有良好的继承性,在软件应用上兼容 PCI总线

PCIe总线的主要改进有如下几点:

1、高速差分传输

2、串行传输

3、全双工端到端连接

4、基于多通道的数据传输方式

5、基于数据包的传输

本文详细介绍了总线定时的同步和异步概念,以及PCI和PCIe总线的数据传输模式,包括读写操作、块传送、组合操作和广播广集。此外,着重剖析了PCI总线的信号、周期操作、仲裁机制,以及PCIe在PCI基础上的改进。

本文详细介绍了总线定时的同步和异步概念,以及PCI和PCIe总线的数据传输模式,包括读写操作、块传送、组合操作和广播广集。此外,着重剖析了PCI总线的信号、周期操作、仲裁机制,以及PCIe在PCI基础上的改进。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?