时序图是所有硬件设计工程师不得不关心的东西,这个是我在做CY7C68013与FPGA模块连接时遇到的,以此为例介绍一下此时序图的读写技巧和编程技巧。

首先看Slave fifo的写时序(图片来自CY7C68013的官方datasheet)

1、首先看时序图左侧的4个I/O(IFCLK,SLWT,DATA,FLAG)这是我们想操作slave fifo必须要用的,也是我们主要关心的东西。

2、然后明确我们的目的是向fifo写入数据,也就是写入DATA,从图9-7中可以看出DATA是在上升沿时写入的,同时DATA的写入是有要求的:必须在距离上升沿至少时间之前输入并且在上升沿之后保持

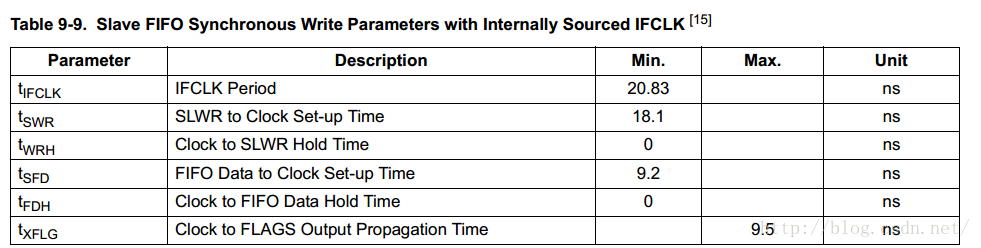

的时间。从表格9-9中可知

至少为9.2ns,

为0。

3、然后继续看图中的SLWR,由前面的datasheet我们已经知道SLWR是FIFO的写信号,用于控制FIFO写入的。同上一样,我们也看到了SLWR两个重要的的时间和

,时间分别是18.1和0。

4、继续看FLAGS,FLAGS由datasheet知是slave fifo空满的标志位。通过图中看出,标志位实在数据上升沿输入后的时间后才输出的。因此程序中我们要检测FLAGS状态时必须在此时间之后才能检测到。这一点是很重要的,否则可能会导致数据溢出。

5、最后是IFCLK了,对于IFCLK datasheet个出的说明是 “Interface Clock, used for synchronously clocking data into or out of the slave FIFOs. IFCLK also serves as a timing reference for all slave FIFO control signals and GPIF. When internal clocking,IFCONFIG.7 = 1, is used the IFCLK pin can be configured to output 30/48 MHz by bits IFCONFIG.5 and IFCONFIG.6. IFCLK may be inverted, whether internally or externally sourced, by setting the bit IFCONFIG.4 =1.”。简单说就是IFCLK是控制数据输入输出的时钟,并且其频率有两个选择:内部时钟30MHZ/48MHZ 或者使用外部时钟 。 我先是用外部时钟(FPGA输出时钟)编的,后来在应用中发现并不方便,因此有换成了内部时钟控制,两种方法都很简单。附的程序为内部时钟48Mhz控制的。

然后就要上程序了:(这里只是控制时序部分的程序)

always@(negedge IFCLK or negedge rst_n) //为了配合时序,此处采用下降沿的时候操作if(!rst_n)

begin

SLWR <= 1; //不允许向FX2LP写入,注意SLWR标志位是“0”有效

data_out <= 16'h00;

end

else if(flagb && start_ad) //如果FIFO非满并且AD采集开关已经打开

begin

SLWR <= 0;

data_out <= data;

end

else

begin

SLWR <= 1;//不允许向FX2LP写入

end

endmodule

还有读fifo部分的时序分析,由于时间问题,以后有时间在写。

第一次写博客,如果有什么纰漏或者错误的话,欢迎大侠批评指正。

129

129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?