VGA协议与图像输出Verilog编程

本次实验,我将完成以下目标:

- 从"实验3-基于Verilog HDL的数字秒表、波形发生器等设计" 任选一个完成;

- 练习基于VGA的图像显示,了解VGA协议,通过Verilog编程实现VGA端口生成彩条图案或者自定义的汉字图案;或者完成一个简单的类似贪吃蛇的VGA小游戏

1 数字秒表

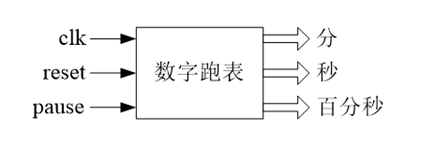

要求用Verilog HDL设计一个数字跑表,所需引脚和功能如下所示:

话不多说,首先点开quartus,创建新的工程

芯片选择如下:EP4CE115F29C7

点击New ->Verilog HDL File 创建新的Verilog文件,然后复制入如下代码

module Verilog1(clk,reset,pause,msh,msl,sh,sl,minh,minl);

input clk,reset,pause;

output [3:0] msh,msl,sh,sl,minh,minl;

reg [3:0] msh,msl,sh,sl,minh,minl;

reg count1,count2;

always @(posedge clk or posedge reset)

begin

if(reset)

begin

{

msh,msl}<=0;

count1<=0;

end

else if(!pause)

begin

if(msl==9)

begin

msl<=0;

if(msh==9)

begin

msh<=0;

count1<=1;

end

else

msh<=msh+1;

end

else

begin

msl<=msl+1;

count1<=0;

end

end

end

always@(posedge count1 or posedge reset)

begin

if(reset)

begin

{

sh,sl}<=0;

count2<=0;

end

else if(sl==9)

begin

sl<=0;

if(sh==5)

begin

sh<=0;

count2<=1;

end

else

sh<=sh+1;

end

else

begin

sl<=sl+1;

count2<=0;

end

end

always @(posedge count2 or posedge reset)

begin

if(reset)

begin

minh<=0;

minl<=0;

end

else if(minl==9)

begin

minl<=0;

if(minh==5)

minh<=0;

else

minh<=minh+1;

end

else

minl<=minl+1;

end

endmodule

编译了一下,注:文件名要保持相同(比如博主的Verilog1),不然编译会出错

将文件置顶

点击Tools→Netlist Viewers→RTL Viewer,可以看到刚才创建的电路图

点击File–>New–>University Program VWF

依次点击

将刚才创建的引脚都加入进去

给它整个时钟信号

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8362

8362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?