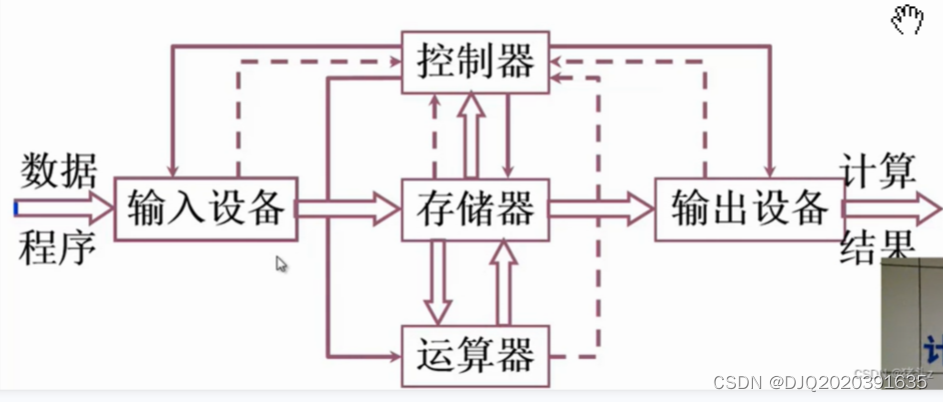

一、计算机的组成

1.输入设备:将数据与程序转换成计算机能够识别,存储,运算的形式,输送到计算机中。

2.输出设备:将计算机对程序和数据的运算结果输送到计算机外部设备

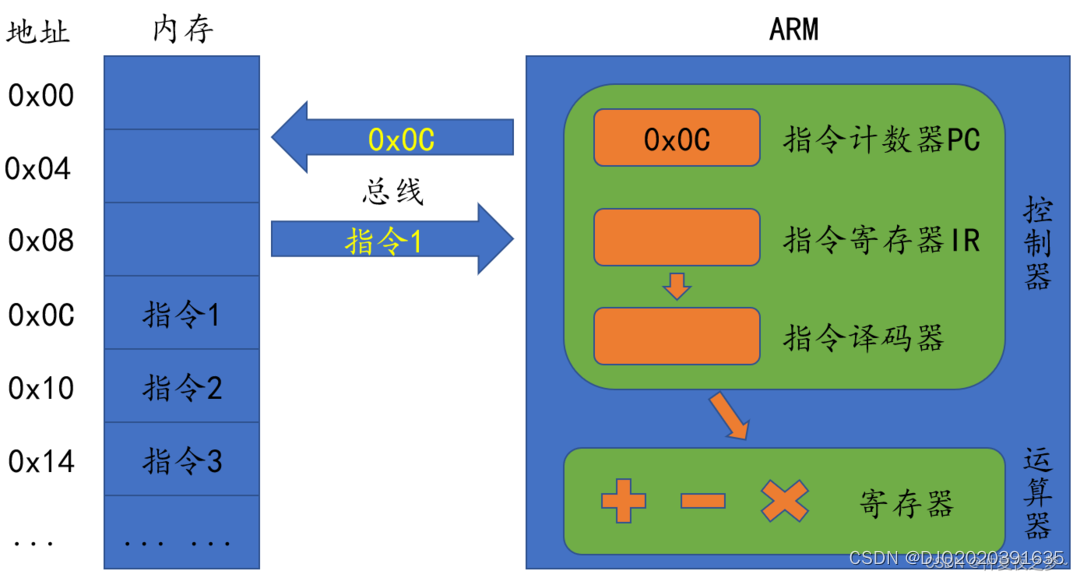

3.控制器:由程序技术器,指令计数器,指令译码器,时许产生器和操作控制器组成。完成计算机指挥工作

4.运算器:由算数逻辑单元(ALU),累计寄存器,数据缓冲寄存器,和状态条件寄存器组成,是数据加工处理部件,完成各种算数与逻辑运算

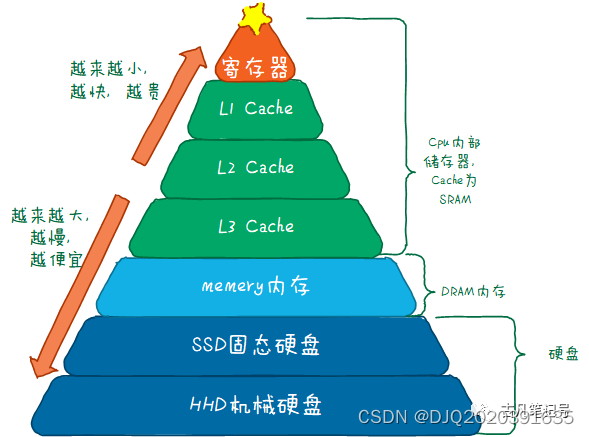

5.存储器:用于保存计算机相关数据模块,根据功能分为内存(主存储器),外存(辅组存储器),寄存器,高速缓冲。

1)寄存器:存在CPU内部,用于暂时存放数据,CPU对此范围没有延时

2)告诉缓冲:硬件管理,主存被分为高速缓冲行,存放在CPU内部或非常接近高速缓冲中。当高速缓存需要存储一个字时,高速缓存检查所需要的高速缓存行是否在高速缓冲中,如是,则称为高速缓存命中,满足缓冲要求,就不需要通过总线把范访问请求送入主存,如不是,则必须访问主存。

3)主存(内存):随机存储器(RAM),断电会丢失数据,制度存储器(ROM),断电数据不丢失,不可修改,启动加载模块是存放其中。电可擦可编程ROM(EEPROM),断电不丢失,闪存(flash),断电不丢失,易失性(CMOS),存放当前时间和日期,没有电也能更新,还可以配置参数,如启动那个磁盘。

4)磁盘(外存):磁盘便宜,空间大,但是随机访问数据时间慢,是一种机械装置。

二、指令与指令集

1.机器指令:机器指令又叫机器码,在运算器内部存在各种运算电路,当处理器从内存中获取一条机器指令,就可以按照指令让运算器内部的指定的运算电路进行运算

2.汇编指令:由于机器指令对人类不友好(记不住),当我们和计算机进行交互时不能直接通过机器指令来进行,这个时候汇编就出现了,每一条汇编指令都可以理解为一条机器指令的标识,当我们编写一条汇编指令时,相当于得到了一条机器指令,就可以让运算器进行对应的运算

3.指令集:指令集就是指令的集合,当设计一个处理器的内核时,需提前设计内核中应该有的运算器的运算电路种类和数量,每个运算电路都对应一条指令。所以,设计内核之前应该将每一条运算电路对应的指令设计出来,组成一个指令集,用于作为内核设计的框架。

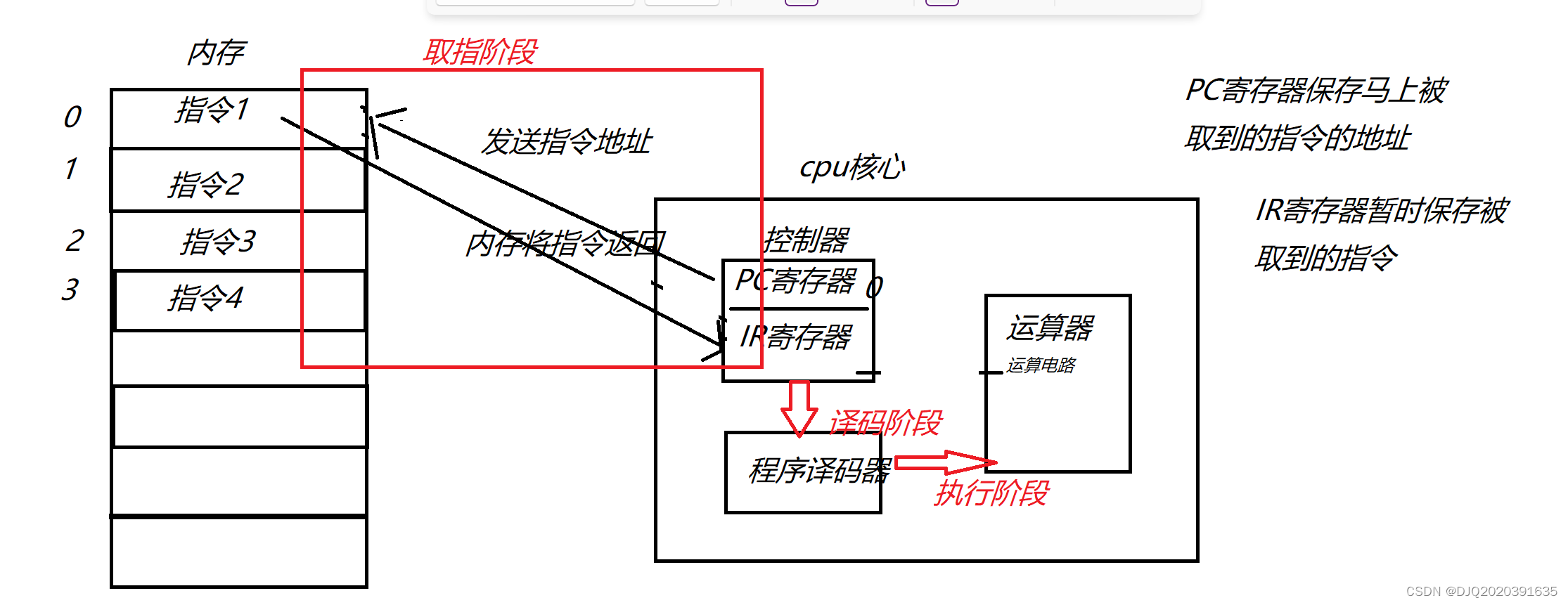

4.一条指令执行过程:

1)取指阶段:控制器将需要执行的指令地址发送给内存,内存将hzi'l返回给控制器

2)译码阶段:取到指令后进行译码操作,分析当前指令的意义,通知运算器进行对应运算

3)执行阶段:指令译码完毕后,运算器进行对应的运算操作,将运算的结果进行保存

地址总线:用于传输地址的媒介

地址总线:用于传输地址的媒介

32位地址总线:32根传输地址的线,寻址范围:0-2^32-1

三、程序编译的基本原理

1.程序编译步骤:

1)预处理:将程序中以#开头的内容展开到当前文件中

2)编译:检查语法的错误,将程序生成汇编

3)汇编:编译汇编文件,生成二进制文件

4)链接:链接程序中使用各种库,生成可执行的二进制文件

2.编译的原理:不同框架的机器识别的机器指令不一样,机器指令与汇编指令不可移植。但是C语言是可移植的,如让c语言程序在不同框架的机器上运行,需要使用不同的编译器,去编译生成不同框架可执行的文件。

四、精简指令集与复杂指令集

指令集用于设计处理器内核框架,不同指令集可以用于设计不同的处理器内核

1.复杂指令集(CISC):指令长度与周期不固定,在处理能力上有优势,一般相对功耗,体积,成本更高,更侧重于硬件执行指令的功能性,它的硬件结构更为复杂。

2.精简指令集(RISC):结构简单,选取了使用频率高的简单指令,指令长度固定,大小固定,多为单周期指令,在功耗,体积,价格方面多有优势,多用于嵌入式领域。

指令长度:一条指令占用存储空间的大小

指令周期:执行一条指令的时间

3.常见的精简指令集框架:

3.常见的精简指令集框架:

ARM架构:当前主流的精简指令集框架,需要ARM公司授权使用

RISC-V架构:开源,正迅速发展的精简指令集架构

MIPS:中国龙芯收购,在原有的架构基础上进行优化

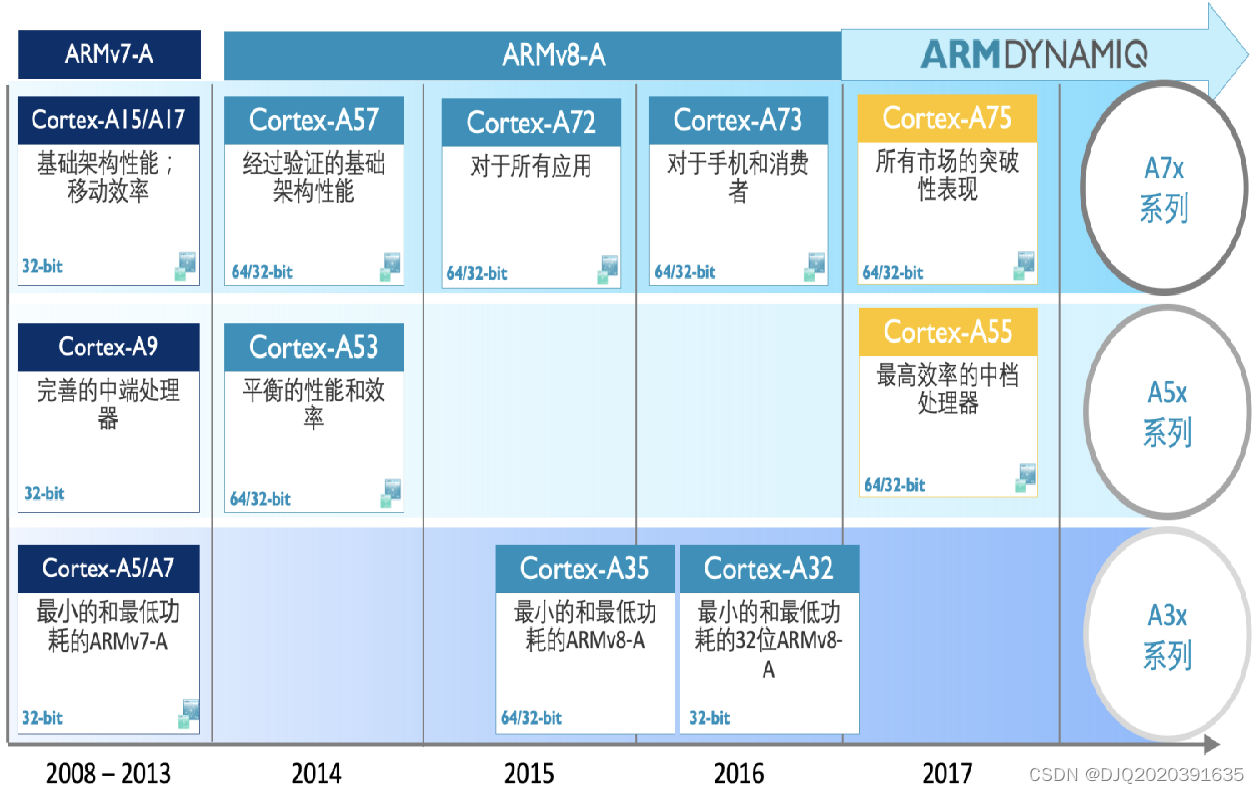

五、ARM

1.ARM架构:ARM推出的用于设计不同处理器核心的框架,本质上是不同的ARM指令集

32位的处理器是指一条机器指令能够最大能够运算32位数据

32位指令集每条指令的长度是32位

2.ARM内核:不同的ARM处理器核心,它基于ARM架构设计

3.SOC:片上系统,若干个内核组成了一个处理器,在处理器外部集成各个外设(GPIO/UART/DMA/IIC/SPI),通过总线完成连接,组成一个微型计算机系统

六、ARM产品分布

1.Cortex-A系列:内核更加注重功能性的完善,继承以往ARM的内核,属于ARM高端产品,一般用于手机,电脑,pad。

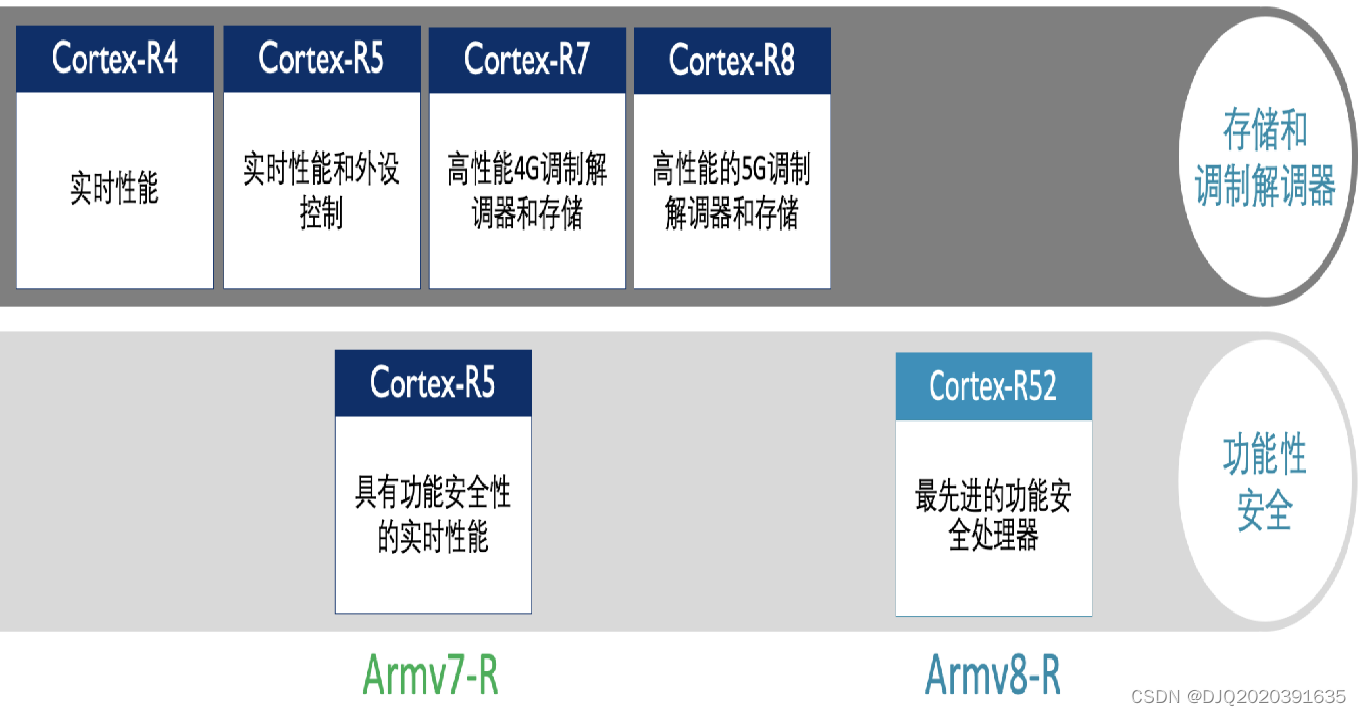

2.Cortex-R系列:用在实时性要求比较高的场景,如智能汽车,军工,医疗

2.Cortex-R系列:用在实时性要求比较高的场景,如智能汽车,军工,医疗

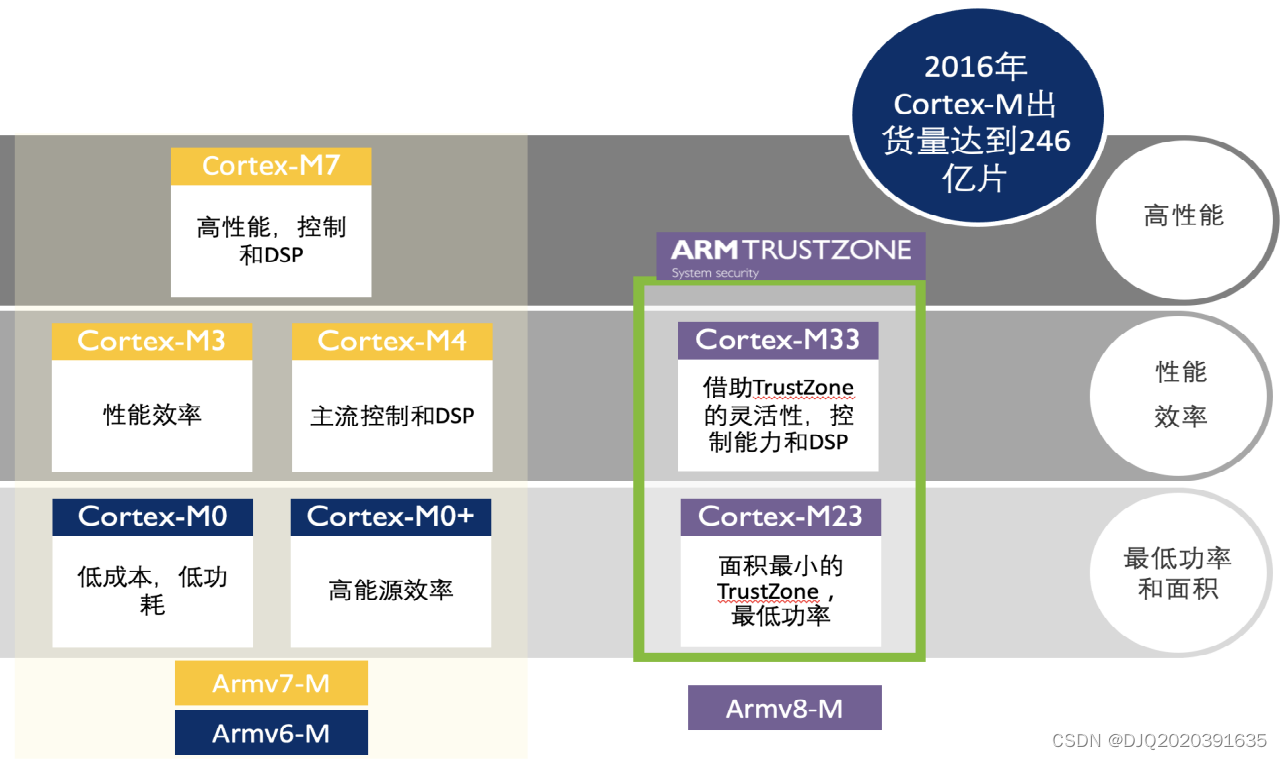

3.Cortex-M系列:属于RAM的低端产品,主要进行一些智能控制工作

3.Cortex-M系列:属于RAM的低端产品,主要进行一些智能控制工作

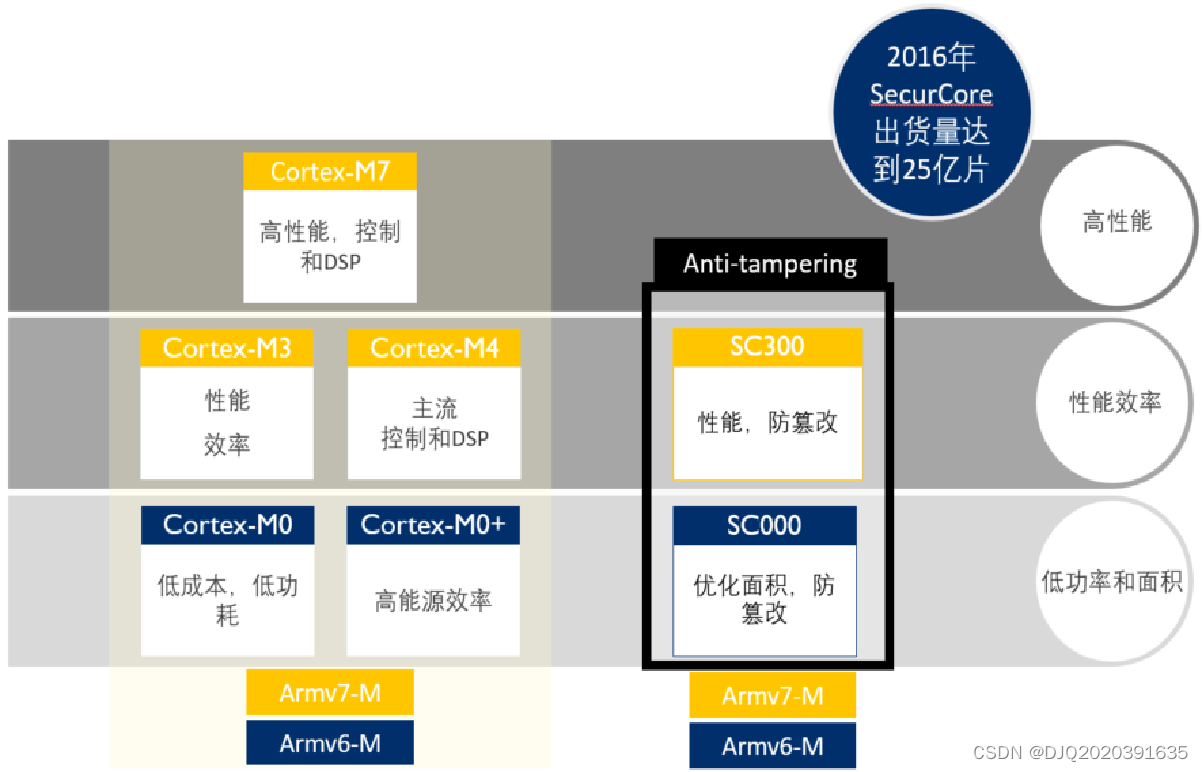

4.SecurCore系列:用于对安全性能要求比较高的场景

4.SecurCore系列:用于对安全性能要求比较高的场景

5.Cortex-X系列:在2016年推出的一种内核系列,在云计算,边缘计算性能比较优越

5.Cortex-X系列:在2016年推出的一种内核系列,在云计算,边缘计算性能比较优越

6.ARM的数据约定:

A7采用的是32位框架:

约定:

Byte 8 bits

Halfword 16 bits

Word 32 bits

Doubleword 64 bits

大部分ARM core 提供:

ARM 指令集(32 bit)

THumb指令集(16 bit)

7.ARM工作模式

在ARM处理器面对不同的工作场景时会进入不同的工作模式去执行

User:非特权模式,大部分任务执行在这种模式

FIQ:当一个高优先级(fast)中断产生时,会进入这种模式

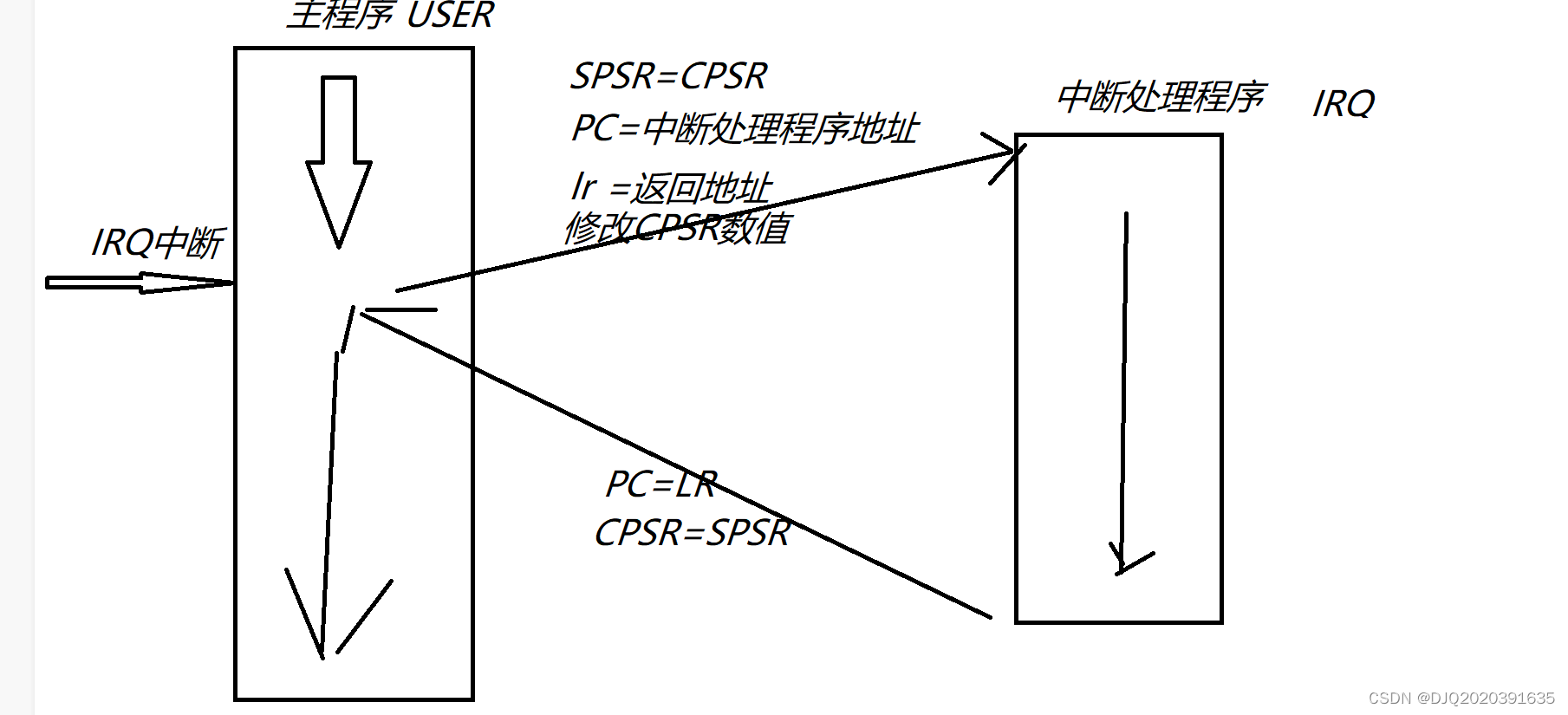

IRQ:当一个低优先级(normal)中断产生时,会进入这种模式

Supervisor:当复位或软中断指令执行时时会进入该种模式

Abort:当存取异常时,会进入该模式

Undef:当执行未定义的指令时,会进入该模式

System:使用和User模式相同寄存器集的特权模式

Cortex-A特有的模式:

monitor模式:执行安全监控代码时进入的模式

HYP模式:虚拟支持模式

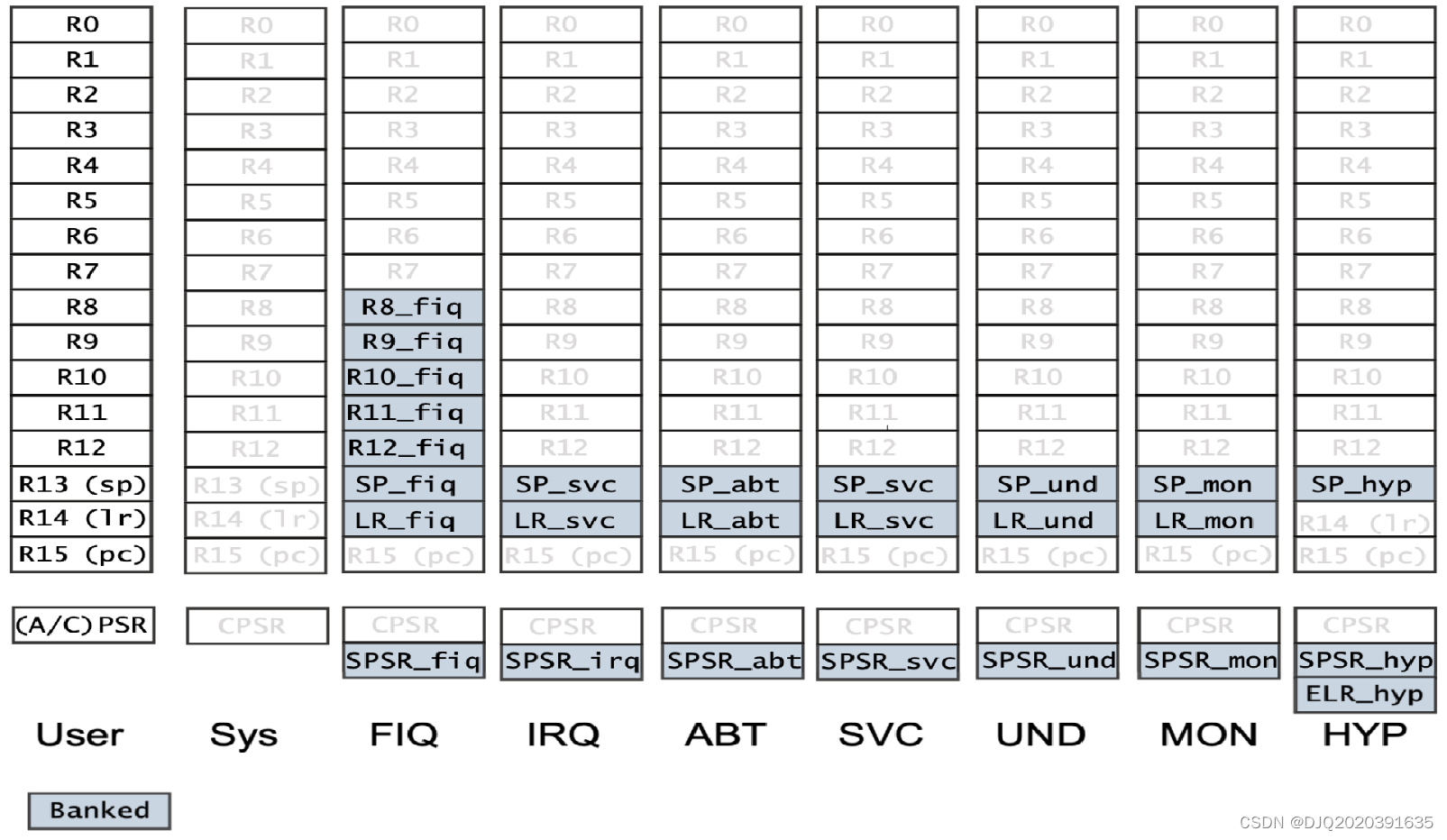

8.ARM V7架构寄存器组织 ARM有37个32bits的长寄存器(1个PC,1个CPSP,5个SPSR,30个通用寄存器)

ARM有37个32bits的长寄存器(1个PC,1个CPSP,5个SPSR,30个通用寄存器)

Cortex体系结构下有43个32bits长的寄存器

当前处理器的模式决定了哪些寄存器可操作,在任何模式下都可以存取

特权模式(除System模式)可以存取

9.ARMv7架构下的一些特殊寄存器

1).R15寄存器(PC):又称为程序计数器,PC寄存器保存即将被从内存中取出来的指令地址,当保存的指令地址被处理器发送给内存之后,PC值会自动向下加一条指令大小,这便是程序继续向下顺序执行断电原因

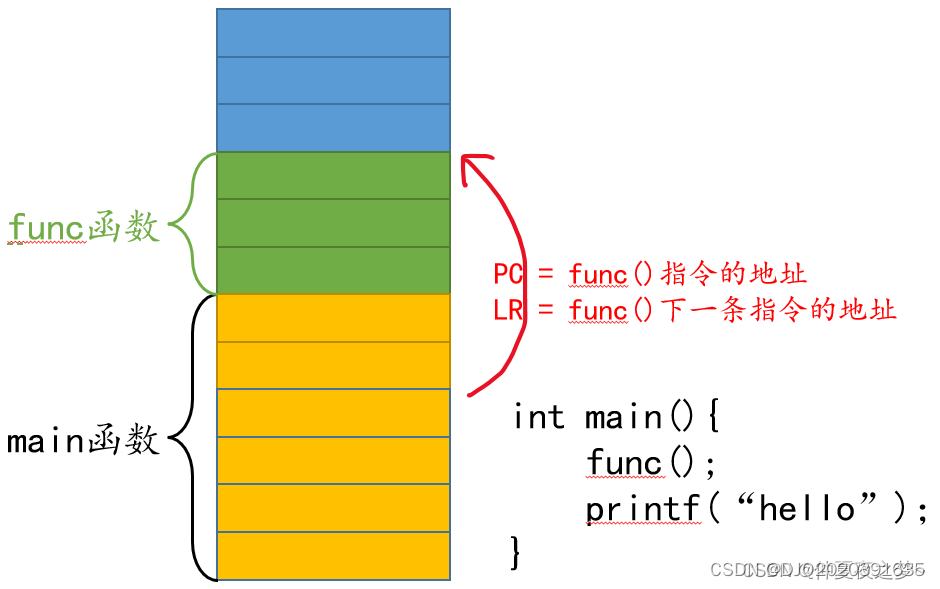

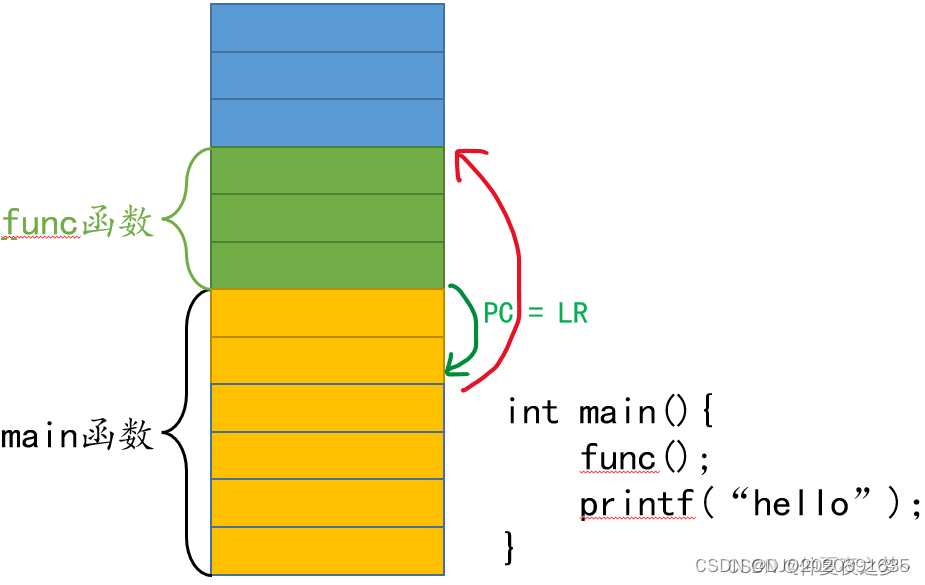

实现程序跳转的本质就是修改PC值

2).R14寄存器(LR):链接寄存器,当执行指令进行程序跳转,LR会保存跳转指令下一条指令的地址,为了程序返回

3).R13寄存器(SP):栈指针寄存器,保存栈内存栈顶地址,对临时数据进行压栈出栈时,需要操作SP的值来找到栈区位置。

3).R13寄存器(SP):栈指针寄存器,保存栈内存栈顶地址,对临时数据进行压栈出栈时,需要操作SP的值来找到栈区位置。

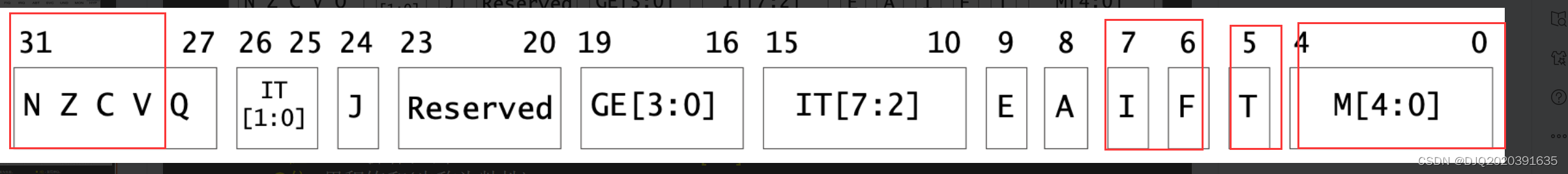

4).当前程序状态寄存器(CPSR):保存当前程序工作状态(工作模式,中断禁止位,程序运算结果条件位)

5).被保存的程序状态寄存器(SPSR):因各种异常切换到异常工作模式时,会将CPSR的值提前保存到SPSR中,处理器处理完异常后,会将SPSR的值赋值给CPSR,用于恢复处理器的工作状态

N[31]:指令运算的结果为负数时,N位被自动置1,否则为0

Z[30]:指令运算的结果为零时,Z位被自动置1,否则为0

C[29]:加法运算产生进位,C位被自动置1,否则为0,减法运算产生借位,C位被自动置0,否则为1

V[28]:符号位发生变化,V位自动置1,否则为0

I[7]:IRQ中断屏蔽位,I=0,不屏蔽IRQ中断,I=1,屏蔽IRQ中断

F[6]:FIQ中断屏蔽位,F=0,不屏蔽FIQ中断,F=1,屏蔽FIQ中断

T[5]:状态位,T=0,表示ARM状态,执行ARM指令集,T=1,Thumb状态,执行Thumb指令集

ARM指令集:一条汇编指令编译生成32位机器码

Thumb指令集:一条汇编指令编译生成16位机器码

ARM的指令集代码密度低,Thumb指令集代码密度高,ARM指令集功能性高于Thumb指令集

M[4:0]:模式位

10000:User mode

10001:FIQ mode

10010:IRQ mode

10011:SVC mode

10111:Abort mode

11011:Undef mode

11111:System mode

10110:monitor mode

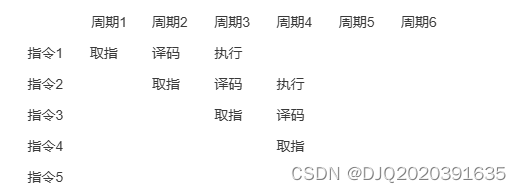

10.ARM处理器的流水线工作

一条指令的执行过程分为取指,译码,执行三阶段,为了充分利用处理器资源,提高指令执效率,引入ARM三级流水线工作

1221

1221

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?