一、半导体存储电路概述

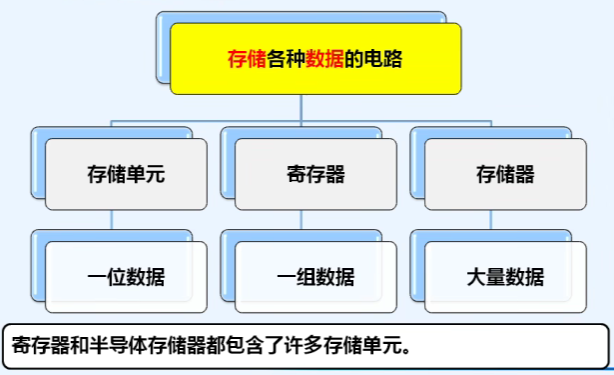

1.存储电路及其分类

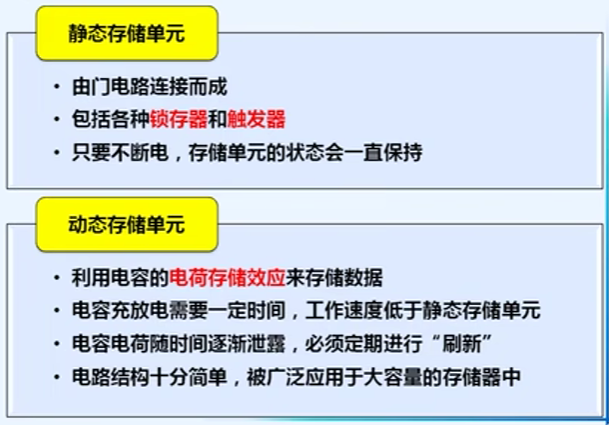

2.存储单元的分类

对电容的电荷存储效应存储数据的理解:比如一个电容一端接地,另一端作为输出,当电容不充电时,电容两端没有压差,对应的输出为低电平,如果电容充满了电,此时电容器两端有压差,对应的输出为高电平,可以通过对电容器的充电和放电来实现数据0和1的存储。

此外,还有一个问题:电容器充满电之后会有一定的漏电流,即电容器在存储完数据之后,会开始逐渐漏电,两端的电压会逐渐降低,因此必须每隔一段时间给电容器重新充一次电,否则数据会丢失,我们将这个过程称之为“刷新”,相当于是重新刷新一遍存放的数据,保证数据不会丢失。

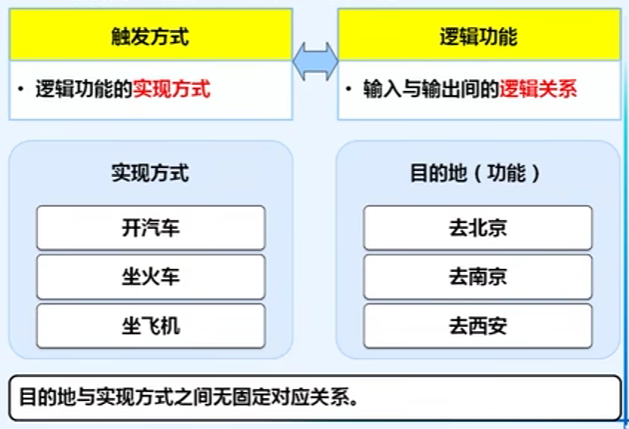

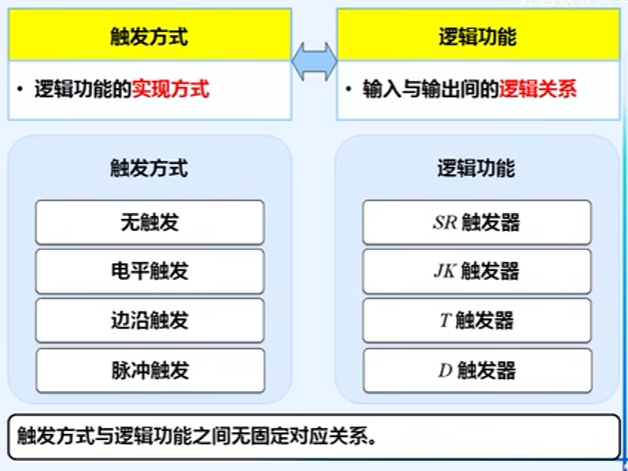

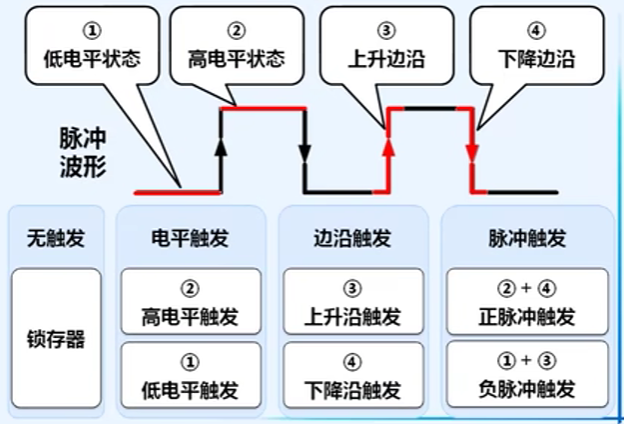

3.存储单元的触发方式与逻辑功能

逻辑功能:该电路能够实现什么样的功能。

触发方式:存储单元实现逻辑功能采用的方法。

4.存储单元按触发方式分类

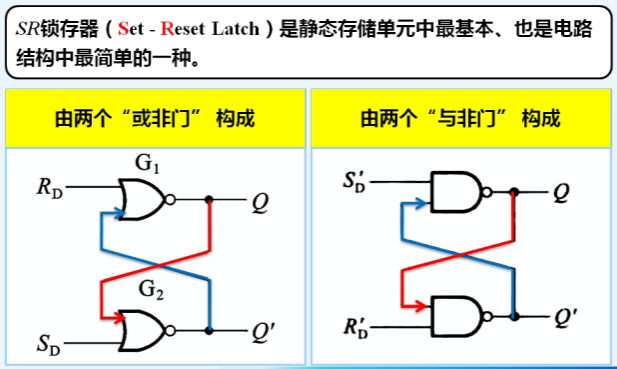

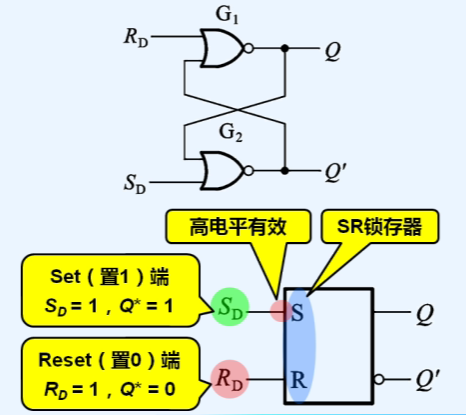

二、由两个“或非门”构成的SR锁存器

1.SR锁存器的电路结构

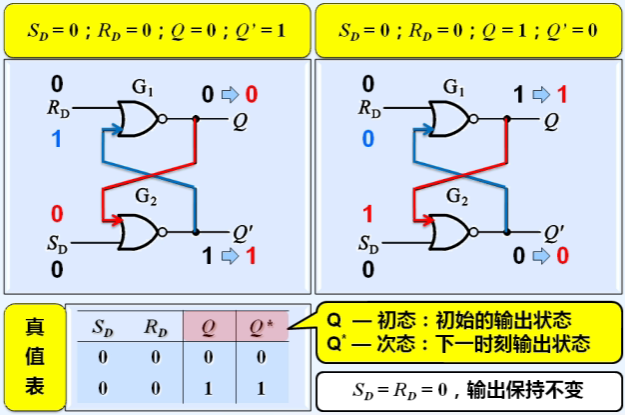

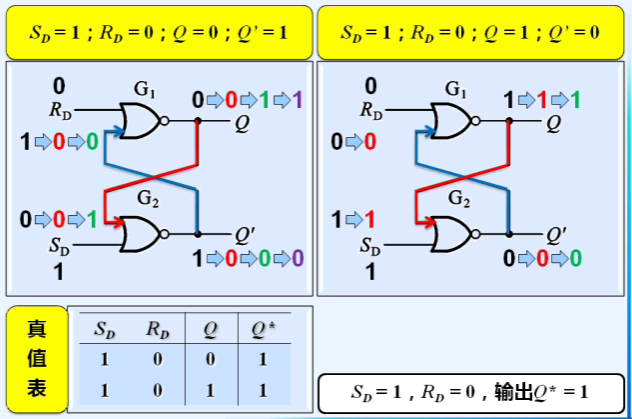

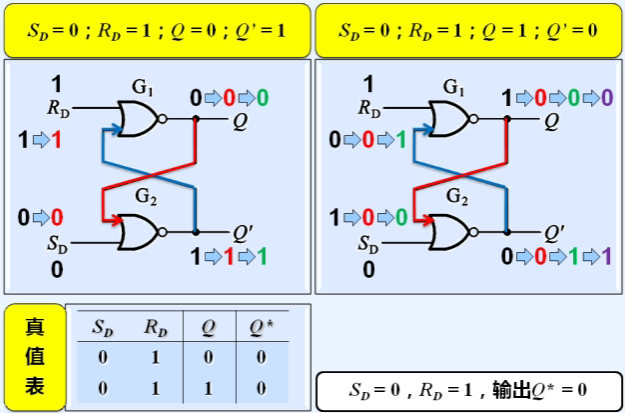

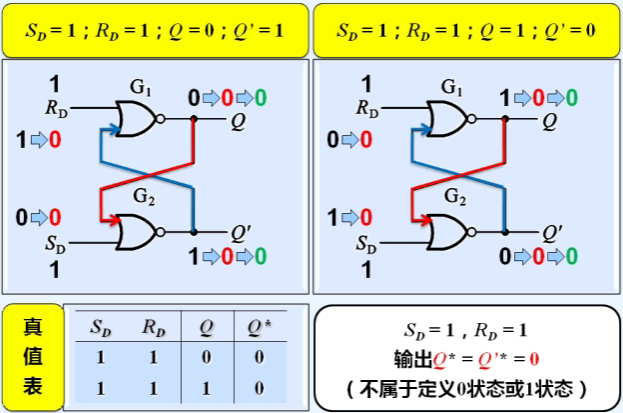

2.由两个或非门组成的SR锁存器的工作原理

注意区分Q Q' Q*

Q:原变量

Q':原变量的反变量

Q*:原变量在下一时刻的输出状态

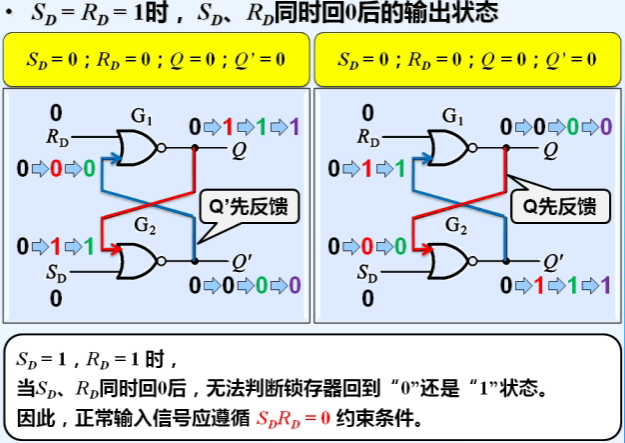

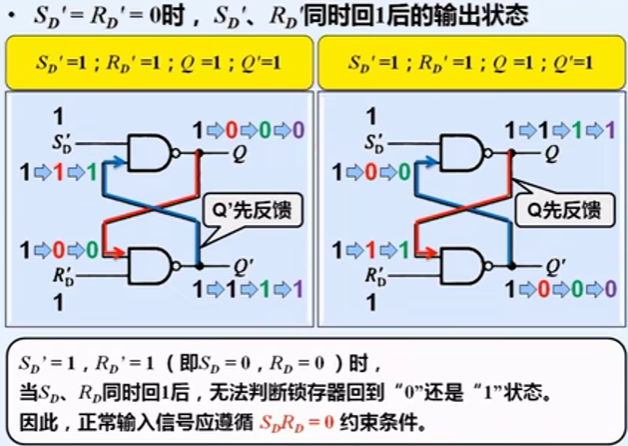

前面的同时反馈结果是稳定的,现在同时反馈结果不稳定,就假设先后。

假定Q'先发生反馈,上方反馈为1,下方还没响应,仍为0。假定Q先发生反馈分析方式与Q'先发生反馈相同。

这样理解,这就是一个卖矛和盾的事件,假如置零就说明你要买盾,你的盾可以仿万物能起作用,假如制1就是买矛,矛起作用可攻万物,那么同时制1 即用矛攻盾,没结果了嘛

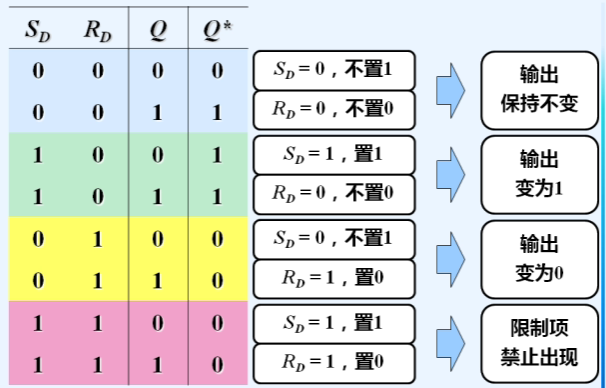

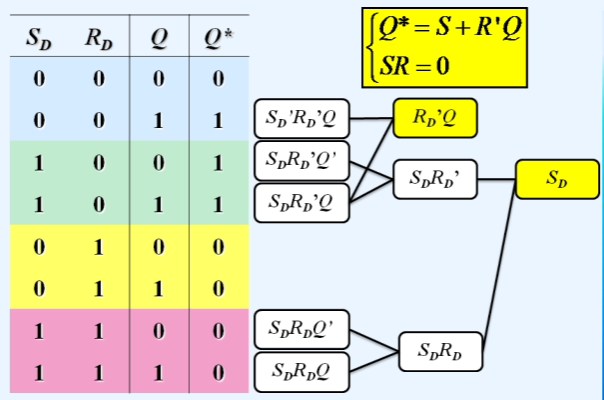

3.由两个或非门组成的SR锁存器的真值表/特性表

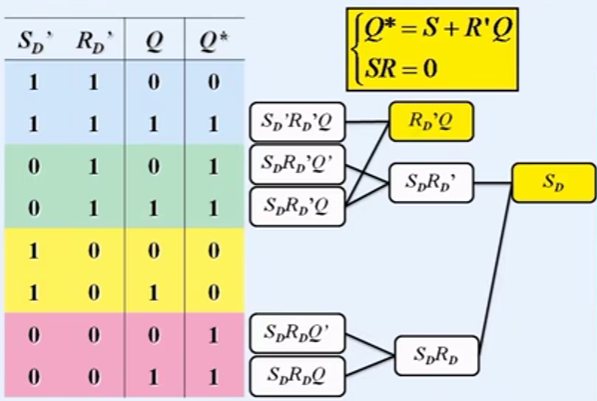

4.由两个或非门组成的SR锁存器的逻辑函数/特性方程

Q是上一次的输出,这一次的输入Q*是这一次的输出。

5.由两个或非门组成的SR锁存器的图形符号

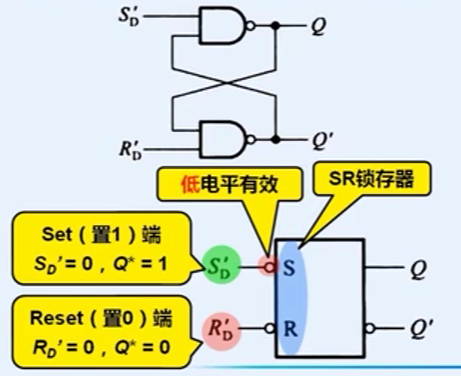

三、由两个“与非门”构成的SR锁存器

1.由两个与非门组成的SR锁存器的图形符号

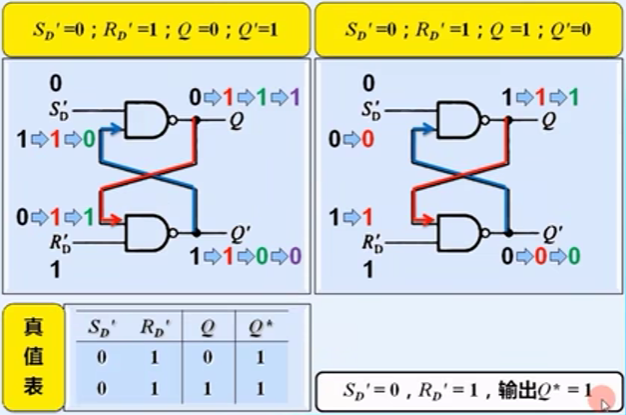

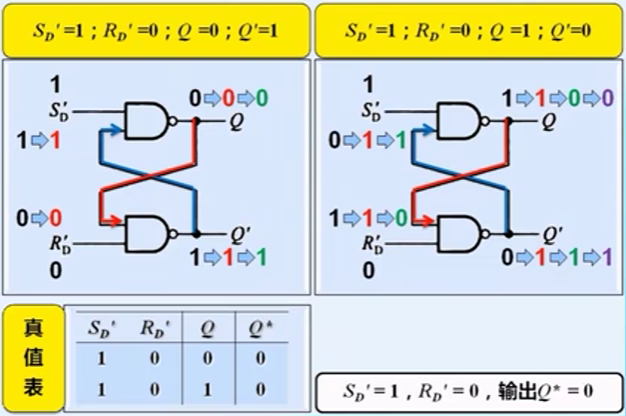

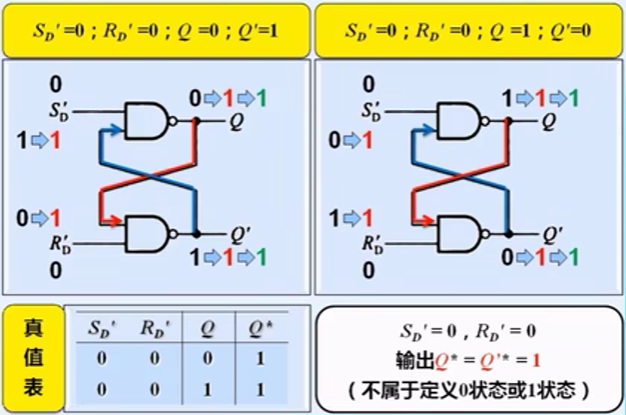

2.由两个与非门组成的SR锁存器的工作原理

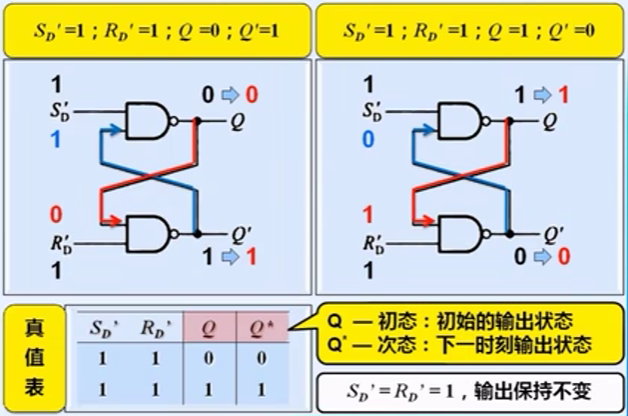

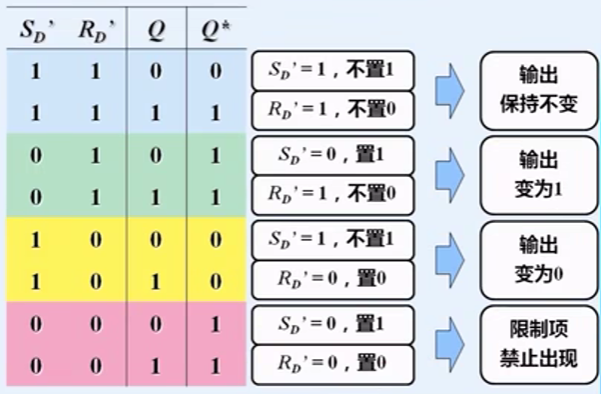

3.由两个与非门组成的SR锁存器的真值表/特性表

4.由两个与非门组成的SR锁存器的逻辑函数/特性方程

0表示取反,1表示保持。

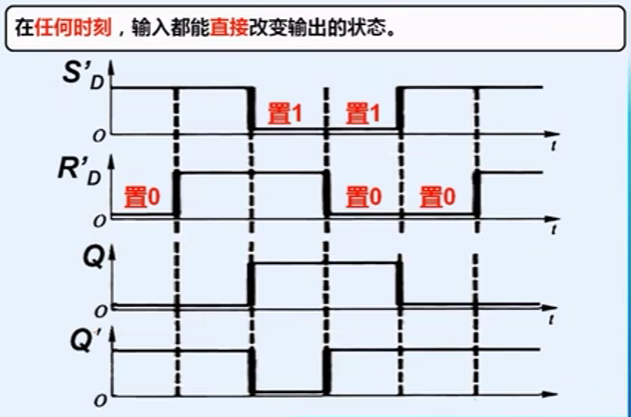

5.SR锁存器的动作特点

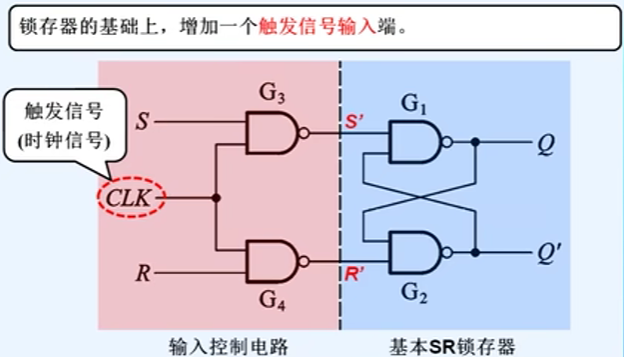

四、电平触发的SR触发器

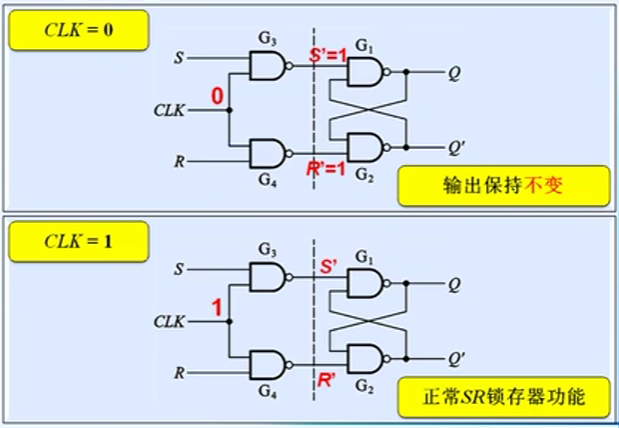

1.电路结构

2.工作原理

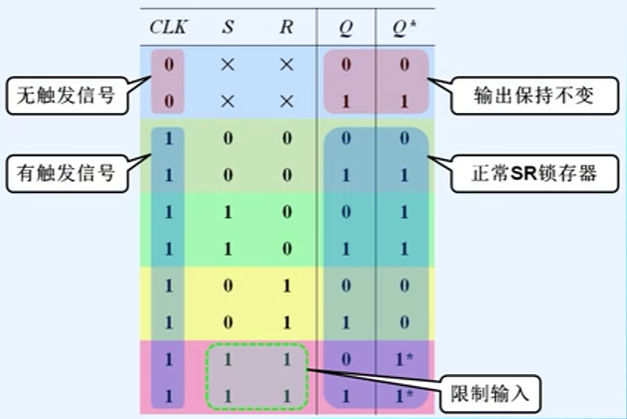

3.真值表/特性表

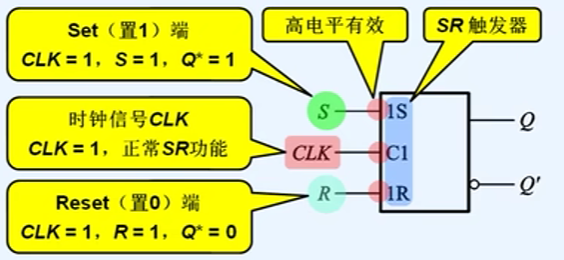

4.图形符号

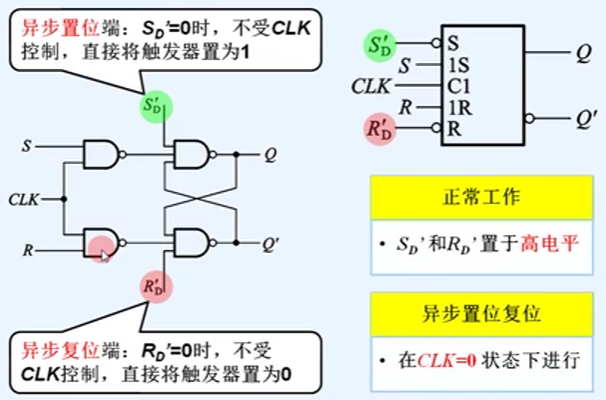

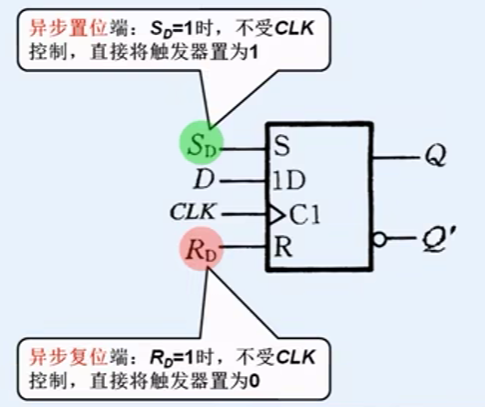

5.带异步置位、复位端的电平触发的SR触发器

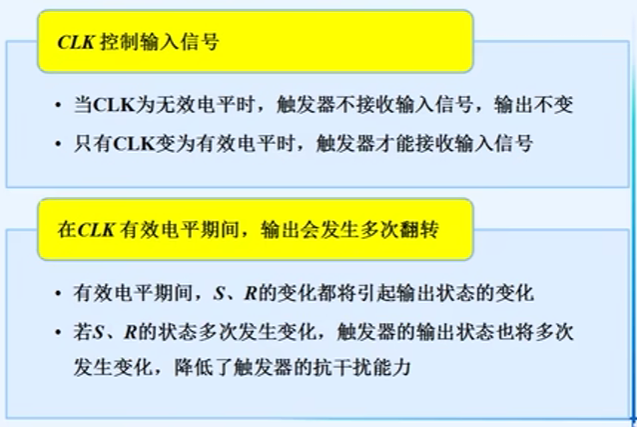

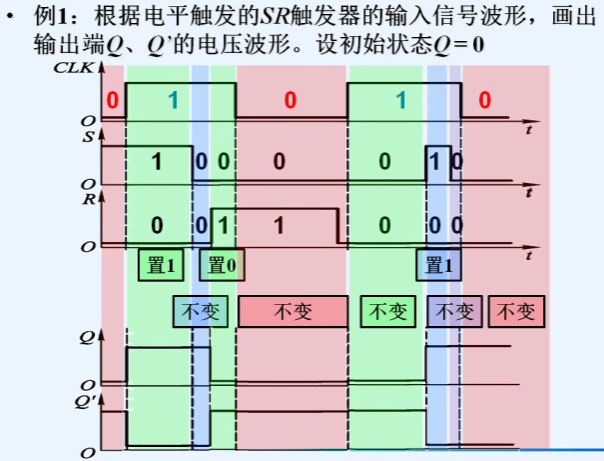

6.电平触发方式的动作特点

五、电平触发的D触发器

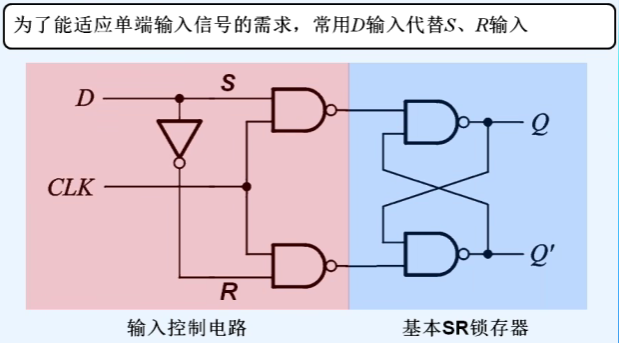

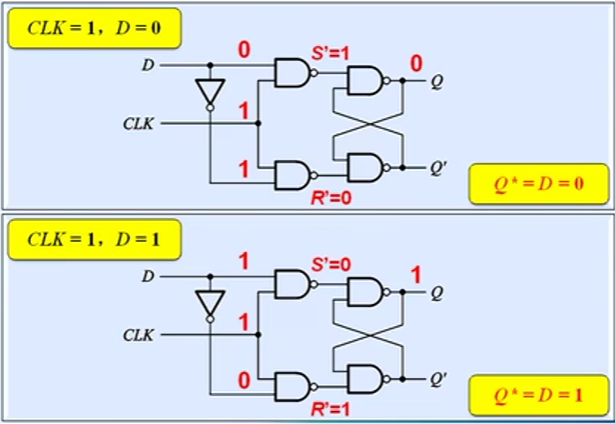

1.电路结构

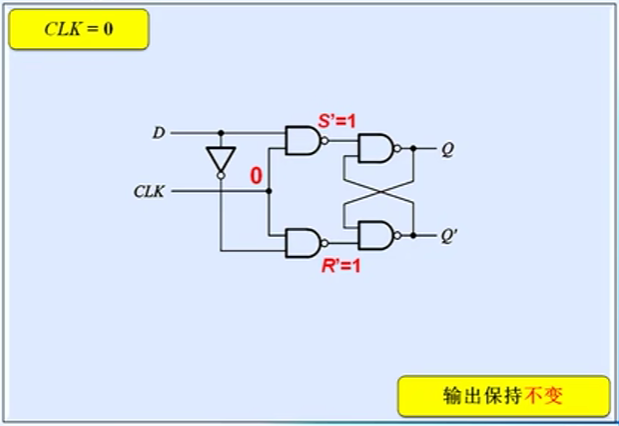

2.工作原理

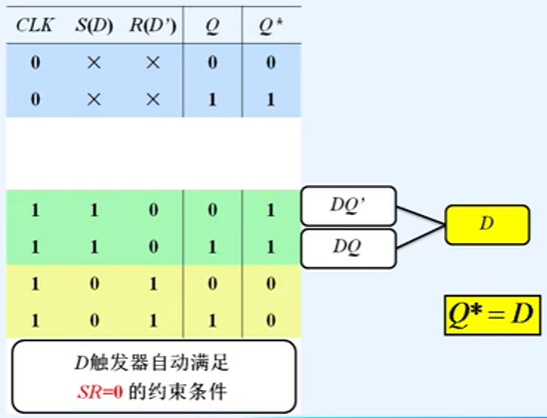

3.特性表与特征方程

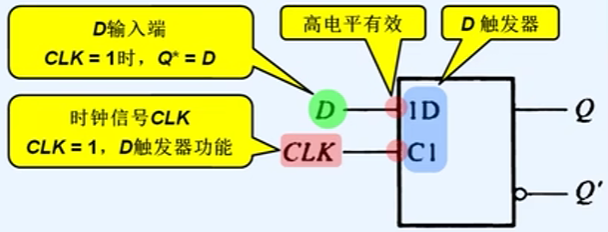

4.图形符号

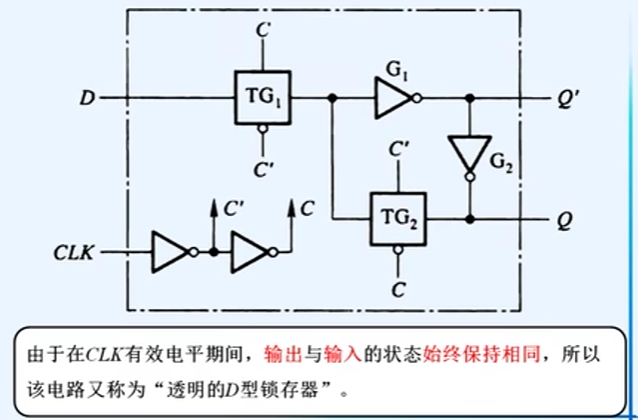

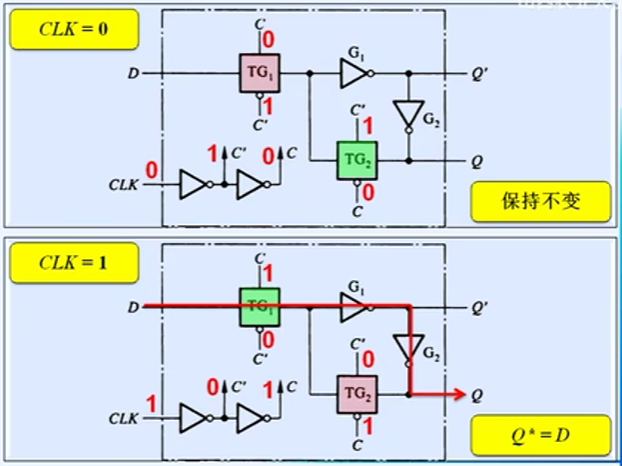

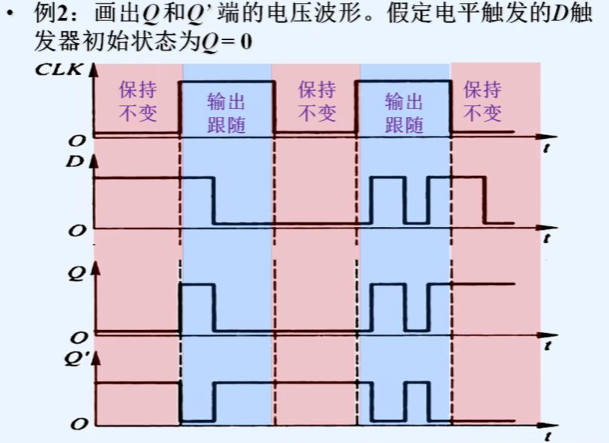

5.利用CMOS传输门组成电平触发的D触发器

TG2的作用是CLK=0时导通使Q与Q'可以形成内循环。

低电平输出保持不变,高电平输出跟随输入。

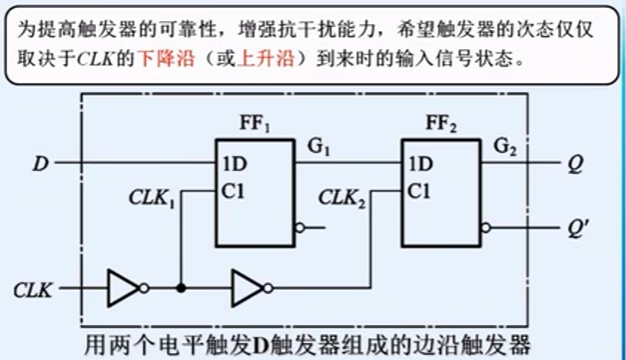

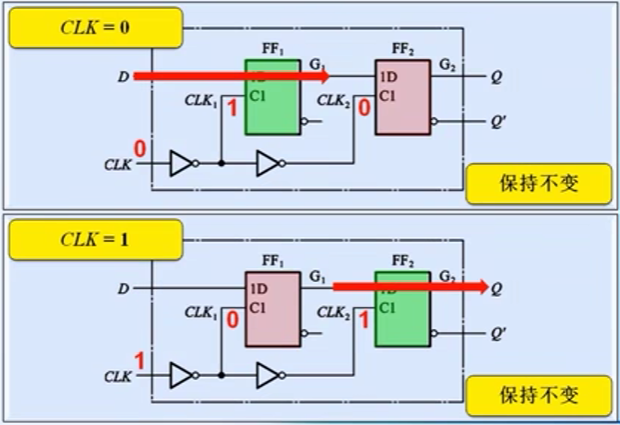

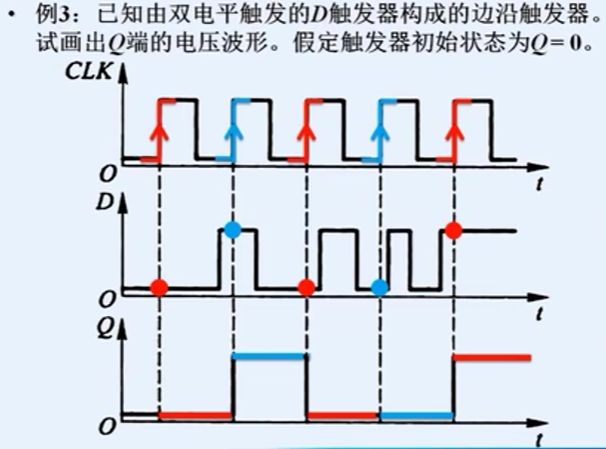

六、边沿触发的D触发器

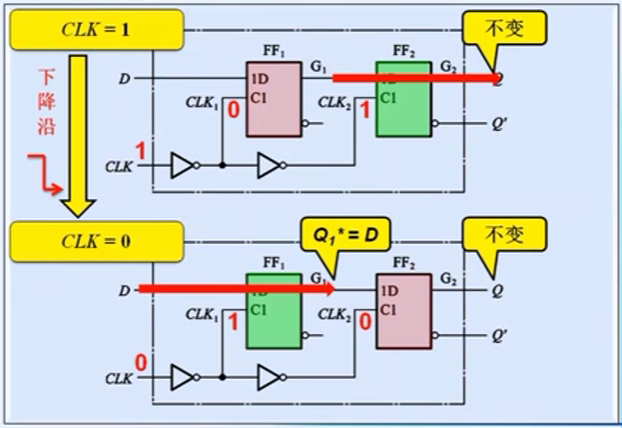

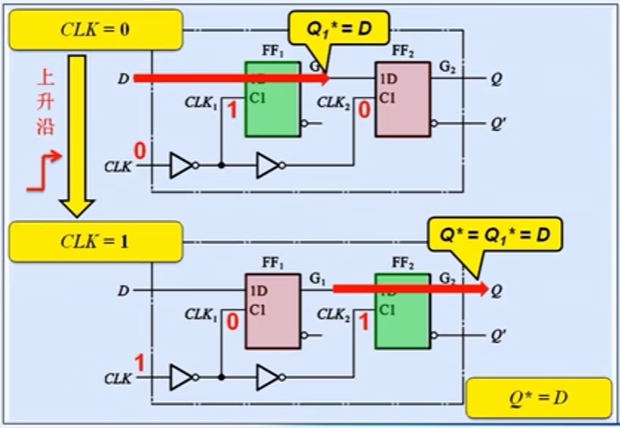

1.电路结构

2.工作原理

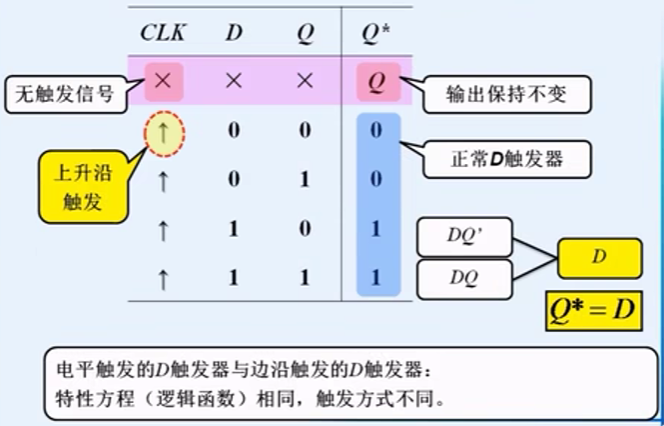

3.特性表与特性方程

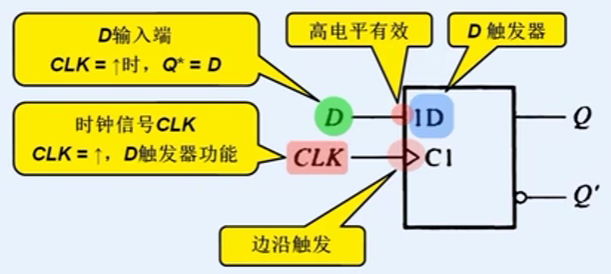

4.图形符号

5.带异步置位、复位端的边沿触发的D触发器

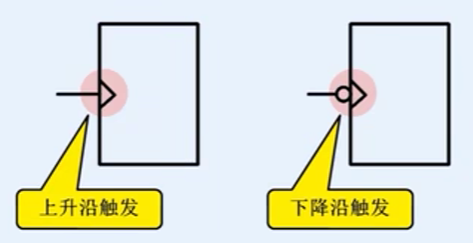

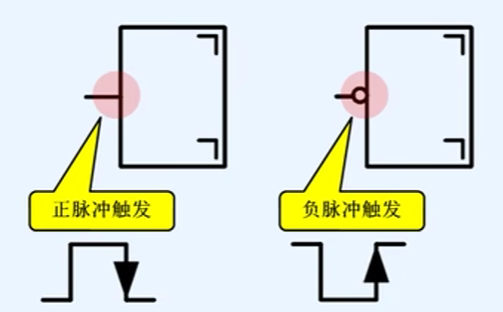

6.边沿触发的两类触发方式

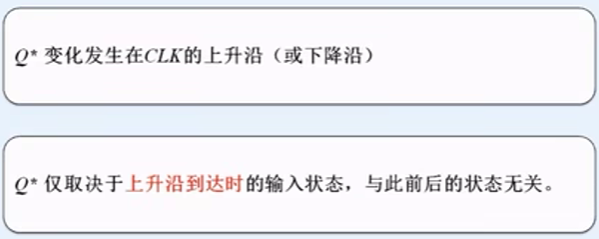

7.边沿触发方式的动作特点

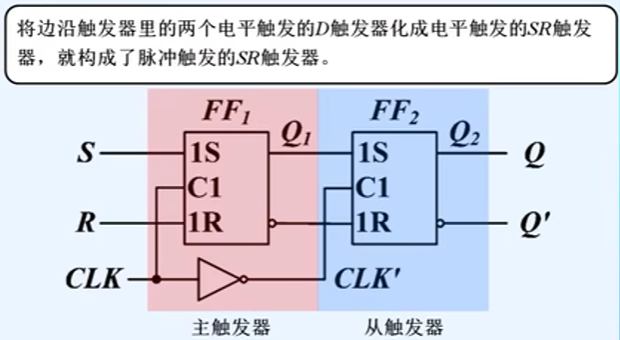

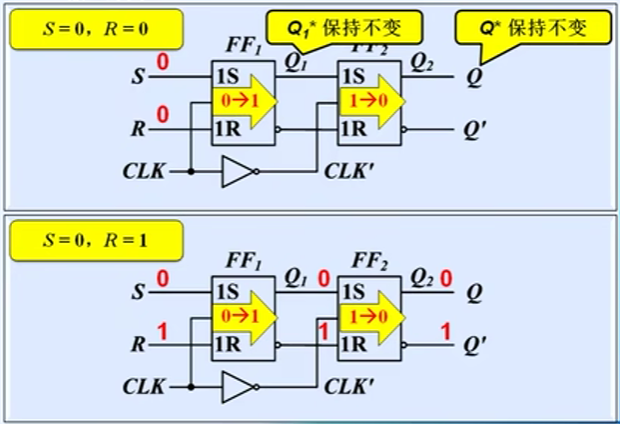

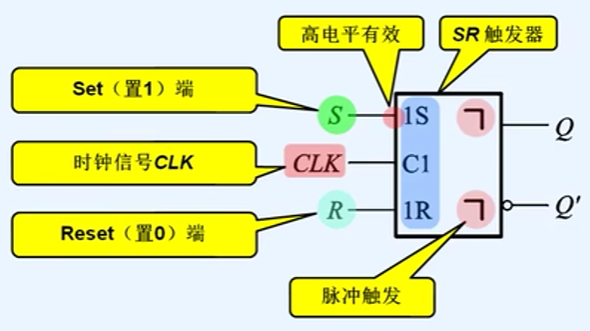

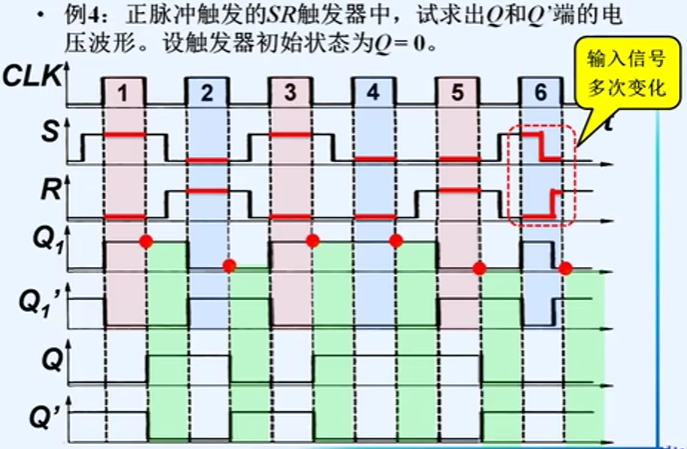

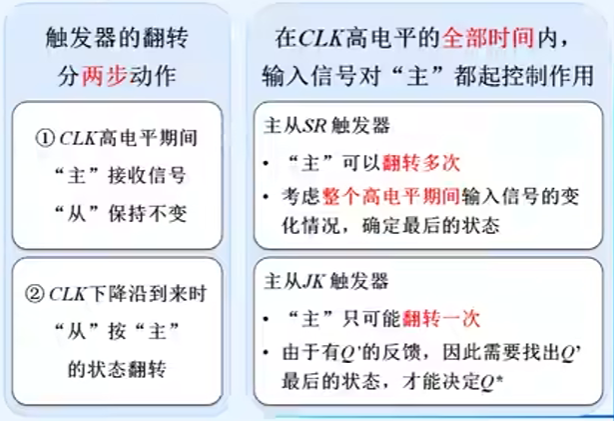

七、脉冲触发的SR触发器

1.电路结构

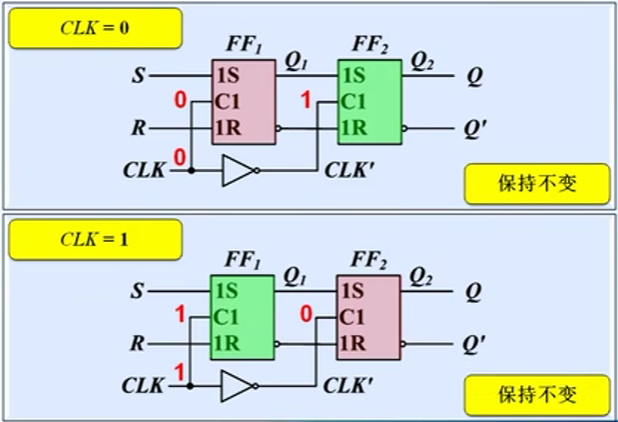

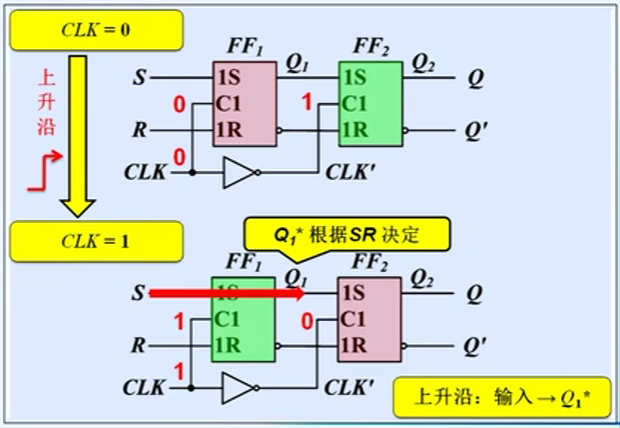

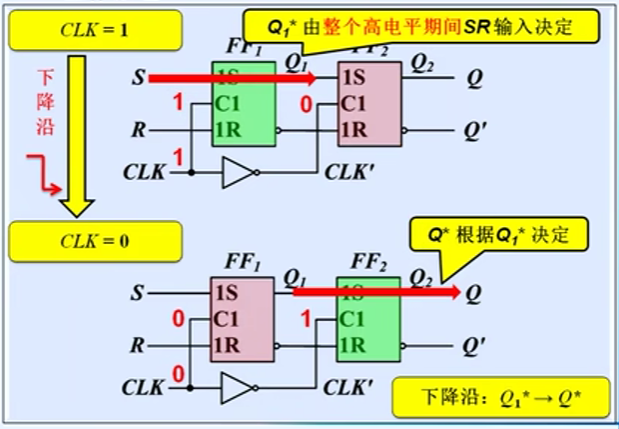

2.工作原理

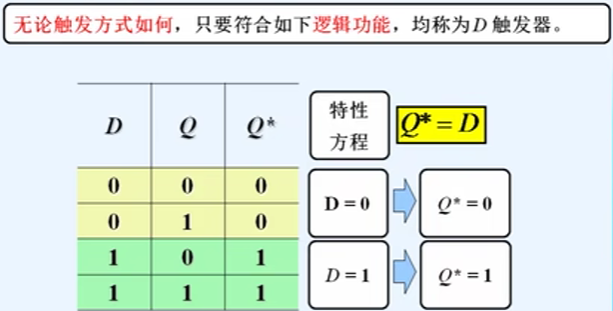

D触发器只有一个输入D(除去CLK),次态总是跟随输入,而SR触发器有两个输入(S和R),有可能SR同时为0,次态保持不变。

主从触发器的状态是同时改变的。

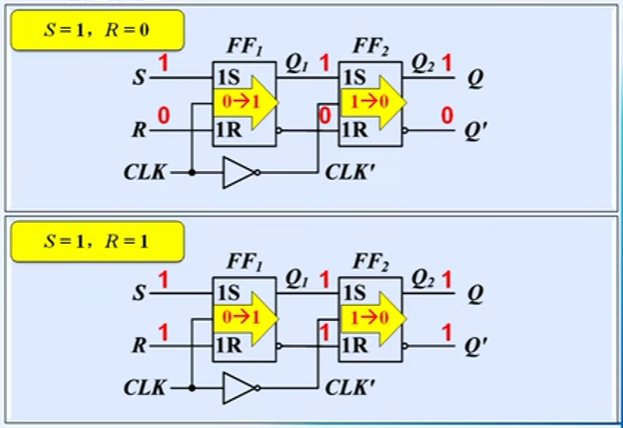

3.输出特性

4.特性表与特性方程

如果没有触发信号,整个电路处于截止状态。

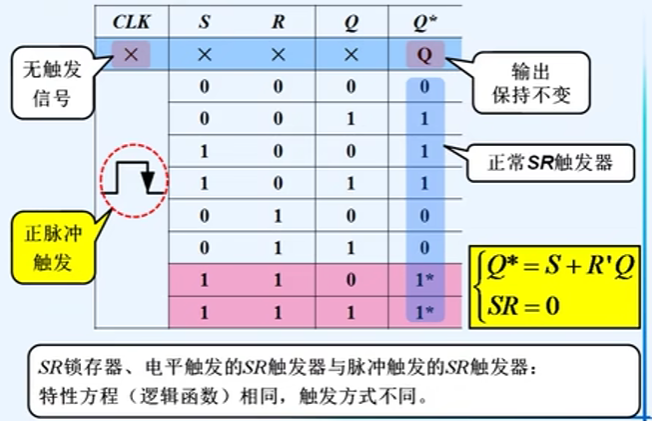

5.图形符号

6.脉冲触发的两类触发方式

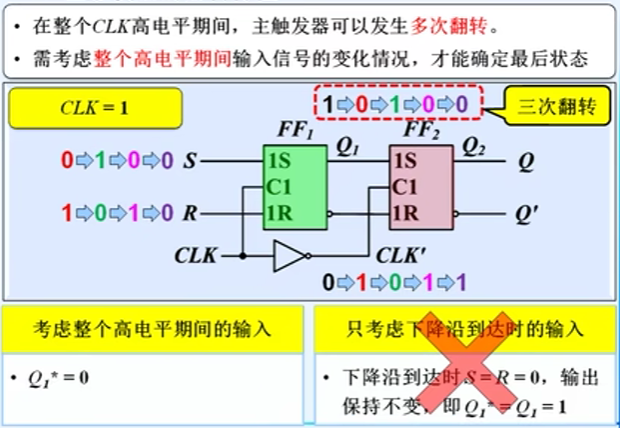

7.主触发器的翻转特性

主从SR虽然消除了空翻也解决了不定问题,但由于主触发器的空翻会使输出与真值表不符,从应跟随空翻之后的主Q*,而不是根据下降沿到来瞬间的SR决定。

脉冲触发的SR触发器在电压波形分析过程中,需要经历两个步骤:先分析高电平期间的中间变量Q1的变化情况,然后在下降沿到达的时刻,分析输出Q和中间变量Q1之间的跟随关系。

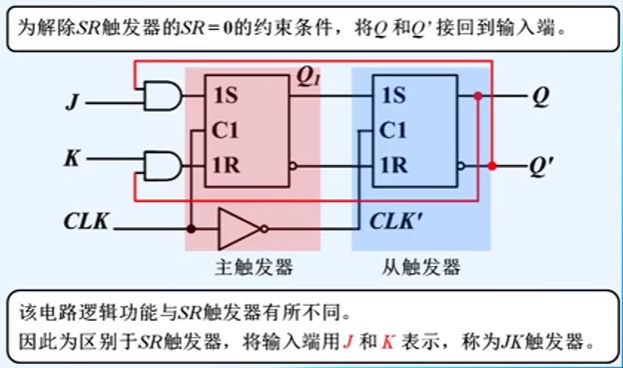

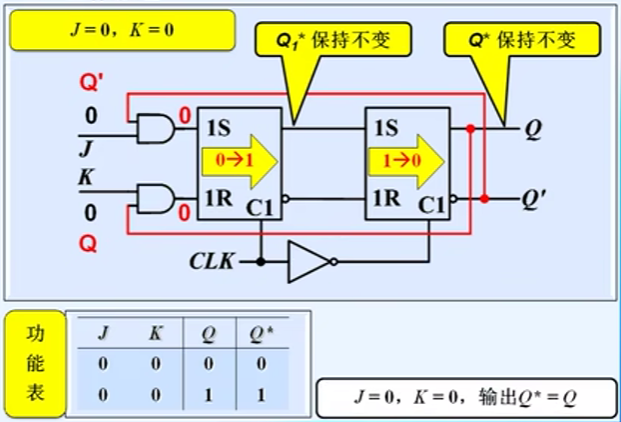

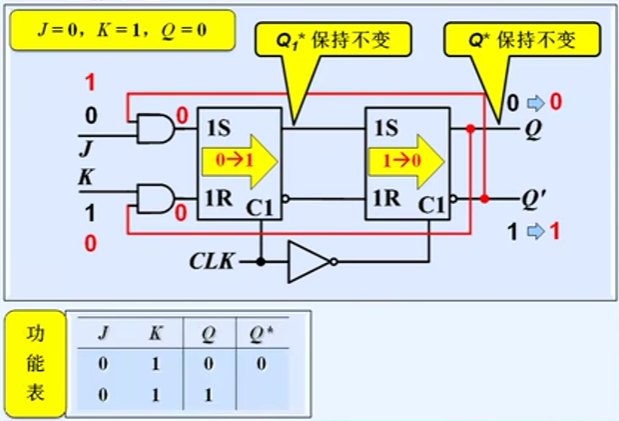

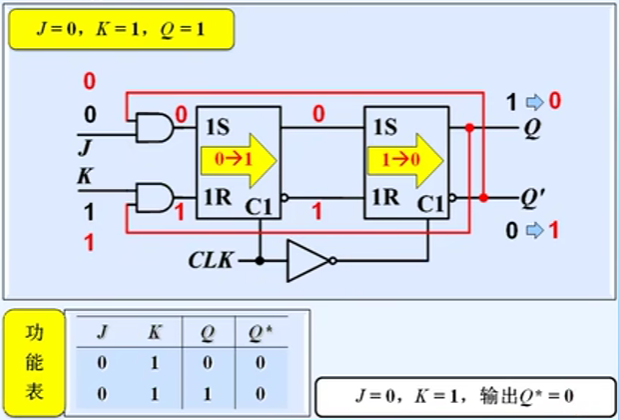

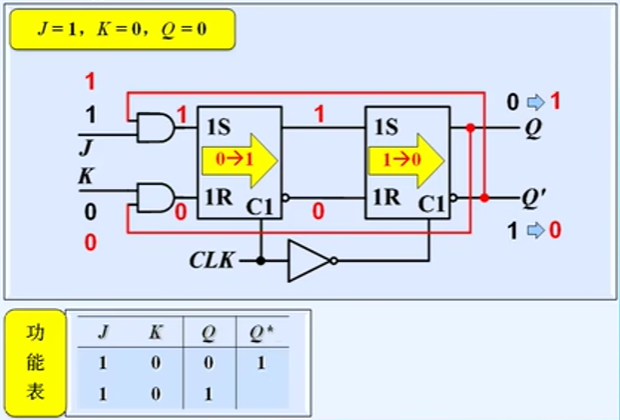

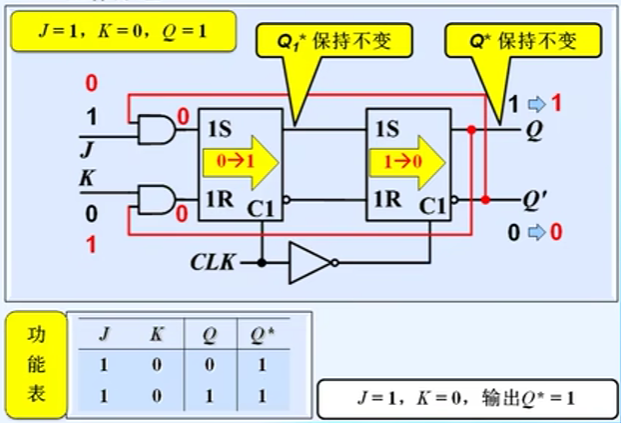

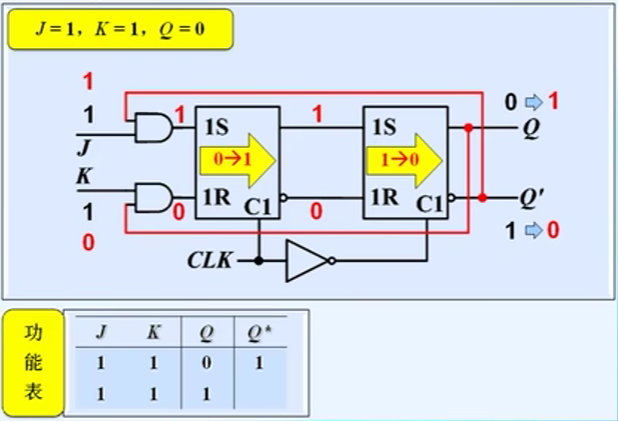

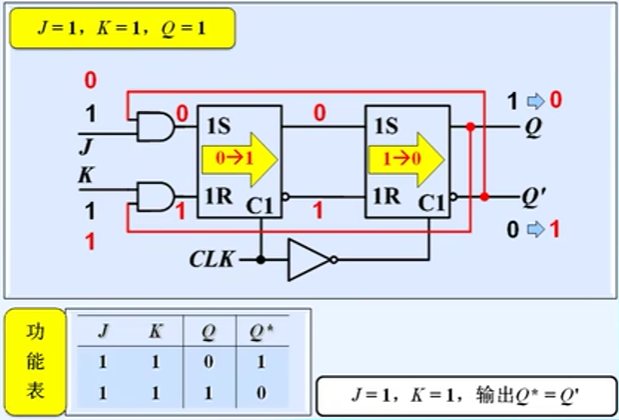

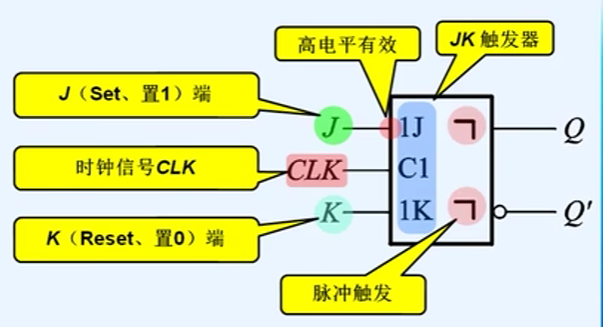

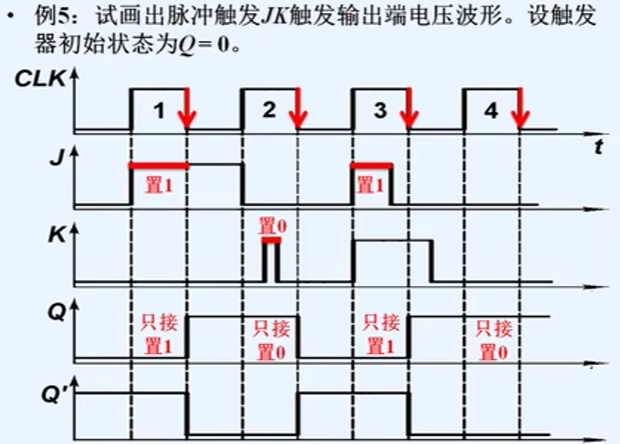

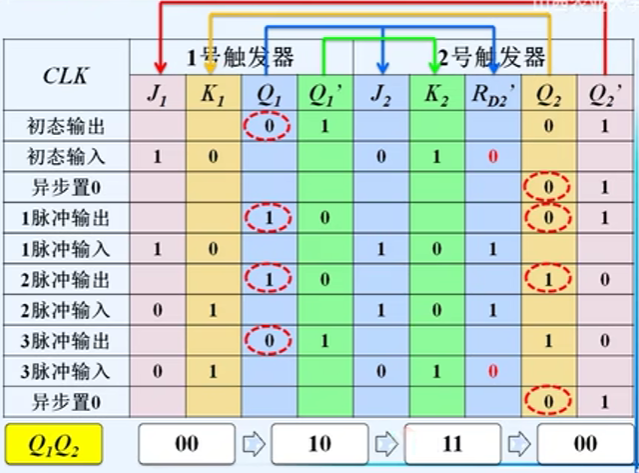

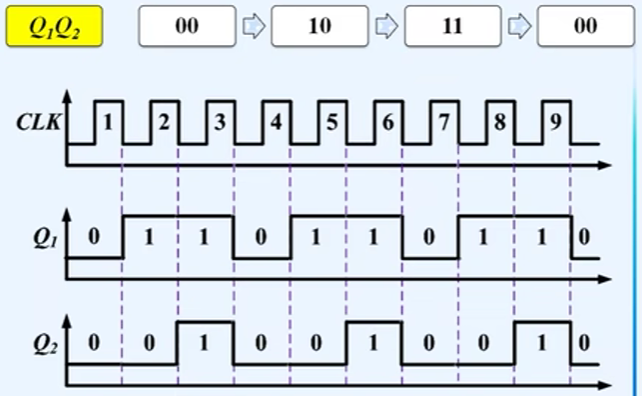

八、脉冲触发的JK触发器

1.电路结构

2.工作原理

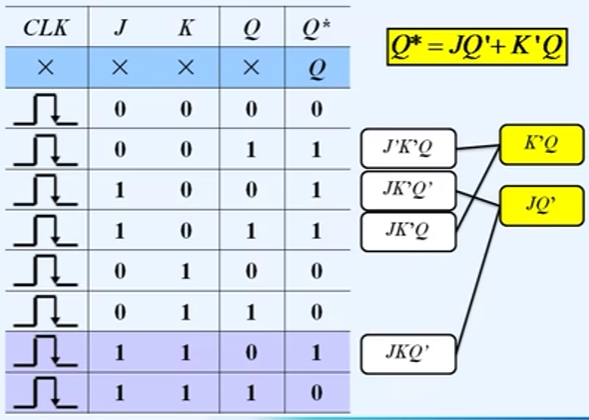

3.特性表与特性方程

4.图形符号

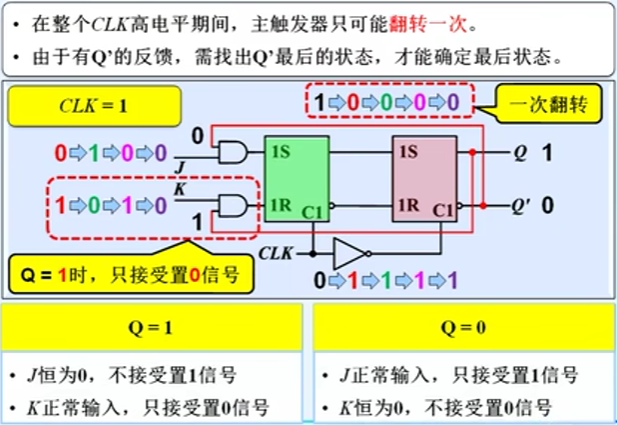

5.主触发器的翻转特性

JK触发器与SR触发器不同,输入信号加入了一个Q和Q'的反馈,所以要判断中间的Q1究竟变成了什么状态,就必须要找出Q'的输入状态,把Q'反馈回来,才能判断出输出最终变成了多少。

6.脉冲触发方式的动作特点

脉冲触发的SR触发器要分析S和R整个变化过程,推导出中间的Q1和Q1'的最终取值,然后再判断输出的变化。而JK触发器则不需要判断中间变量,只需要根据输出的Q的取值判断该状态下是只能接收0信号还是只能接收1信号,然后从输入端的信号里边找有没有相应的置0置1信号即可,如果有置1信号,而且只接收置1信号,则下一个时刻就会被置1,如果有置0信号,而且只接收置0信号,则下一个时刻就会被置0,如果既不出现置0信号,也不出现置1信号,就保持原状态不变,不需要再分析中间究竟是怎样翻转的,而是可以直接得到最终的输出的电压波形。

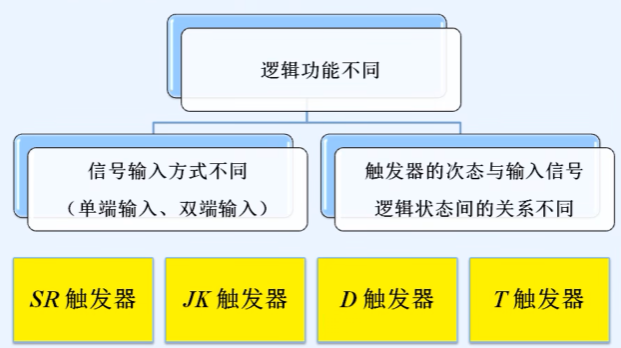

九、触发器按逻辑功能的分类

1.触发器按逻辑功能的分类

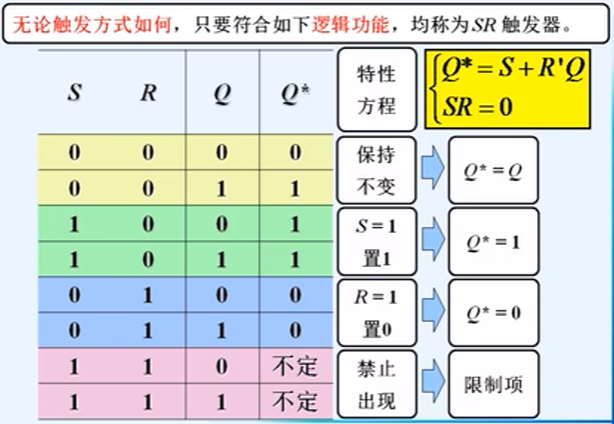

2.SR触发器

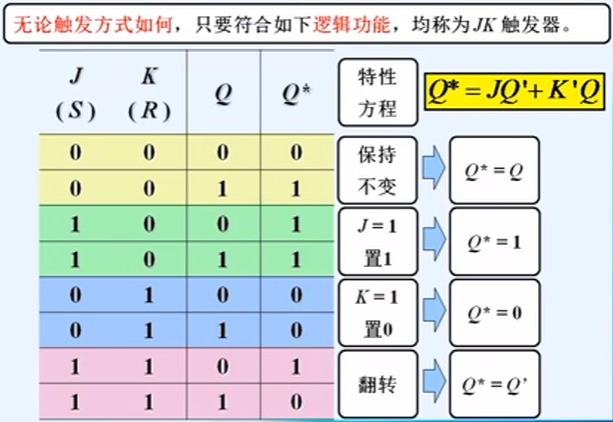

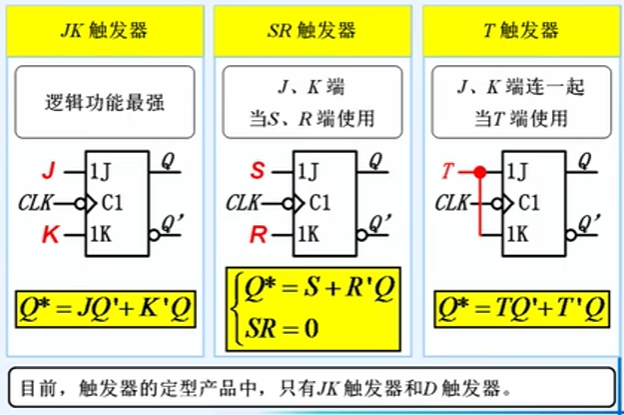

3.JK触发器

4.D触发器

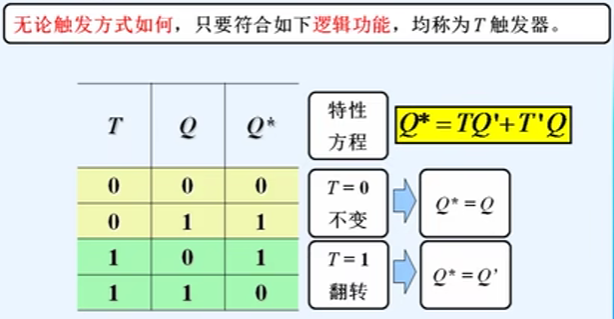

5.T触发器

6.不同触发器间的关系

在实际应用的过程中,通过接线的不同,来实现SR触发器和T触发器的功能。

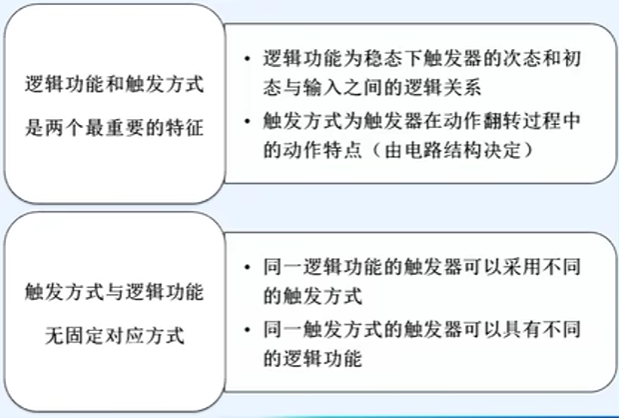

7.触发方式与逻辑功能

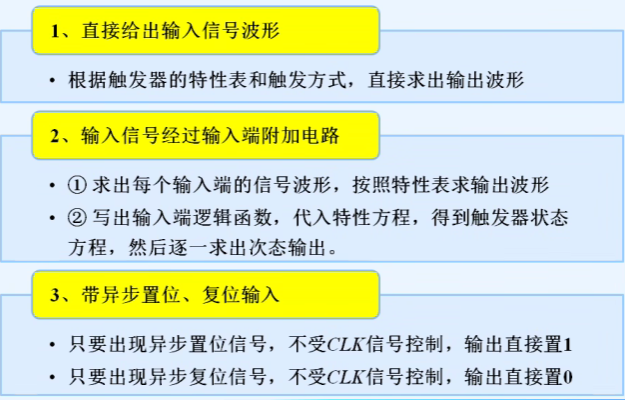

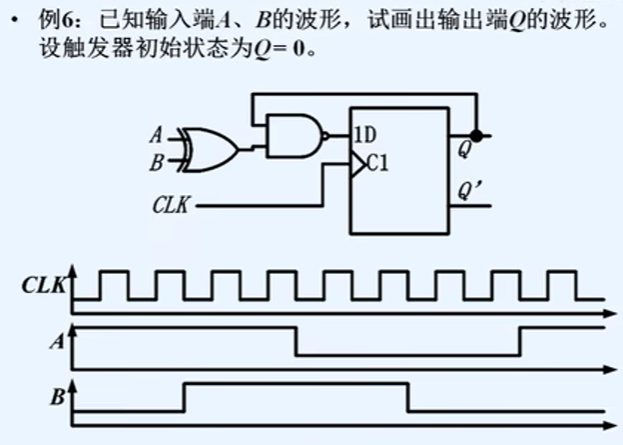

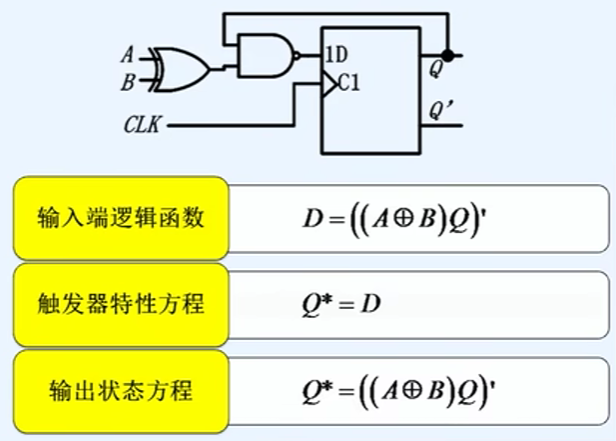

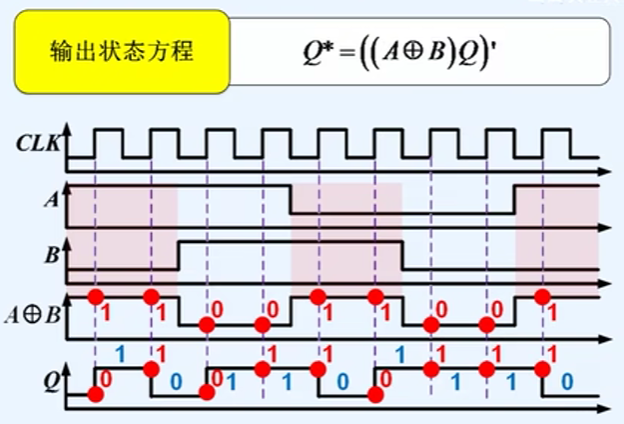

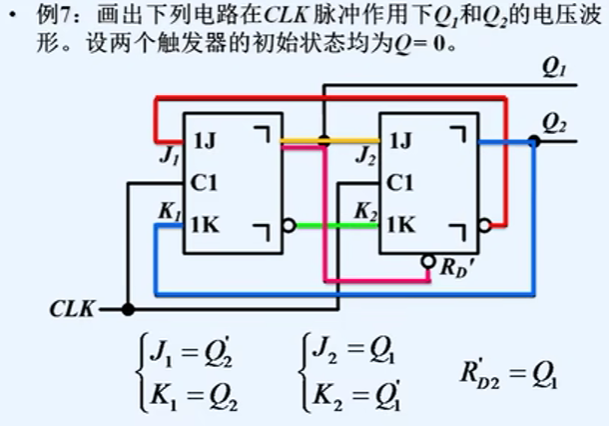

九、一直触发器的输入波形,求输出波形

做题步骤:先推导了输入附加电路的逻辑函数,然后代入触发器的特性方程,得到了输出端Q的状态方程,然后主次把相应的ABQ的取值代入状态方程,得到了次态Q*的取值,从开始一步步推导,最终得到了整个输出端Q的电压波形。在该过程中,需要注意的是触发方式,根据触发方式去选择输出电平变化的时间节点,从而完成正确的输出波形的绘制。

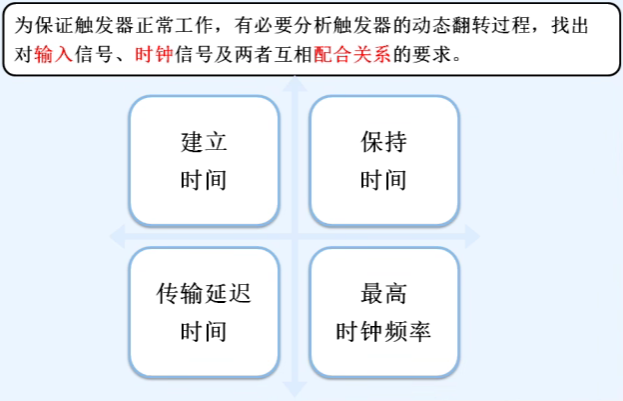

十、触发器的动态特性

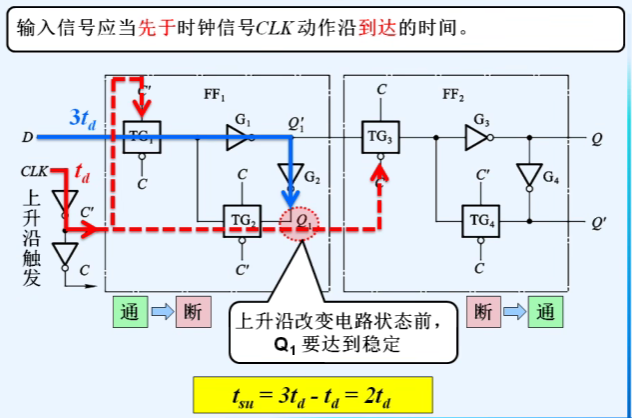

1.建立时间(Setup time)tₛᵤ

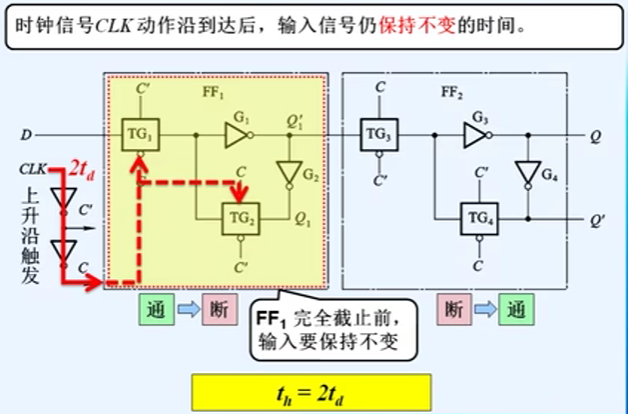

2.保持时间(Hold time)tₕ

为了保证Q1是一个稳定的结果,所以需要让输入的D信号再保持一段时间,直到FF1完全截止。

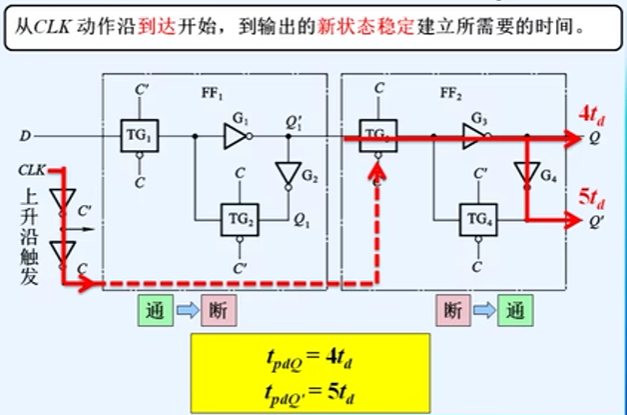

3.传输延迟时间(Propagation delay time)

实际上,建立时间、保持时间和传输延迟时间实际上讲的是输入信号和时钟信号之间的配合关系,这三个时间共同决定了我们脉冲信号的一个频率。

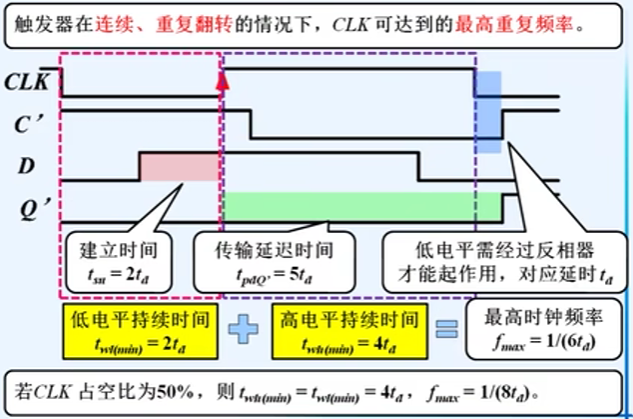

4.最高时钟频率(Maximum clock frequency)fₘₐₓ

根据上述三类时间可以推出,在实际工作的情况下,我们能够加载的最高时钟频率是多少。

在用该触发器工作的时候,时钟信号的频率不能够超过该频率,否则的话触发器就不能正常工作了。

实际上,不管是建立时间、保持时间、传输延迟时间还是最高时钟频率,都是在一些比较理想的假设的条件下得出的。比如假设所有门电路的传输延迟都是td,但是在实际情况下,每一个门电路传输延迟都有所区别,因此对于一个触发器,它的动态参数往往是通过实验测量的手段来得出的。

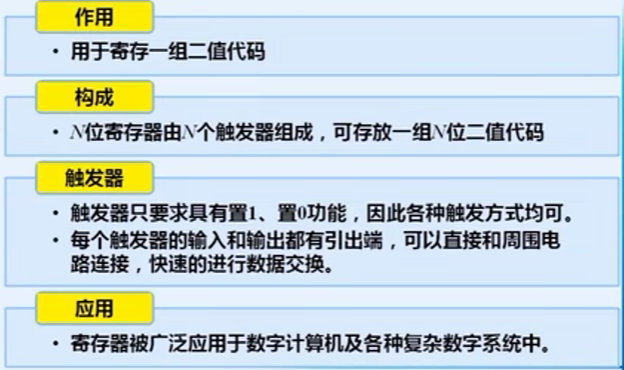

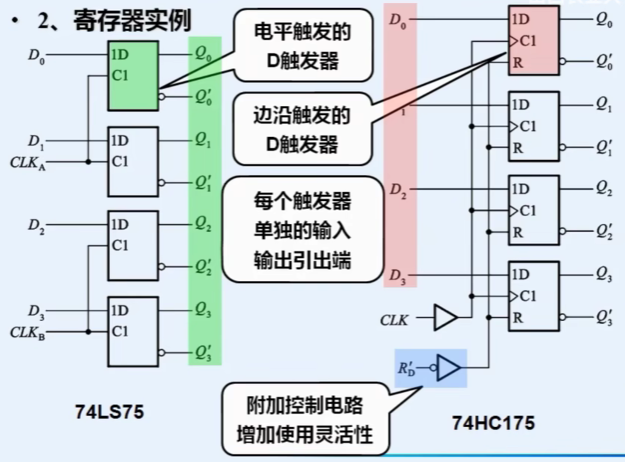

十一、寄存器

1.寄存器的概念

2.寄存器实例

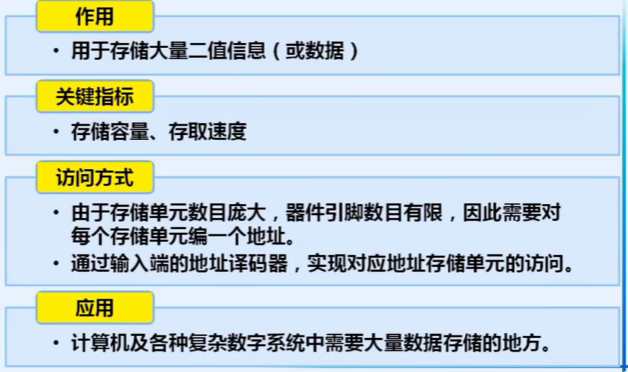

十二、存储器

1.存储器的基本概念

寄存器存储读取速度快但是贵,所以为了提高计算机的速度,又为了经济效益,计算机一般是寄存器+存储器一起使用,先访问寄存器,寄存器里要是没有的数据,再访问存储器(这样可以加快电脑速度)。

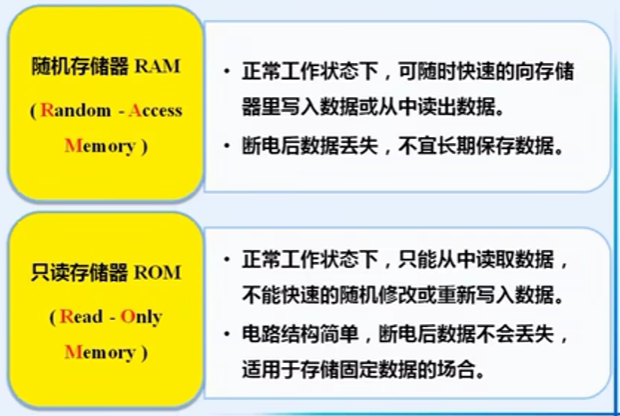

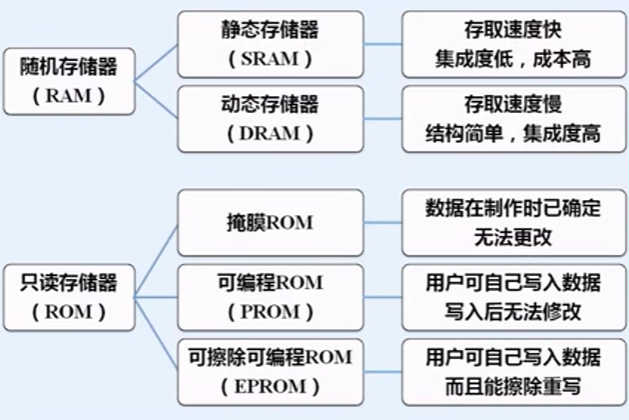

2.存储器根据存/取功能分类

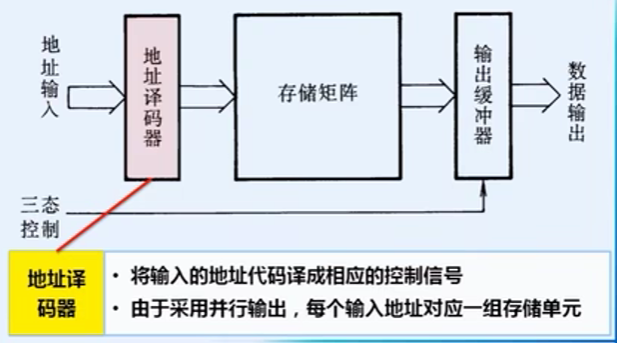

十三、随机存储器(RAM)

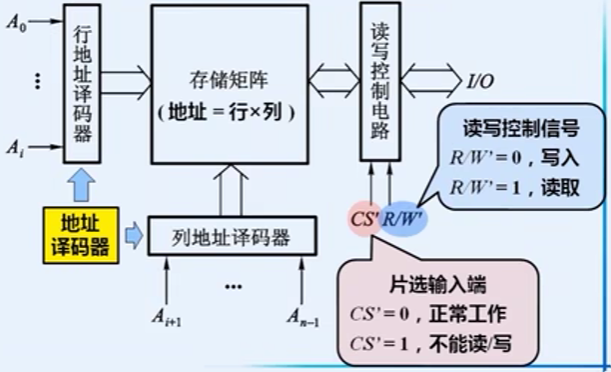

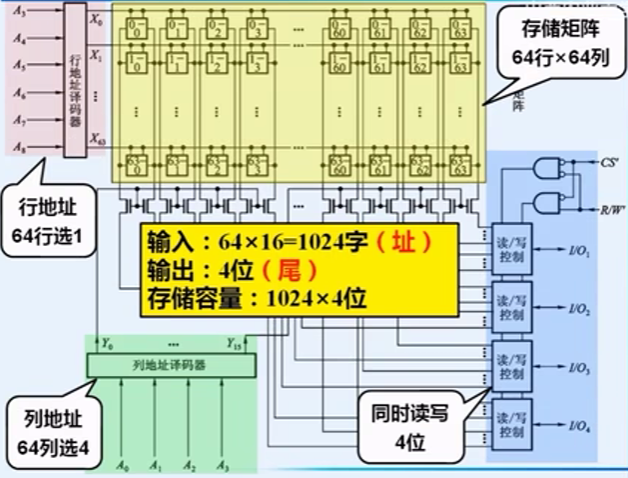

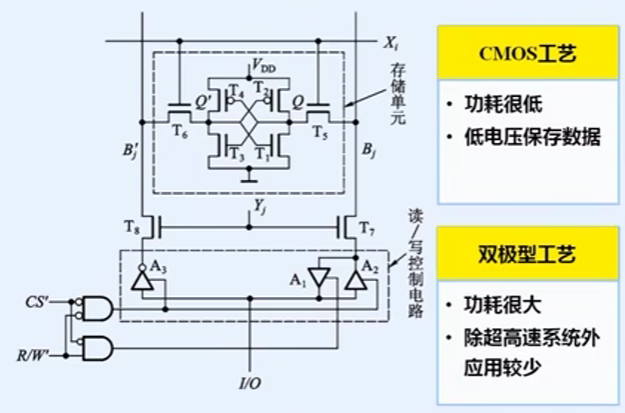

1.静态随机存储器(SRAM)的电路结构

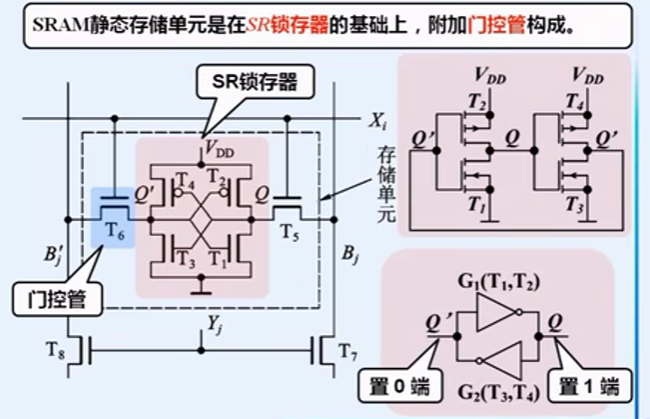

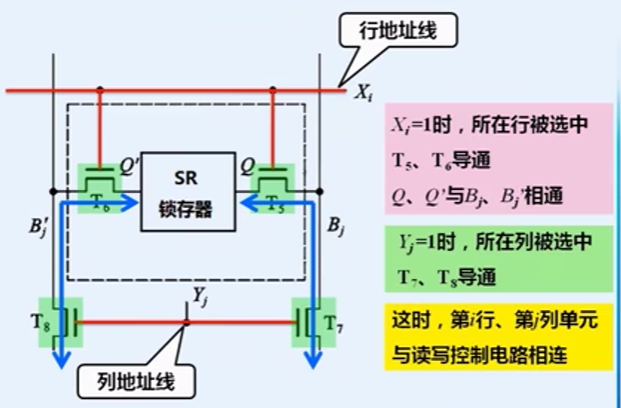

2.SRAM的静态存储单元

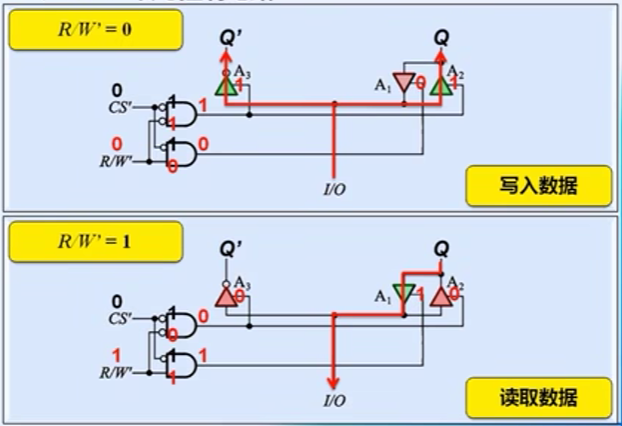

3.SRAM读写控制电路

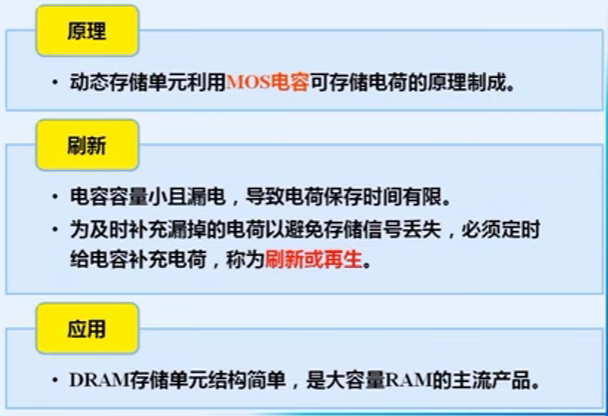

4.动态随机存储器(DRAM)

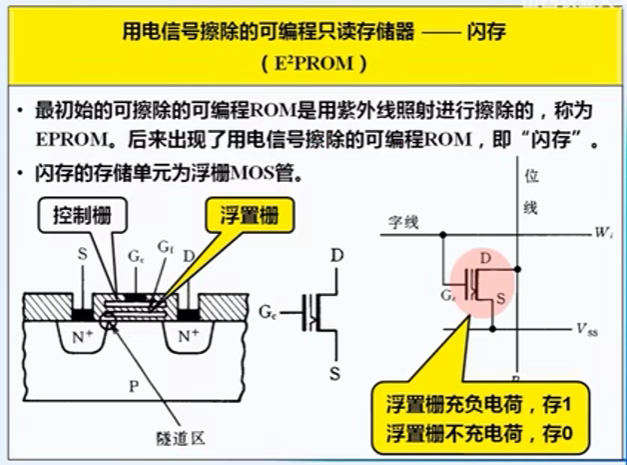

十四、只读存储器(ROM)

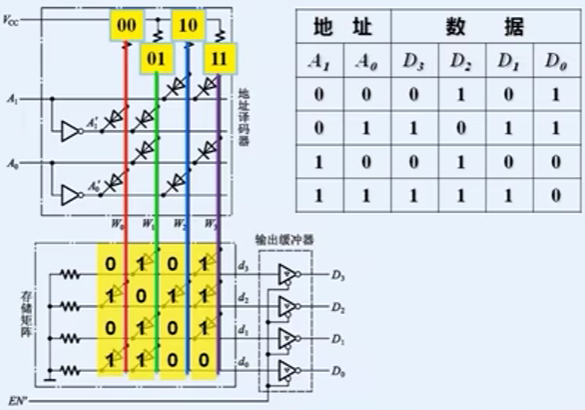

1.ROM的电路结构

2.二极管ROM的电路结构

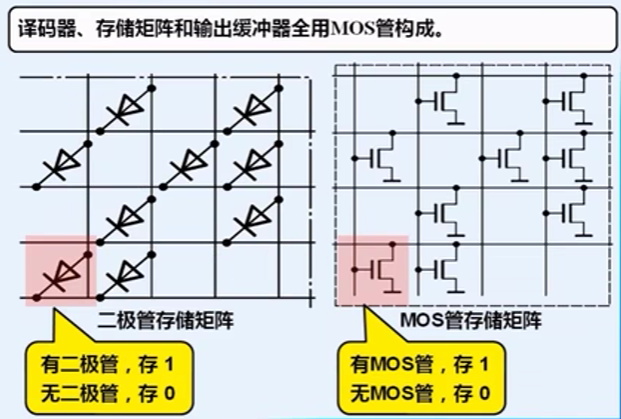

3.MOS管工艺的ROM

4.二极管ROM的工作原理

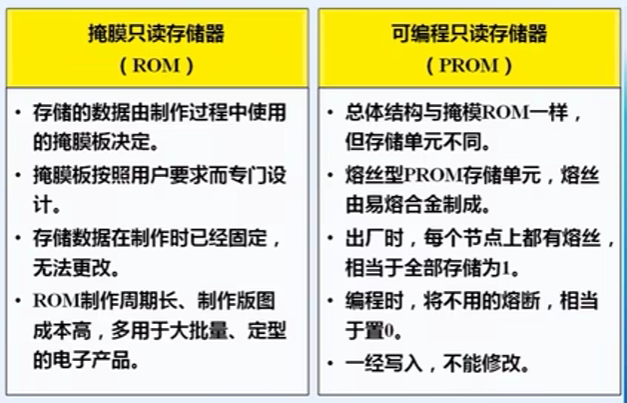

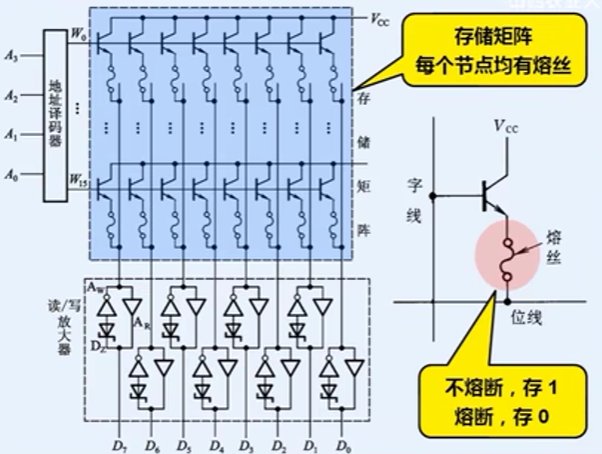

5.ROM的分类

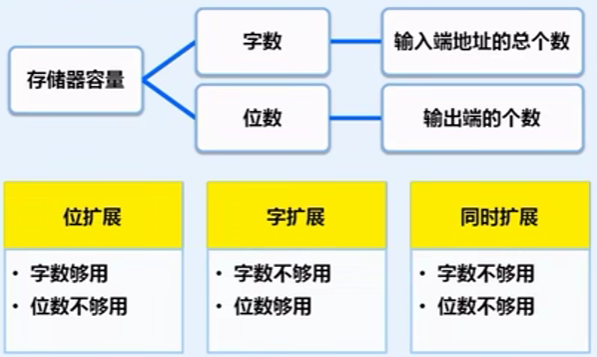

十五、存储器容量的扩展

1.存储器容量的扩展类型

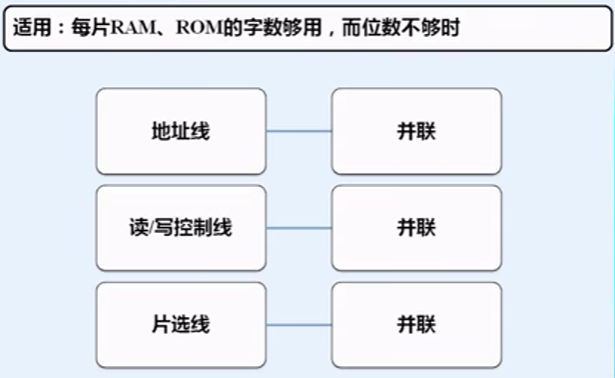

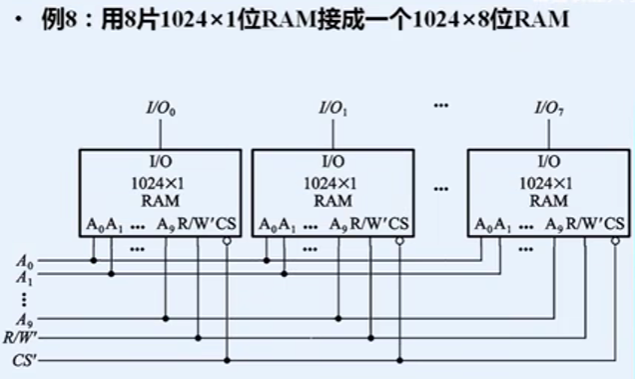

2.位扩展方式

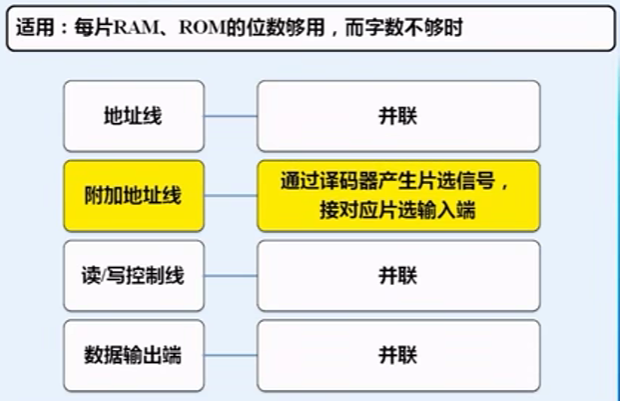

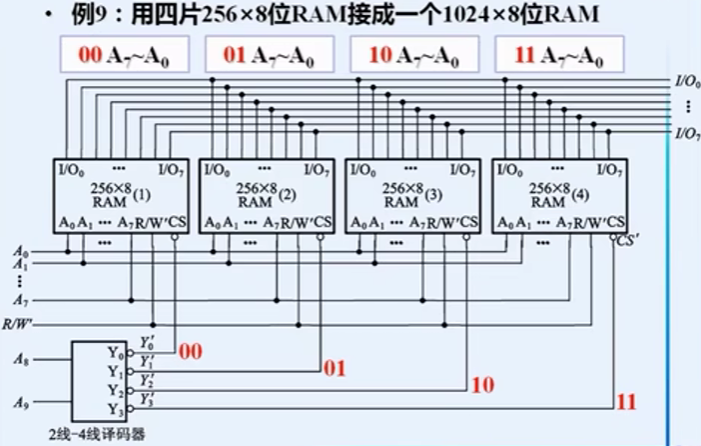

3.字扩展方式

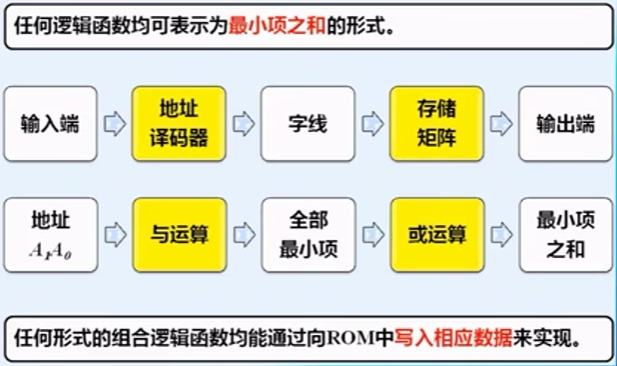

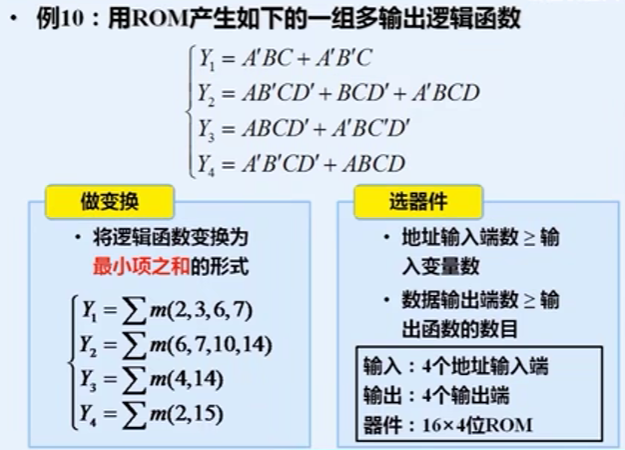

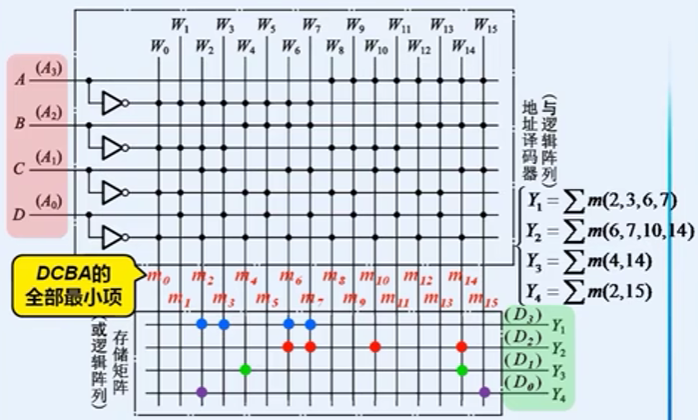

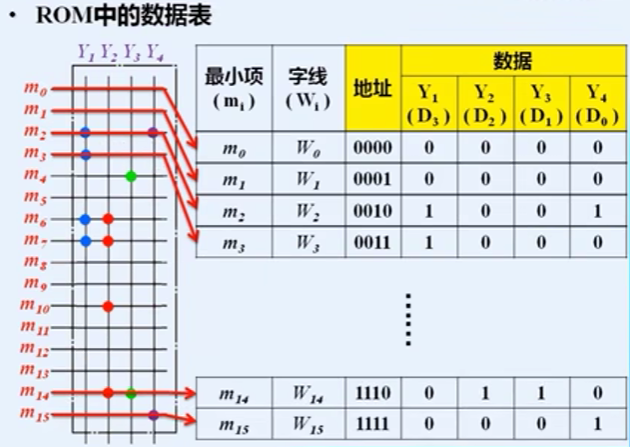

十六、用存储器实现组合逻辑函数

1.设计原理

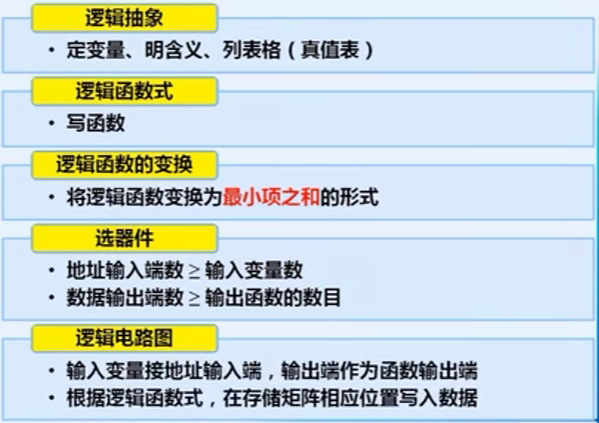

2.设计步骤

注:本文出自对bilibili 王文俊讲电气数字电子技术基础 内容的学习笔记。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?