目录

1. 简介

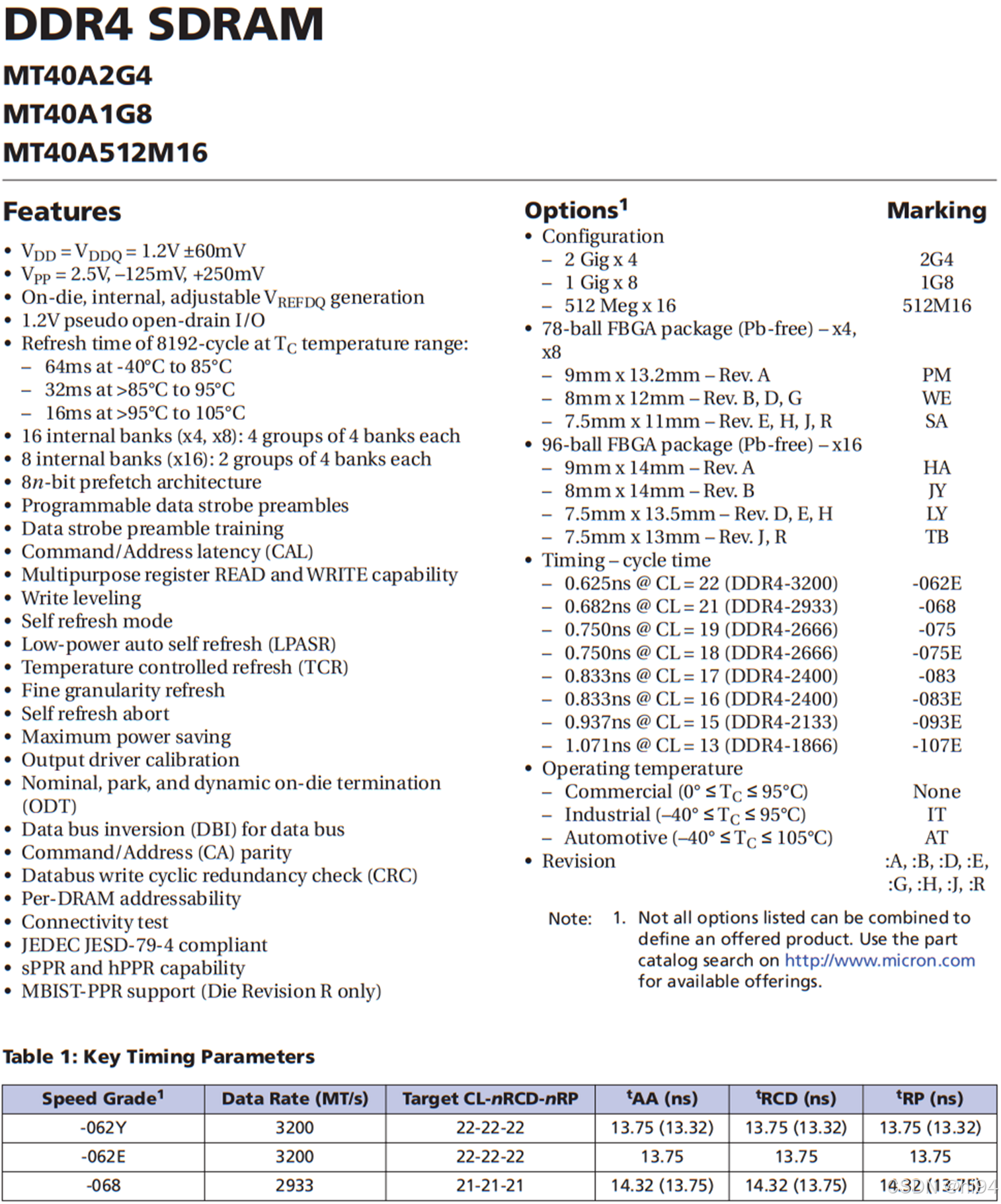

1.1 DDR4 DS 首页

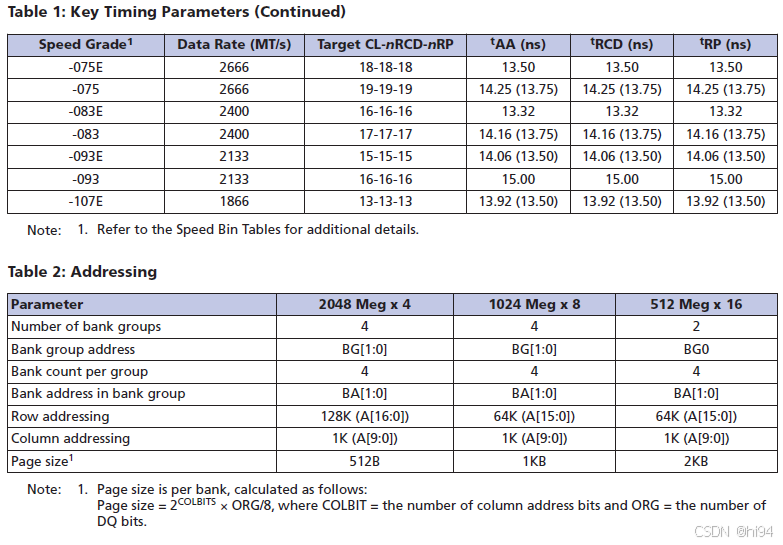

1.2 DDR4 结构框图

1.3 DDR Generations

| DDR | DDR2 | DDR3 | DDR4 | DDR5 | |

| Release | 1998 | 2003 | 2007 | 2014 | 2020 |

| Bus CLK [MHz] base Bus CLK [MHz] EXT |

100-200 | 200-400 | 400-800 (933, 1066) |

800-1600 | 1600-3200 (3400) |

| DataRate base DataRate EXT |

200-400 | 400-800 | 800-1600 (1866, 2133) |

1600-3200 | 3200-6400 (6800) |

| Internal banks | 4 | 4, 8 | 8 | 8, 16 | 8, 16, 32 |

| Max. capacity (Gb) | 1 | 4 | 8 | 16 | 32 |

| Bit Width | x4, x8, x16 | x4, x8, x16 | x4, x8, x16 | x4, x8, x16 | x4, x8, x16 |

| Prefetch | 2n | 4n | 8n | 8n | 16n |

| std: VDD/VDDQ/VPP Low volt version |

2.5 | 1.8 | 1.5/1.5/na 1.35/1.5/na |

1.2/1.2/12.5 | 1.1 |

1.4 Xilinx IP 特征

- 支持 8~80 bit 接口宽度的组件(支持 RDIMM、LRDIMM、UDIMM 和 SODIMM)

- 密度支持

- 最高支持 32 GB 的组件密度,64 GB 的 LRDIMM,128 GB 的 RDIMM,16 GB 的 SODIMM 和16 GB 的 UDIMM。

- 其他内存设备支持的密度可通过自定义部件选择获得支持。

- AXI4 Slave 接口

- 支持 x4、x8 和 x16 组件

- DDR4 RDIMM、SODIMM、LRDIMM 和 UDIMM 的双槽支持

- 8-world 突发支持

- 支持 9~24 个列地址脉冲(CAS)延迟(CL)

- 支持 9~18 个 CAS 写延迟周期

- ODT支持

- 3DS RDIMM 和 LRDIMM 支持

- 3DS 组件支持

- Verilog 源代码交付

- 4:1 内存到 FPGA 逻辑接口时钟比率

- 开放、封闭和基于事务的预充电控制器策略

- 通过 Vivado 硬件管理器提供接口校准和训练信息

- 非 AXI4 72位接口的可选纠错码(ECC)支持

- 不支持写操作的 CRC

- 不支持地址/命令总线的 2T 定时

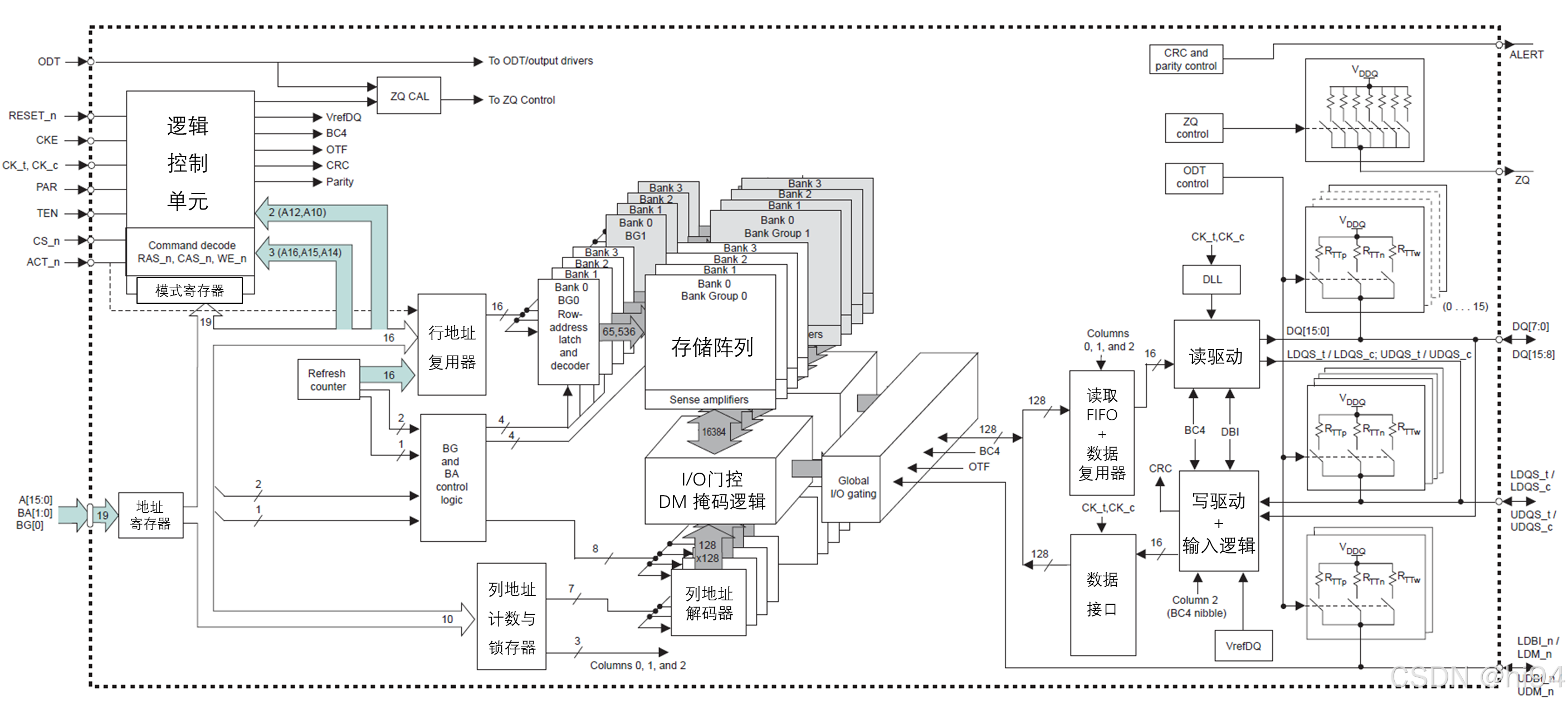

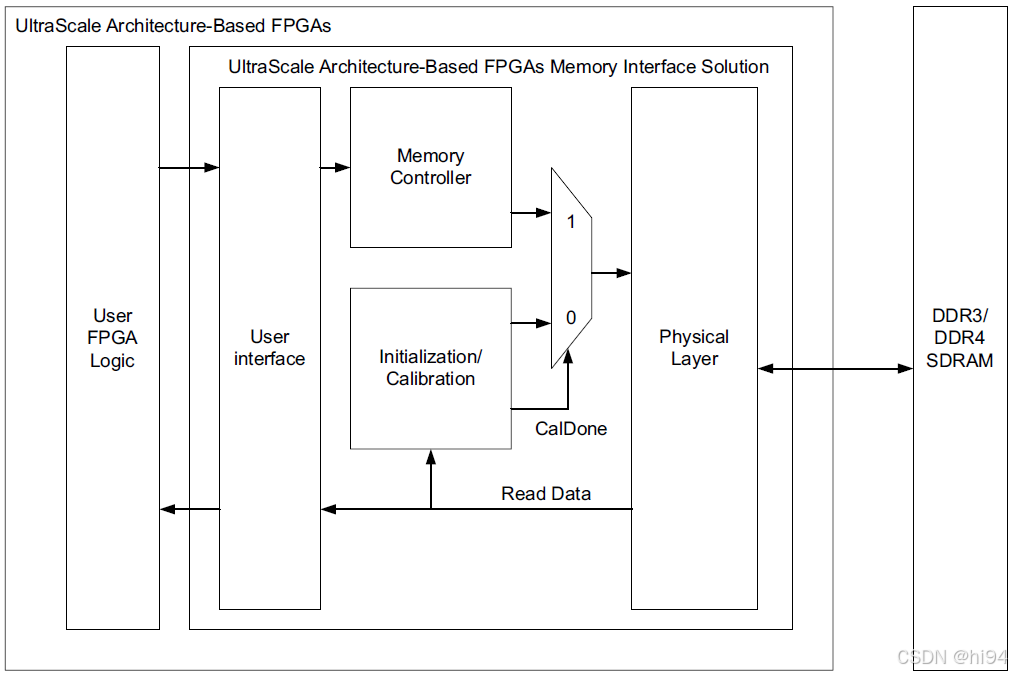

1.5 IP Core 结构

DDR4 IP Core 包含以下三个模块:

1)控制器:控制器接受来自用户接口的突发事务,并生成与 SDRAM 之间的事务。控制器负责处理 SDRAM 的时序参数和刷新操作。它合并写入和读取事务,以减少总线转换过程中涉及的空闲周期数。控制器还会重新排序命令,以提高数据总线到 SDRAM 的利用率。

2)物理层:物理层为 SDRAM 提供高速接口。包括 Hard Blocks 与 Soft Blocks 逻辑,负责所有 SDRAM 事务、时序和刷新。

- Hard Blocks

- 数据序列化和传输

- 数据捕获和反序列化

- 高速时钟生成和同步

- 每个引脚的粗细延迟元素,具有电压和温度跟踪功能

- Soft Blocks

- 内存初始化(Memory Initialization),提供符合 JEDEC 标准的初始化程序。

- 校准(Calibration),校准所有延迟,每个位(Bit)都会单独进行训练,然后组合在一起以确保接口的最佳性能。

3). 应用接口:用户接口层为应用程序提供一个简单的类似FIFO的接口。数据被缓冲,并且读取的数据按照请求顺序呈现。

结构图:

2. 概念解释

2.1 模块(Module)

- DIMM(Dual In-line Memory Module,双列直插内存模块)。区别于早期的 SIMM(Single In-line Memory Module,单列直插内存模块),DIMM 的两侧有独立的电气接触点,能够提供更宽的数据通道(64 位)。

- RDIMM(Registered DIMM,带有寄存器的双列直插内存模块)。寄存器位于 CPU 和 DRAM 芯片之间,用于缓冲数据传输信号,提高了传输效率和稳定性。通常用于需要高稳定性和大容量内存的企业级服务器和高端计算机系统。

- LRDIMM(Load-Reduced DIMM,降低负载的双列直插内存模块)。与 RDIMM 不同,LRDIMM 使用内存缓冲芯片而不是寄存器来减少主板上的电力负载,这允许系统安装更多的内存模块,从而增加总内存容量,同时还能保持较高的数据传输速率。LRDIMM 非常适合需要极大内存容量的应用,如大型数据库、数据分析和高性能计算。

- UDIMM(Unbuffered DIMM,不带缓冲的双列直插内存模块)。UDIMM 直接与系统的内存控制器交互,通常用于台式机和笔记本电脑。由于没有缓冲,UDIMM 的延迟较低,但支持的内存容量较小。

- SODIMM(Small Outline DIMM,小型双列直插内存模块)。主要用于笔记本电脑和其他空间有限的设备。SODIMM 的体积约为常规 DIMM 的一半,但性能和容量与全尺寸 DIMM 相似。

2.2 组件(Component)

组件(Component)指单个 DRAM 芯片,是构成内存模块(如 DIMM)的基本单元。每个组件都有特定的容量和特性,它们共同决定了整个内存模块的性能和容量。以下是一些关键点:

- 容量:组件的容量通常以千兆位(Gb)为单位。例如,一个 8Gb 的 DRAM 组件可以存储 8 千兆位的数据。

- 位宽:组件的位宽决定了每次数据传输的位数。常见的位宽有 x4、x8 和 x16,他们每次传输 4 位、8 位或 16 位数据。

- 组织:组件的组织方式描述了其内部结构,例如 8Gb x8 组件表示这个组件有 8Gb 的容量,每次传输 8 位数据。

- 速度:组件的速度通常以数据传输率(如 3200 MT/s)表示,决定了数据传输的快慢。

- 电压:不同代的 DDR 组件工作在不同的电压下,DDR4 通常工作在 1.2V,而 DDR3 工作在 1.5V。

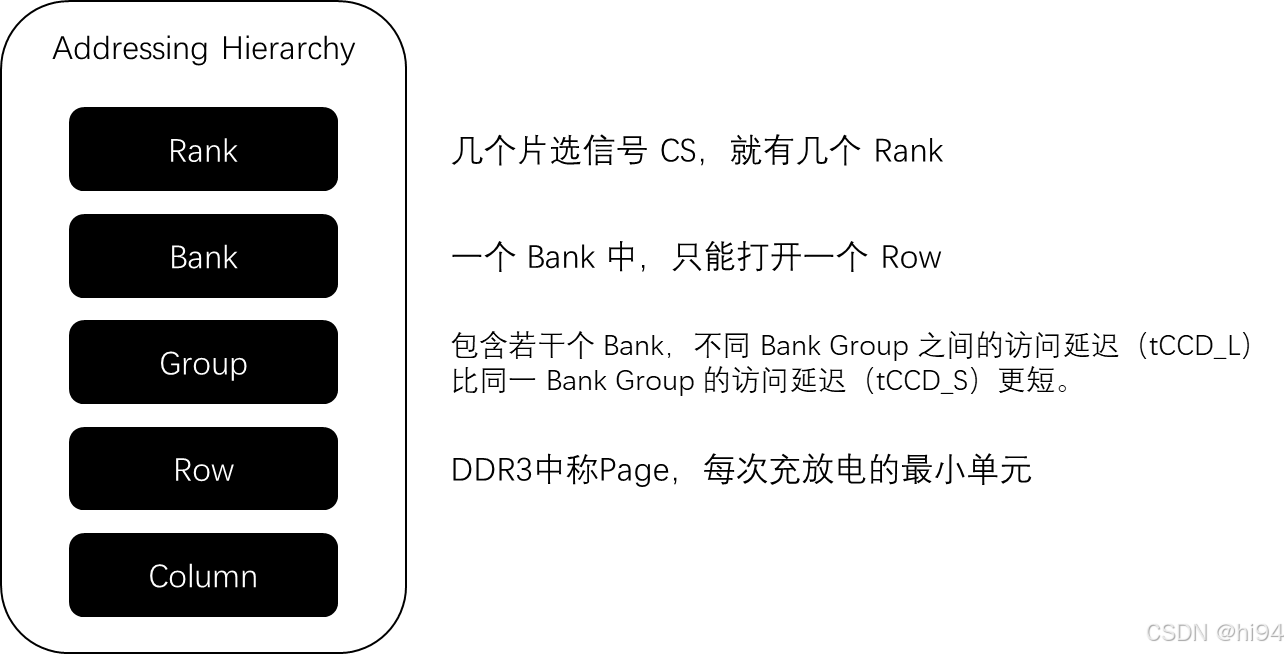

2.3 Rank / Bank / Group...

DDR4 包含五种地址:

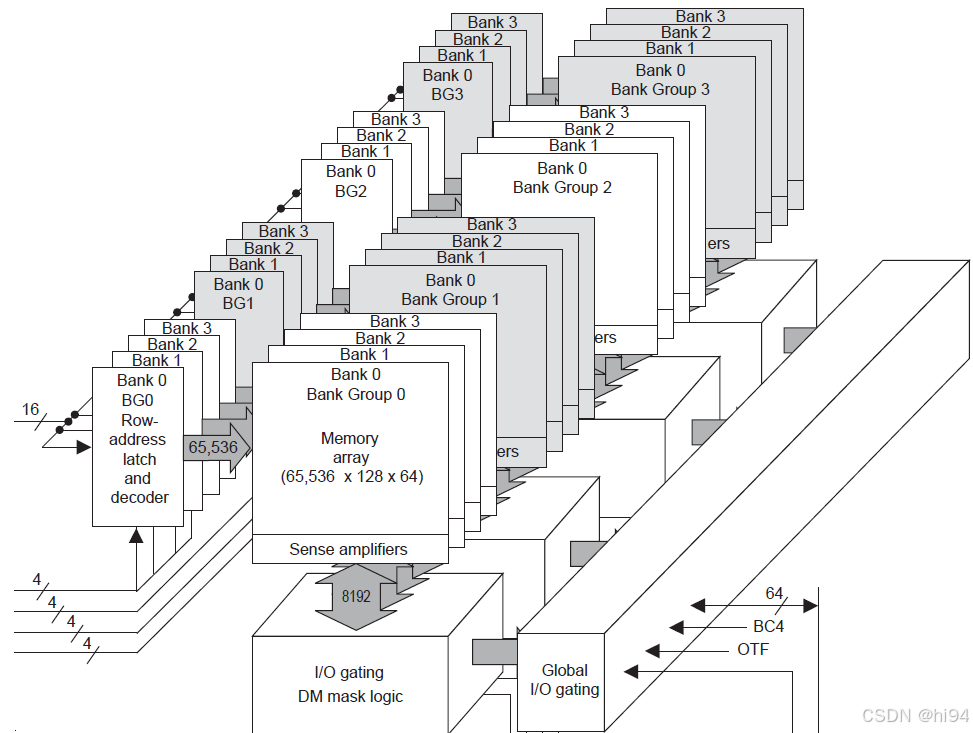

DDR4 框图:

1)Rank

如果控制器数据位宽为 64bits,那么 CPU 每次操作内存数据为 64bits,如果组件是 8bits,那么就需要 8 个组件凑在一起,他们组成一组,称为一个 Rank。此时:

Rank = DDR_8bits * 8chips

简单理解:共享一个片选信号(CS)的一组芯片。

2)Bank

Bank 是指内存芯片内部的一个存储单元块。每个内存芯片可以包含多个 bank,每个 bank 可以独立地进行读写操作。

Bank 的数量通常是固定的,例如 DDR4 内存芯片通常有 8 或者 16 个 Bank。

3)Group

DDR4 中,每个 Bank 被进一步划分为多个 Bank Group。

不同 Bank Group 之间的访问延迟(tCCD_S)(Short)比同一 Bank Group 的访问延迟(tCCD_L)(Long)更短。

Example:2400 Mbps

- tCCD_S = 4x CK

- tCCD_L = 6x CK

- 如果第一次读和第二次读打开的是不同 Bank Group 中 Column,它是需要 4 个CK,一次 burst 是 8 个数据,就是 4 个CK&

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

991

991

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?