折叠式共源共栅放大器设计 cadence

宽摆幅 压摆率 smic180 tsmc180

ID:56300694592127911

老王模拟

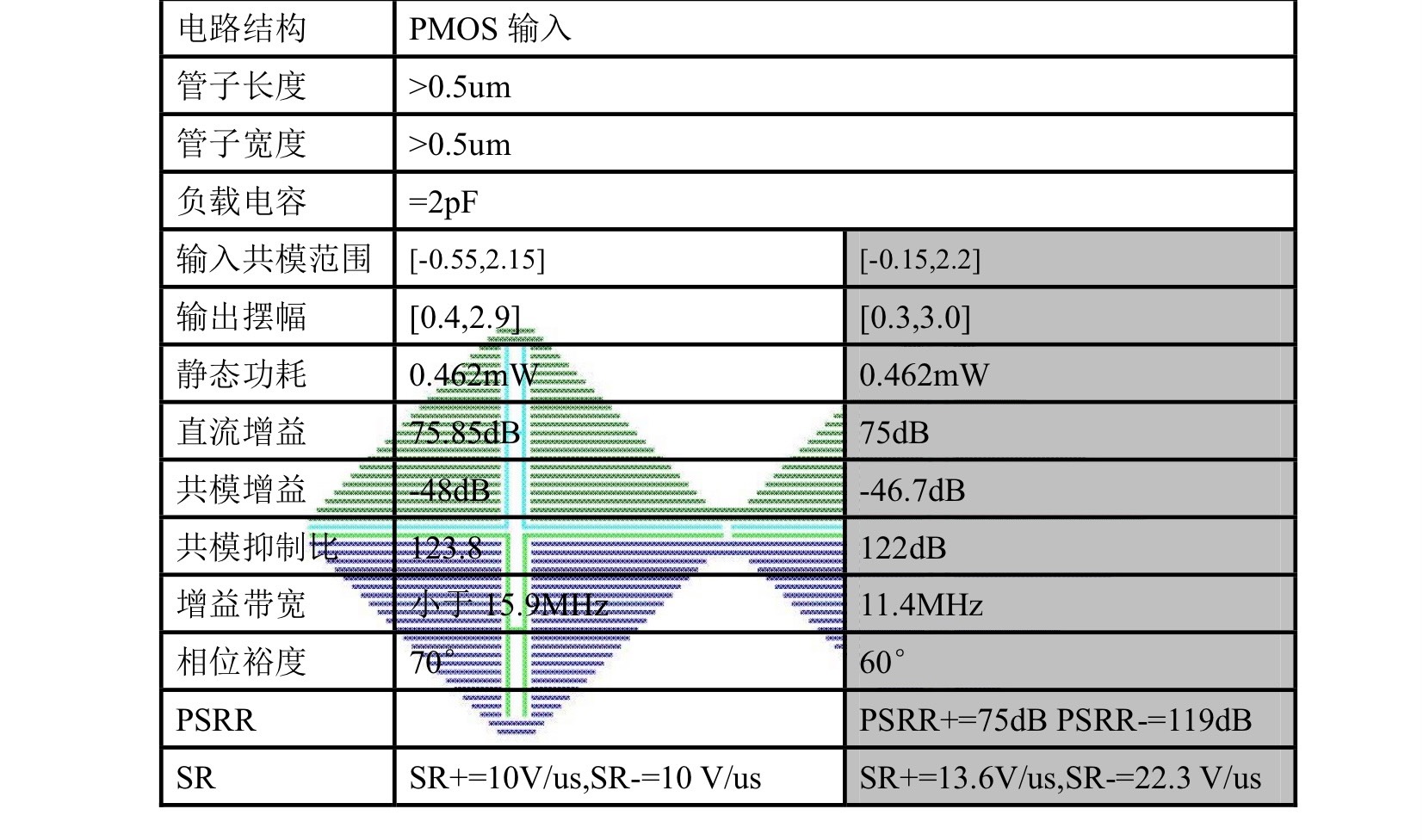

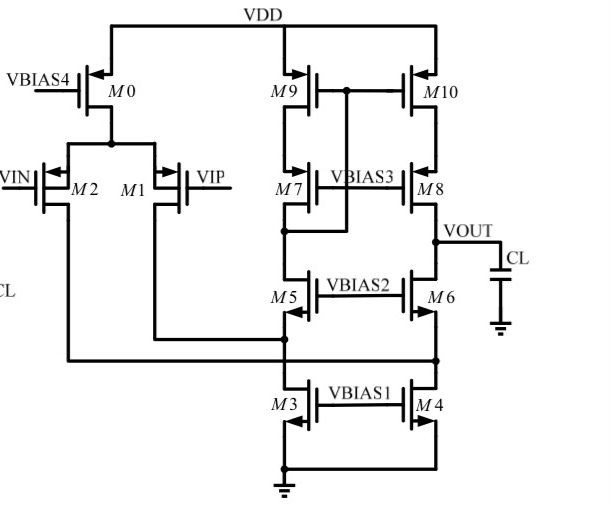

折叠式共源共栅放大器是一种在集成电路中常用的放大器设计方案。它通过使用共源共栅结构,在保证较好的增益和带宽的同时,有效地降低了功耗和噪声。

在放大器设计中,一个关键的指标是增益,即输入信号与输出信号的比值。折叠式共源共栅放大器设计中,通过合理选择设备的尺寸参数以及电流源的配置,可以实现较高的增益。此外,折叠式结构在电路布局中也占据较小的面积,有助于提高集成度。

针对设计过程,CADENCE是一款常用的EDA(Electronic Design Automation)工具,它提供了丰富的模拟和数字电路设计功能,可以有效辅助工程师进行电路设计、仿真和验证。在使用CADENCE进行折叠式共源共栅放大器设计时,我们可以充分利用其强大的功能和丰富的库模型,快速搭建电路原型并进行性能评估。

宽摆幅是指输入信号的幅度范围。在折叠式共源共栅放大器设计中,为了保证较大的动态范围和线性度,我们需要设计合适的电流源和偏置电路,以及合理的电路结构。通过合理调节尺寸和偏压,我们可以实现宽摆幅的特性。

压摆率是指输出信号的上升时间和下降时间。在现代通信系统中,高速数据传输要求电路具备较高的压摆率,以保证信号的快速传输和正确恢复。在折叠式共源共栅放大器设计中,我们可以通过采用高速驱动电路和优化电流源的方式,有效提高压摆率,并满足系统对于高速信号处理的需求。

SMIC180和TSMC180是两个常见的半导体制造工艺。在折叠式共源共栅放大器设计中,合适的工艺选择对于电路性能的影响非常大。根据具体的应用需求和制造成本,我们可以选择适合的工艺,并在设计过程中充分考虑工艺的特性和限制。

综上所述,折叠式共源共栅放大器设计是一种常用的放大器设计方案。通过合理的电路结构选择、CADENCE工具的辅助,以及对于宽摆幅和压摆率的优化,我们可以实现较好的电路性能。同时,对于不同的工艺选择,我们需要充分理解工艺特性,并在设计过程中加以考虑。这样的折叠式共源共栅放大器设计方案,适用于多种应用领域,为集成电路设计提供了一种高效可行的解决方案。

【相关代码,程序地址】:http://fansik.cn/694592127911.html

1490

1490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?