场景1:控制信号有效时,透传输出输入的数据;控制信号无效时,输出数据为0。

普通的写法,当控制信号vld_in无效时,输出数据赋值为0,如下:

module vld_power #(

parameter DWIDTH = 8

)

(

input clk ,

input rst_n ,

input vld_in ,

input [DWIDTH-1:0] data_in ,

output reg [DWIDTH-1:0] data_out

);

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

data_out <= {DWIDTH{1'b0}};

end

else if (vld_in) begin

data_out <= data_in;

end

else begin

data_out <= {DWIDTH{1'b0}};

end

end

endmodule但是,vld_in无效时总是在时钟上升沿对输出赋值,无意中就产生过多的功耗。

可以优化为,在vld_in下降沿输出赋值为0,其它情况下保持,如下:

module vld_power #(

parameter DWIDTH = 8

)

(

input clk ,

input rst_n ,

input vld_in ,

input [DWIDTH-1:0] data_in ,

output reg [DWIDTH-1:0] data_out

);

wire vld_in_neg;

reg vld_in_ff1;

assign vld_in_neg = ~vld_in & vld_in_ff1;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

vld_in_ff1 <= 1'b0;

end

else begin

vld_in_ff1 <= vld_in;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

data_out <= {DWIDTH{1'b0}};

end

else if (vld_in) begin

data_out <= data_in;

end

else if (vld_in_neg) begin

data_out <= {DWIDTH{1'b0}};

end

else;

end

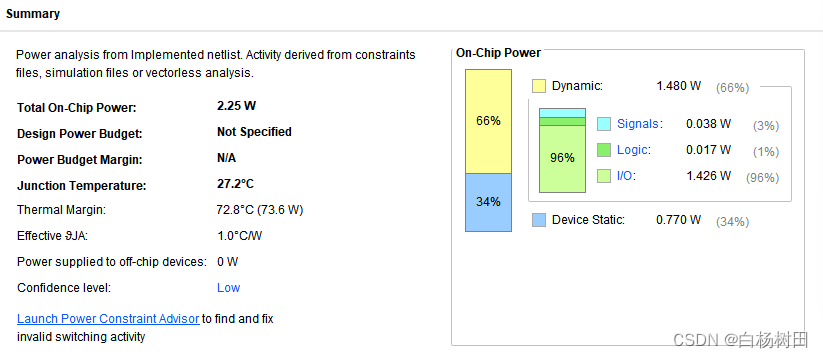

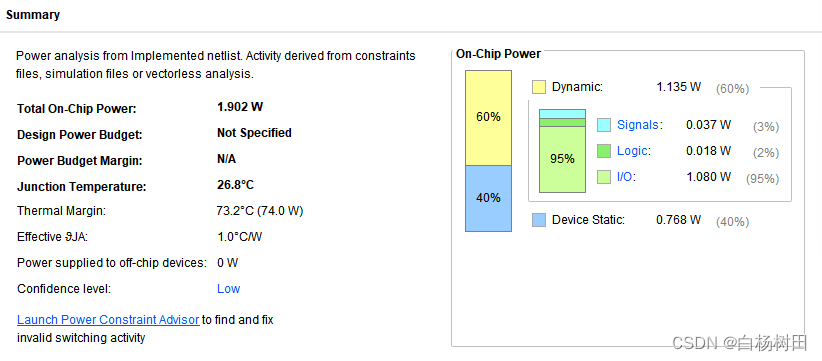

endmodule通过Vivado,二者选取相同的器件,运行后比较二者的功耗报告。

优化后的功耗相比优化前功耗减少0.348W,减少了15%。

468

468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?