二级运算放大器设计

一、实验目的

本次实验的目的是设计和仿真一个两级放大器电路,验证其性能指标,并通过多种仿真手段(如DC、AC、PSRR、CMRR等)全面评估该电路的各项性能。具体目标包括:

-

功耗 < 1.5mA

-

增益 > 60dB

-

GBW > 100MHz

-

相位裕度 > 60度

-

负载电容 10pF

二、实验内容

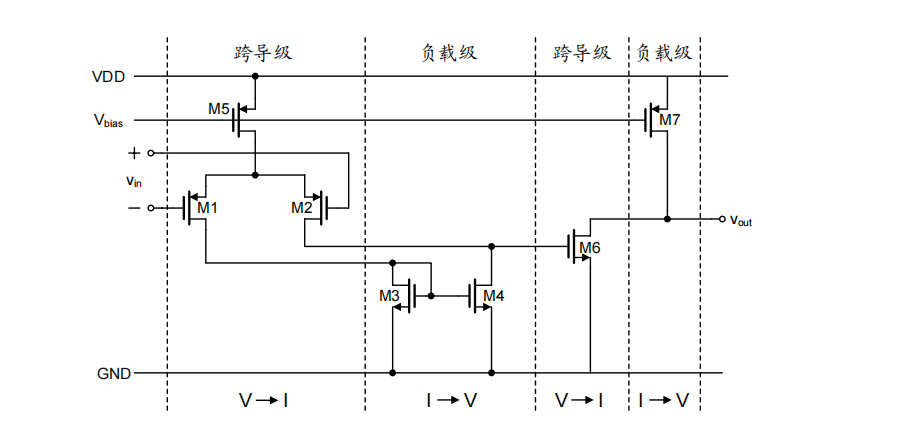

-

搭建两级放大器电路:包括输入级和输出级的设计。

-

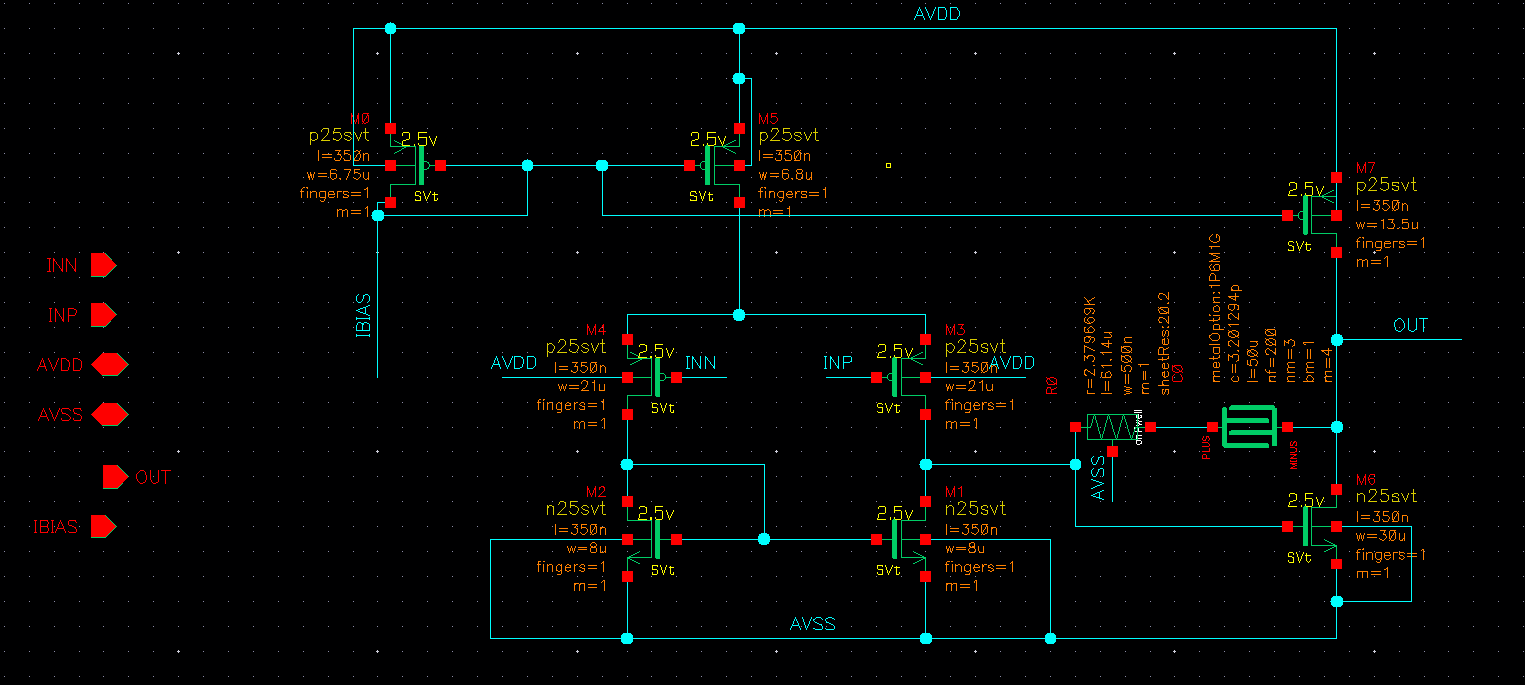

输入级由M1~M5组成,采用PMOS差分输入对和电流镜负载。

-

输出级由M6和M7组成,M6为共源放大器,M7提供偏置电流并作为输出负载。

-

相位补偿电路由M14和Cc构成,形成RC密勒补偿。

-

-

电路分析:从电流与电压转换角度进行分析,将运放层次结构分为跨导级和负载级。

三、实验步骤及结果

-

搭建电路原理图

- 创建symbol并搭建仿真TB电路。

二级放大电路搭建

| 器件编号 | 器件类型 | 长(nm) | 宽(um) | 栅指数 | 乘积数 |

|---|---|---|---|---|---|

| M0 | p25svt | 320 | 6.75 | 1 | 1 |

| M1 | n25svt | 350 | 8 | 1 | 1 |

| M2 | n25svt | 350 | 8 | 1 | 1 |

| M3 | p25svt | 350 | 21 | 1 | 1 |

| M4 | p25svt | 350 | 21 | 1 | 1 |

| M5 | p25svt | 320 | 6.8 | 1 | 1 |

| M6 | n25svt | 350 | 30 | 1 | 1 |

| M7 | p25svt | 320 | 13.5 | 1 | 1 |

| 器件编号 | 器件类型 | 数值 |

|---|---|---|

| R0 | p25svt | 2.379KΩ |

| C0 | p25svt | 3.2pF |

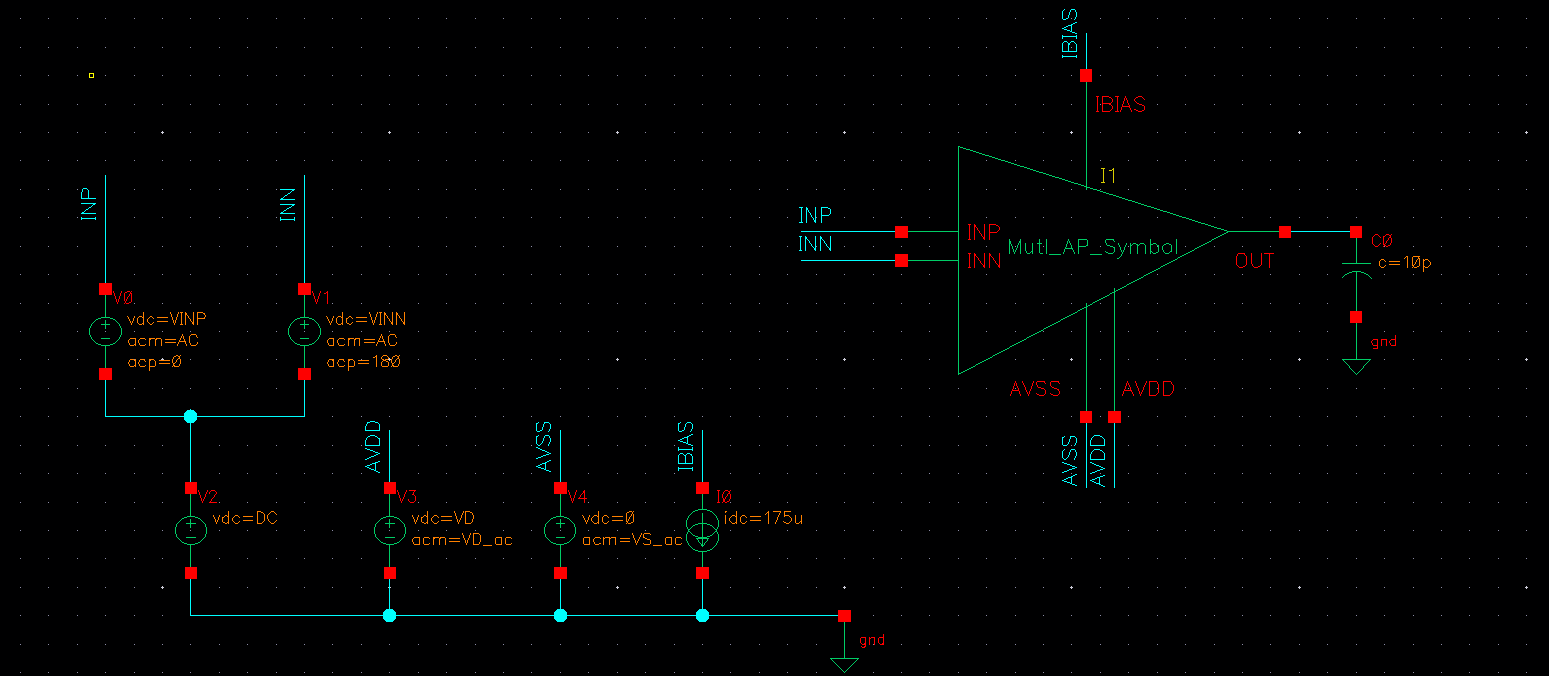

仿真测试电路

| 编号 | 信号标签 | 说明 |

|---|---|---|

| V0 | INP | 差分正向输入 |

| V1 | INN | 差分反向输入 |

| V2 | VDC | 直流偏置源 |

| V3 | AVDD | 电源电压 |

| v4 | AVSS | 地 |

| I0 | IBIAS | 电流偏置 |

-

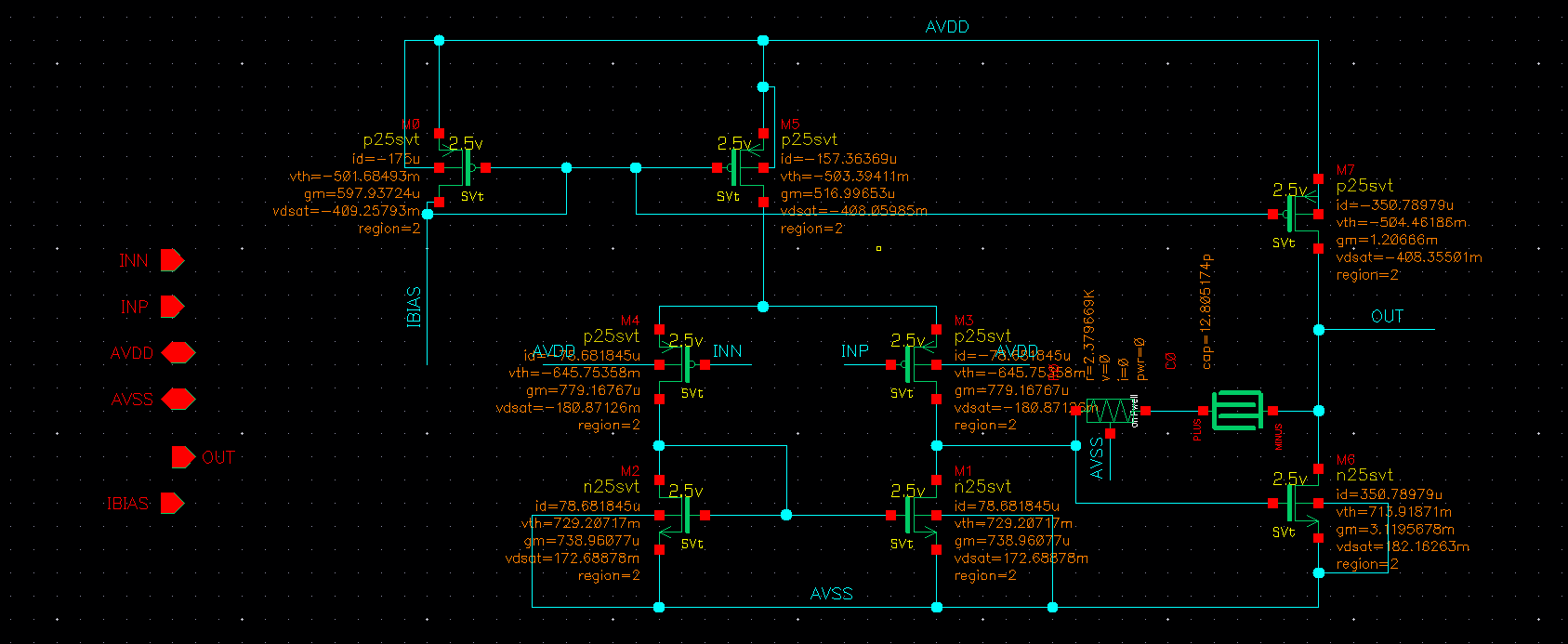

DC仿真

- 确定直流工作点,设置条件并运行仿真。

直流工作点的确定

| 信号 | 直流工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 1.25V |

| IBIAS | 175uA |

由图可知,所有器件的都工作在饱和区,静态直流电流等于682uA, 直流功耗 1.705mW

-

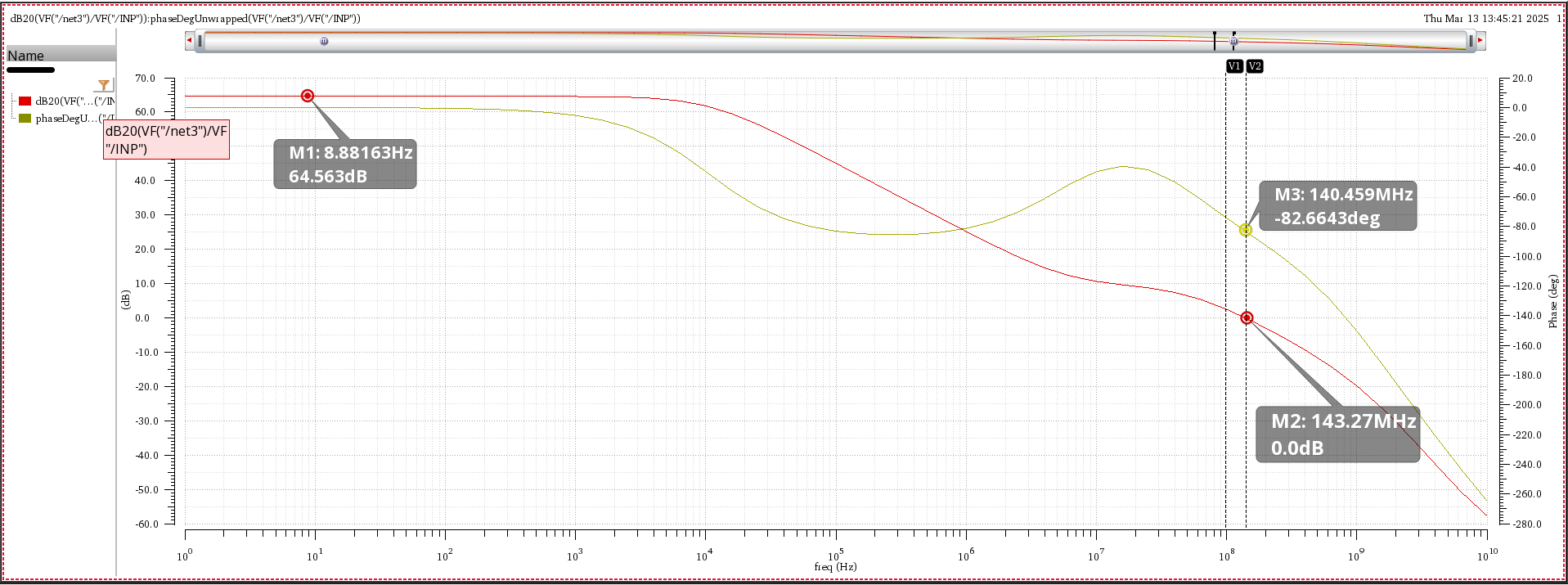

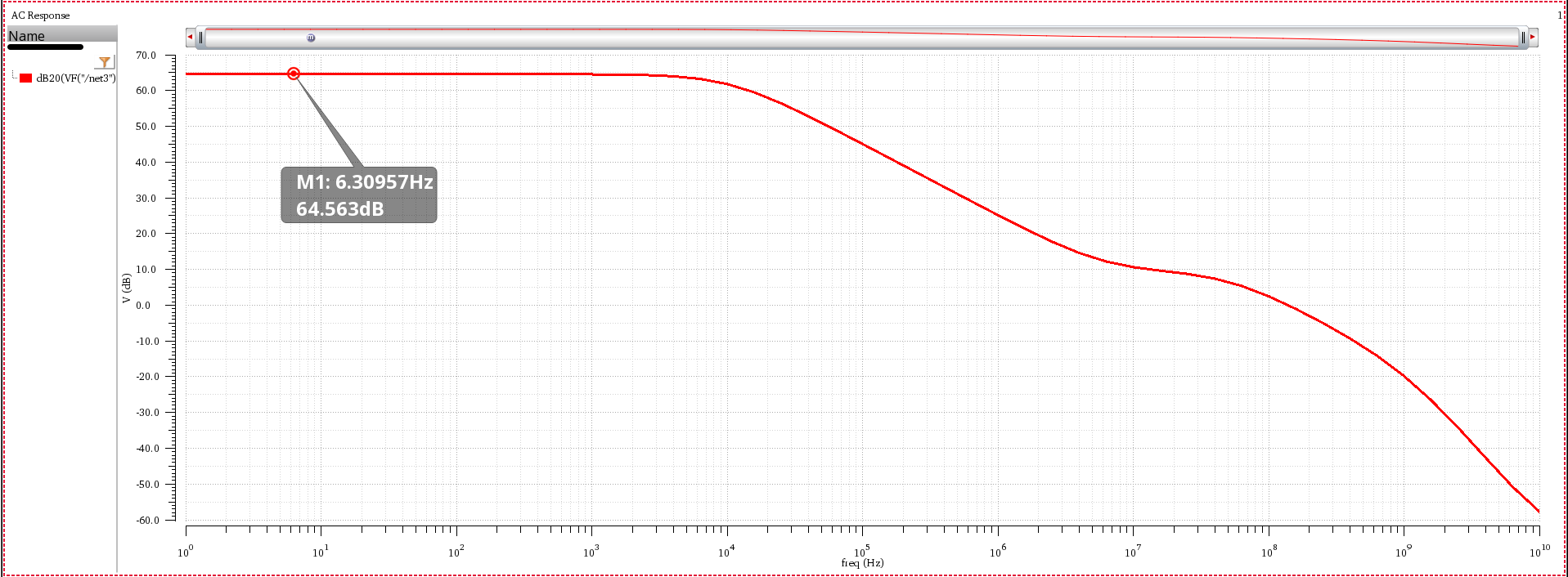

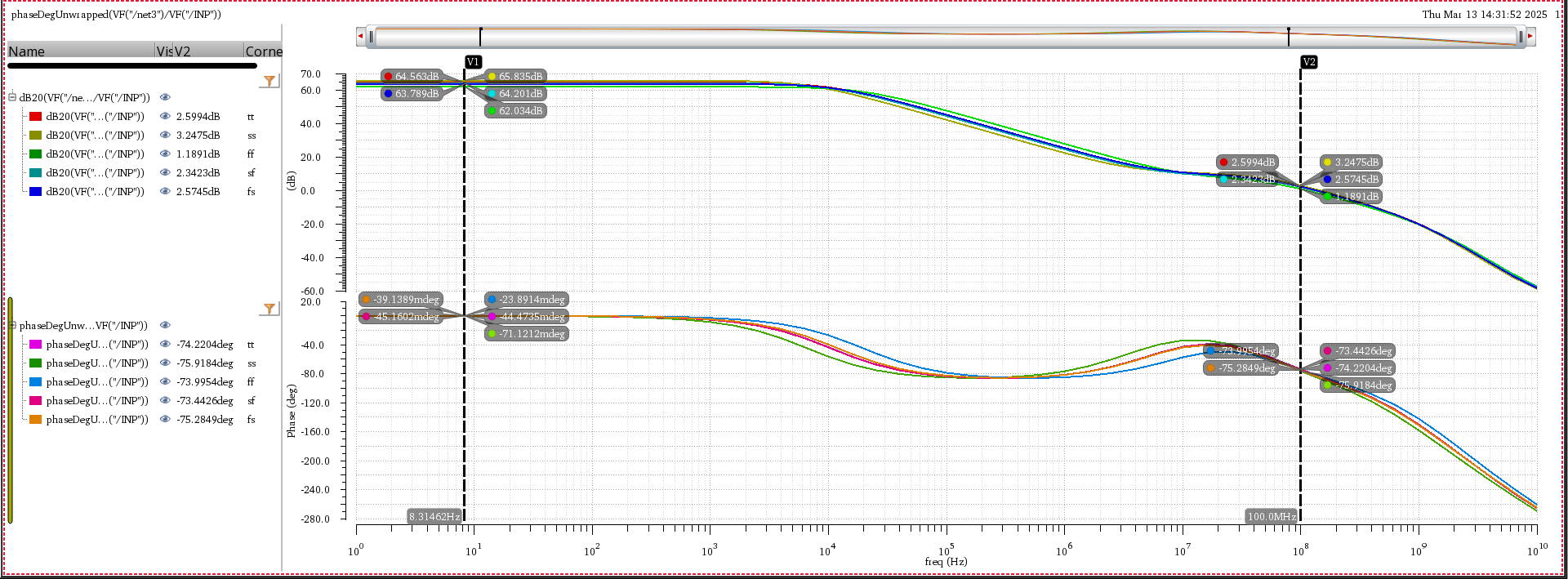

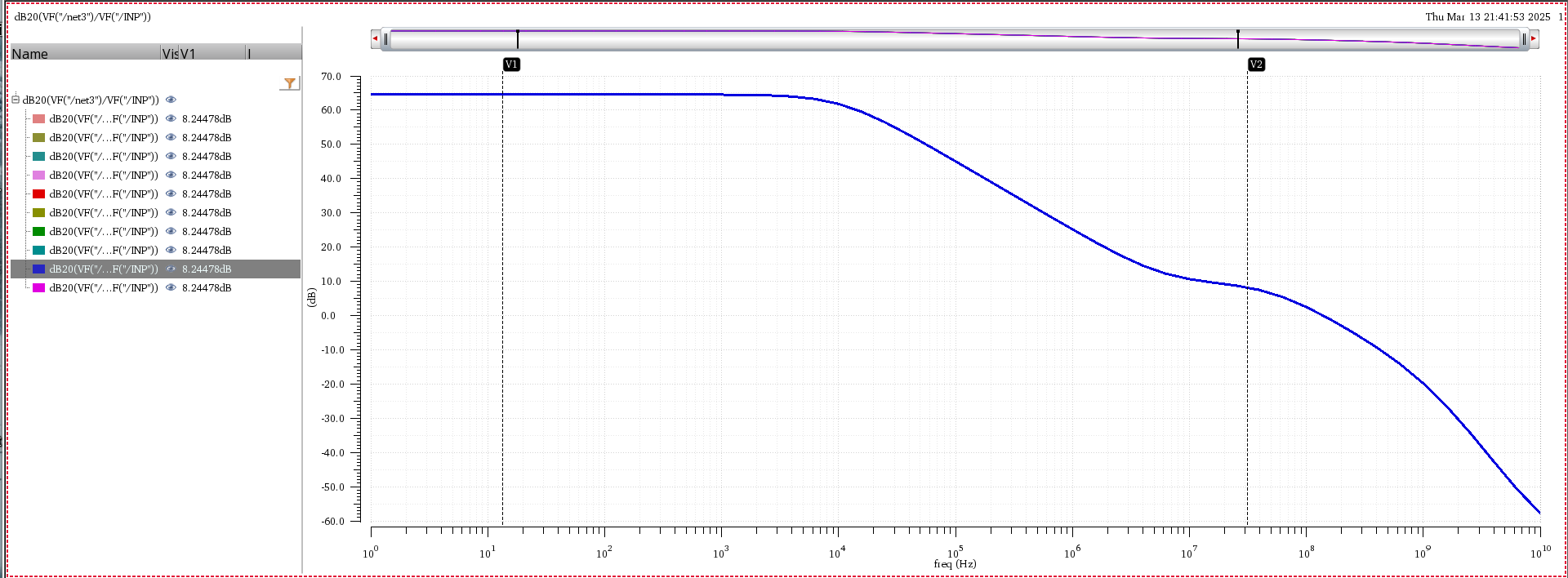

AC仿真

- 设置条件,仿真得到增益、GBW和相位裕度

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 1.25V |

| IBIAS | 175uA |

| AC | 1V |

- 结果:增益约为64.563dB,GBW为143MHz,相位裕为82,均度满足要求。

-

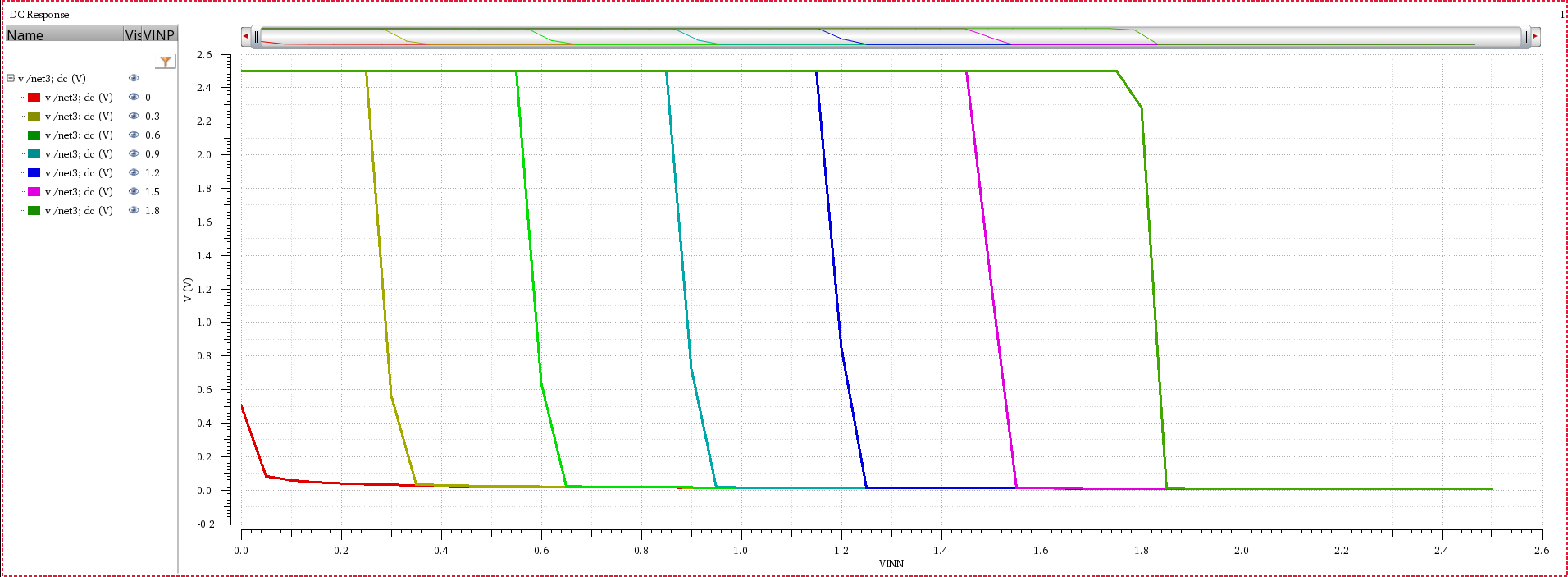

输入输出范围仿真

- 设置仿真参数,运行仿真并记录输出结果。

输入输出范围图

工作条件

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 0 |

| IBIAS | 175uA |

| AC | 0V |

输出信号变化范围

| 信号 | 工作条件 |

|---|---|

| INP | 0V~1.8V |

| INN | 0V~2.5V |

-

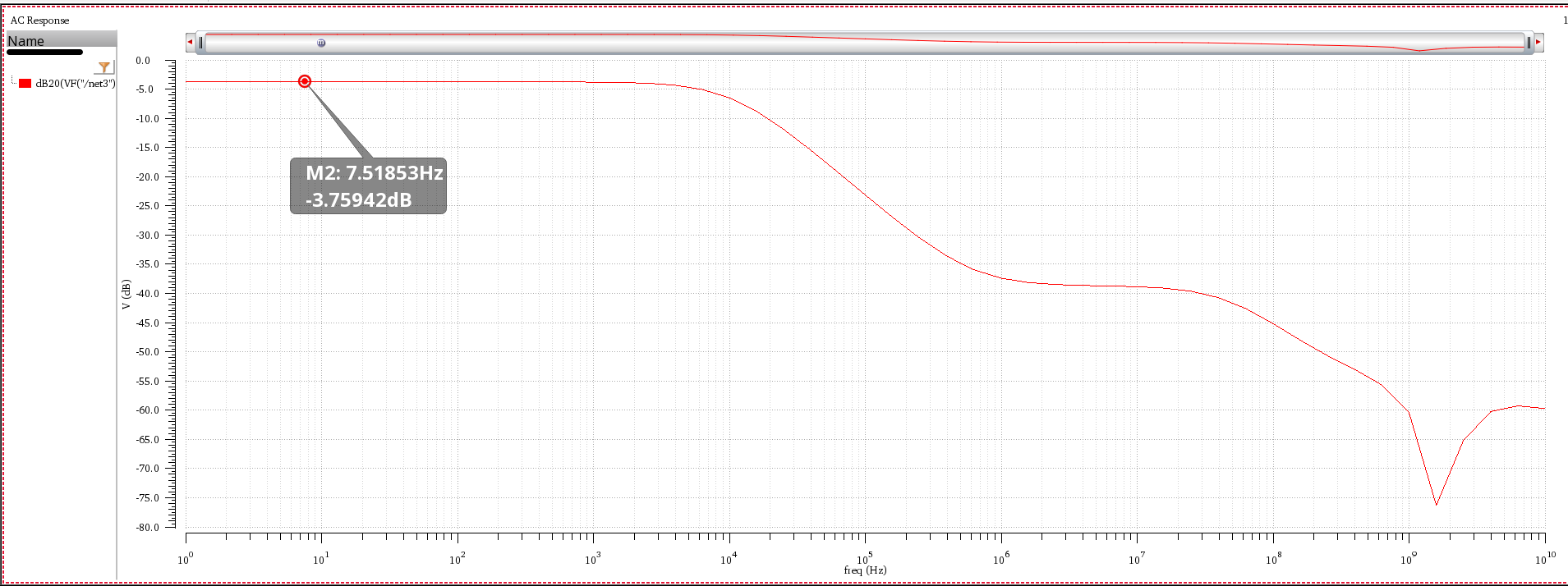

电源抑制比(PSRR)仿真

- 计算公式:PSRR = 差模增益 / 电源增益。

差模增益

工作条件

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 0 |

| IBIAS | 175uA |

| AC | 1V |

| VD_ac | 0V |

电源增益

工作条件

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 0 |

| IBIAS | 175uA |

| AC | 0V |

| VD_ac | 1V |

- 结果:PSRR = 64.563dB - (-3.7594)dB = 68.3324dB。

-

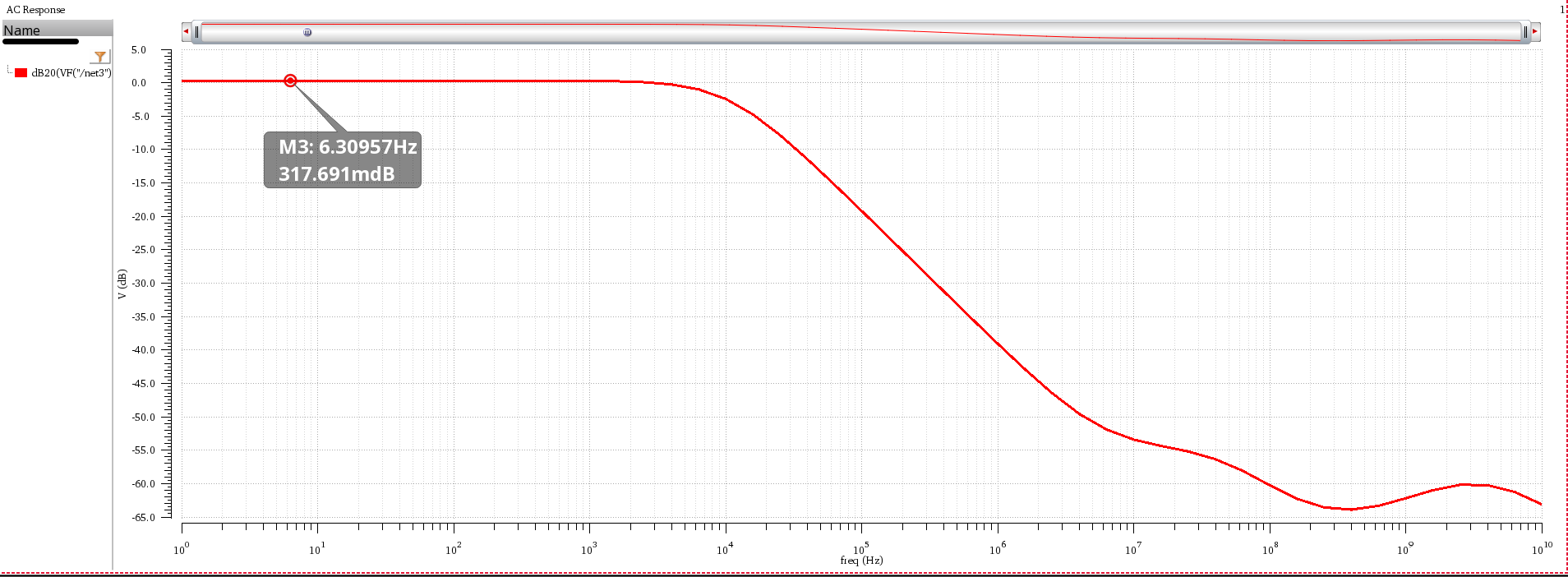

共模抑制比(CMRR)仿真

- 计算公式:CMRR = 差模增益 / 共模增益。

共模增益

工作条件

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 0 |

| IBIAS | 175uA |

| AC | 1V |

| VD_ac | 0V |

注意在测量共模增益时,VINN和VINP的相位需要一致

- 结果:CMRR = 64.563dB - 0.317dB = 64.246dB。

-

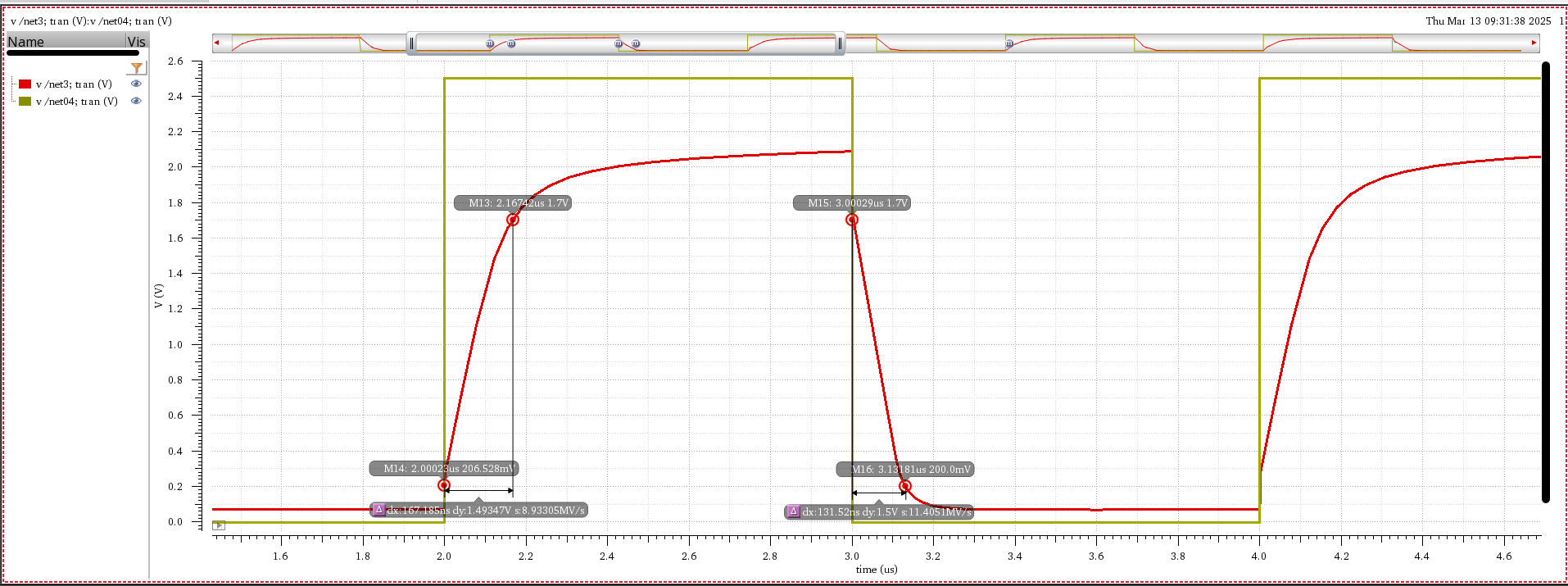

压摆率(Slew Rate)仿真

- 接成单位负反馈形式,施加阶跃信号。

压摆率的测量

- 结果:上升沿压摆率为8.93MV/s,下降沿压摆率为11.405MV/s。

-

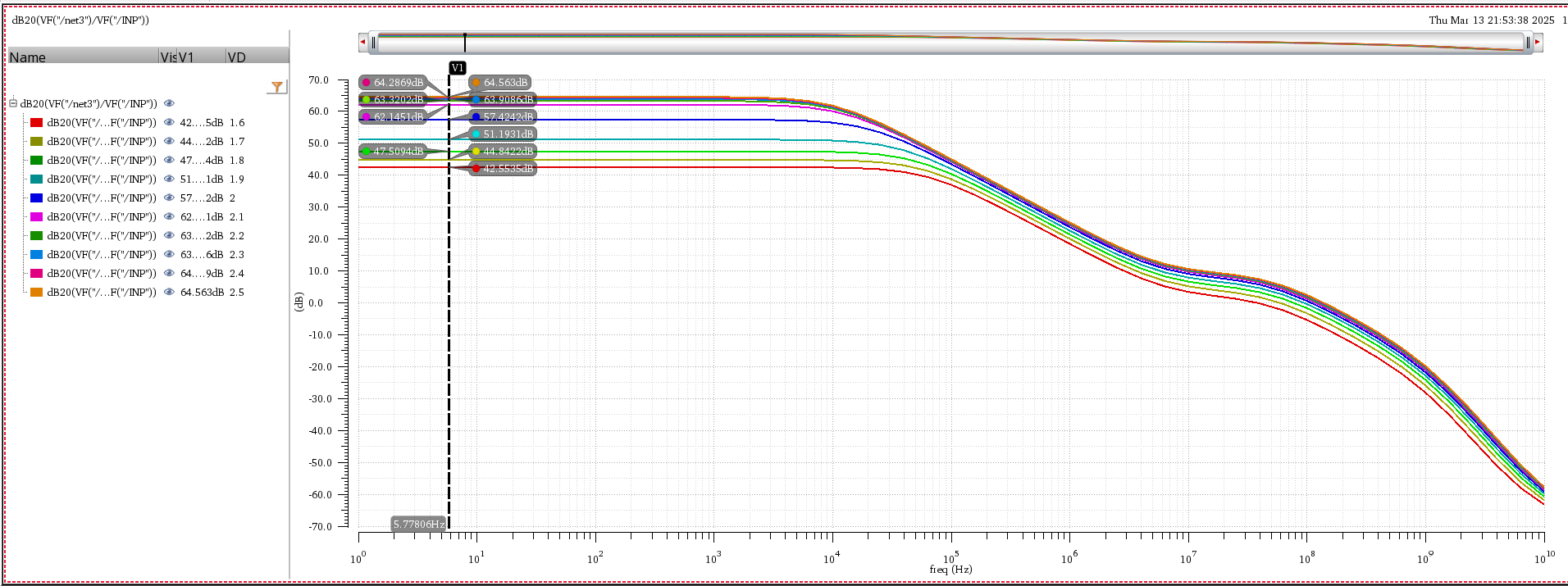

工艺角仿真

- 配置工艺角文件,进行仿真并绘图。

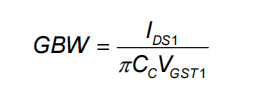

不同工艺角下,ac仿真结果

工作条件

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 1.25V |

| IBIAS | 175uA |

| AC | 1V |

结果

| 工艺角 | 低频增益(dB) | GBW(Hz) | 相位裕度(deg) |

|---|---|---|---|

| tt | 64.563 | 143.27 | -84.524 |

| ss | 65.835 | 152.74 | -86.698 |

| ff | 62.034 | 120.143 | -77.699 |

| fs | 63.789 | 142.356 | -83.932 |

| sf | 64.201 | 139.336 | -81.754 |

在ss工艺角下,该双级电路增益最大,单位增益带宽最大,相位裕度充裕

四、问题及思考

- 各个性能指标之间的约束:各个性能指标之间存在什么样的约束?

原电路图如下

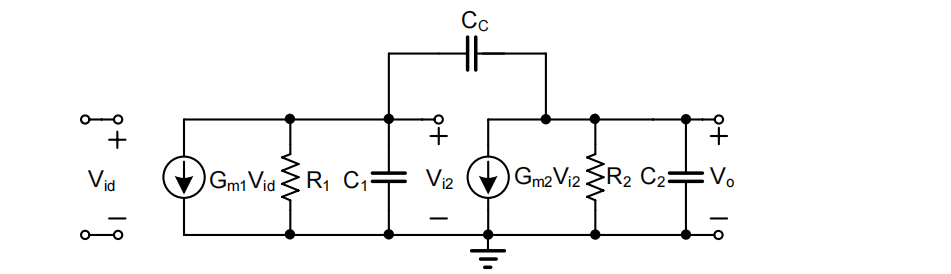

该两级运放电路的等效电路如下

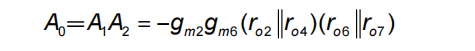

第一级差分输入对管M1与M2相同,有

Gm1=gm1=gm2

R1=ro2||ro4

A1=Gm1R1= gm1(ro2||ro4)

对第二级有

Gm2=gm6=2Ids6/Vgst6

R2= ro6||ro7

A2=-Gm2R2=-gm6(ro6||ro7)

总增益为

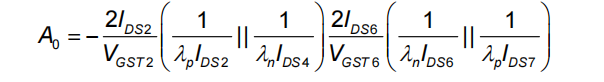

采用一阶模型有

最终得到

++M1管和M6管的过驱电压越小(跨导越大), M2, M4, M6, M7的沟道长度愈大(电阻越大)++

++增益越大++

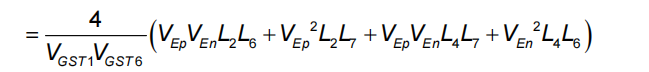

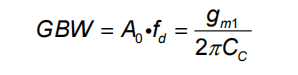

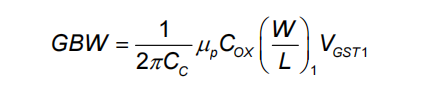

单位增益带宽

可以写成

和

可以看出(第二个式子),如果减小过驱电压以及增大沟道长度来提高增益,那么GBW会减小,也即

++增益与单位增益带宽相互制约++

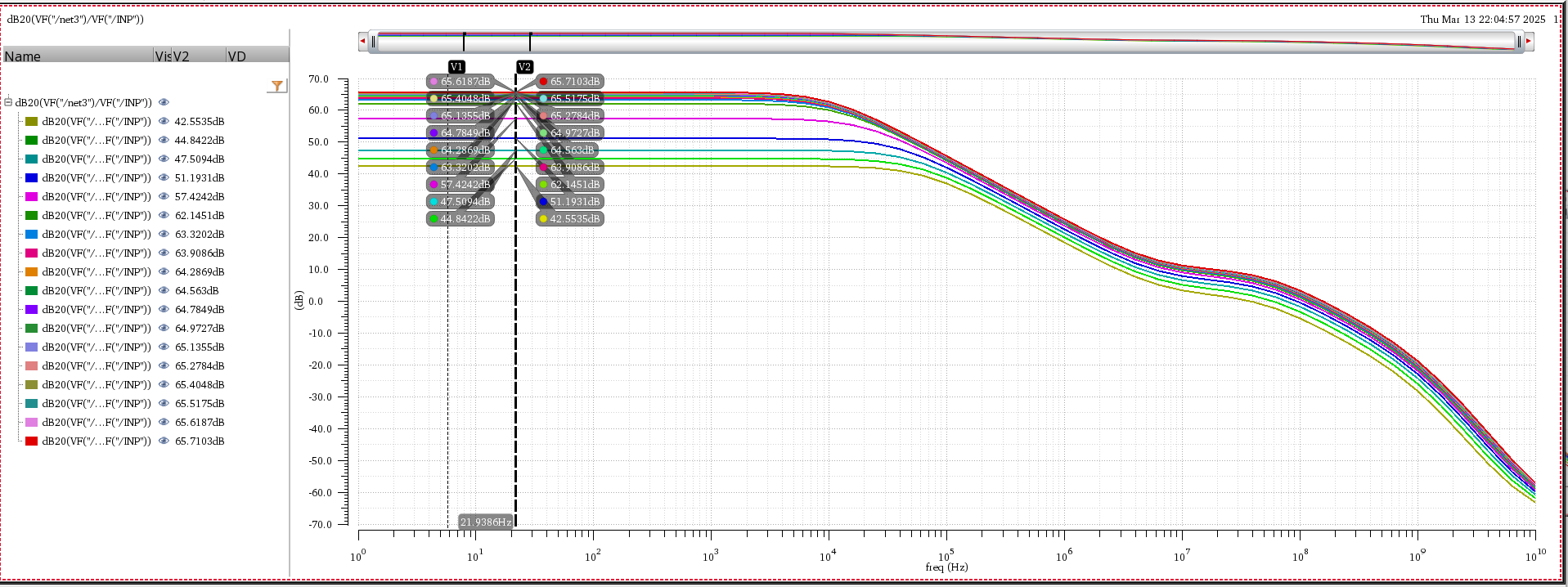

改变L对电路的ac仿真影响

结果

| 沟道长度(nm) | 低频增益(dB) | GBW(MHz) |

|---|---|---|

| 270 | 50.9186 | 177.05 |

| 290 | 55.3571 | 172.5 |

| 310 | 59.0786 | 163.23 |

| 330 | 62.137 | 153.19 |

| 350 | 64.563 | 143.27 |

| 370 | 65.874 | 131.205 |

| 390 | 66.879 | 119.648 |

可以看出器件的沟道越长,交流低频增益越大,GBW越小

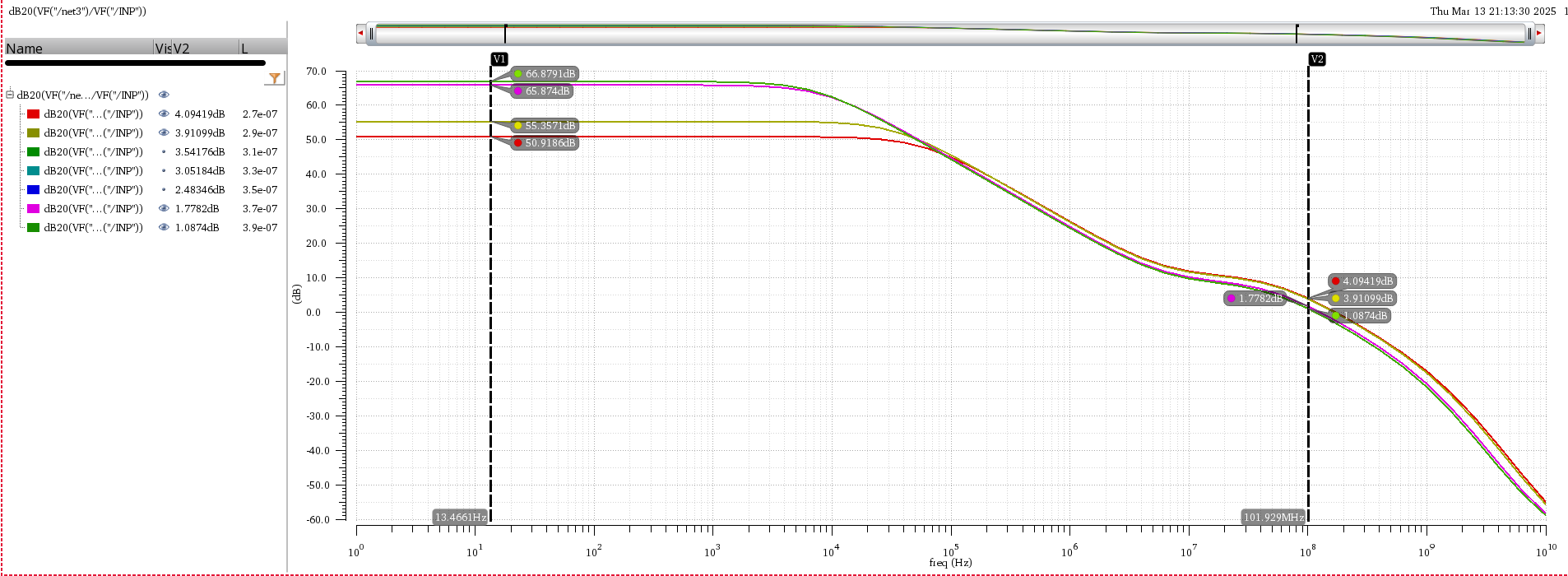

- 相位裕度的影响:在设计中如何确保相位裕度足够大以避免振荡?

要避免振荡,我们需要确保当电路的增益幅值为1时,还有足够的相位裕度。这就需要我们

-

将零点移到左半平面并与第二极点重合,可以消去第二极点,使补偿后的运放只有一个极点

-

消去零点。即将零点移至无穷远处

-

将零点移到左半平面略大于 GBW 的位置。要求60的相位裕度,那么需要将零点移动到2.2GBW处,这就要求

我们此处采用的就是这种方法,通道调节Rz和Cc,可以实现要求相位裕度

-

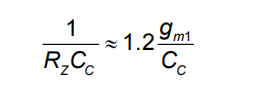

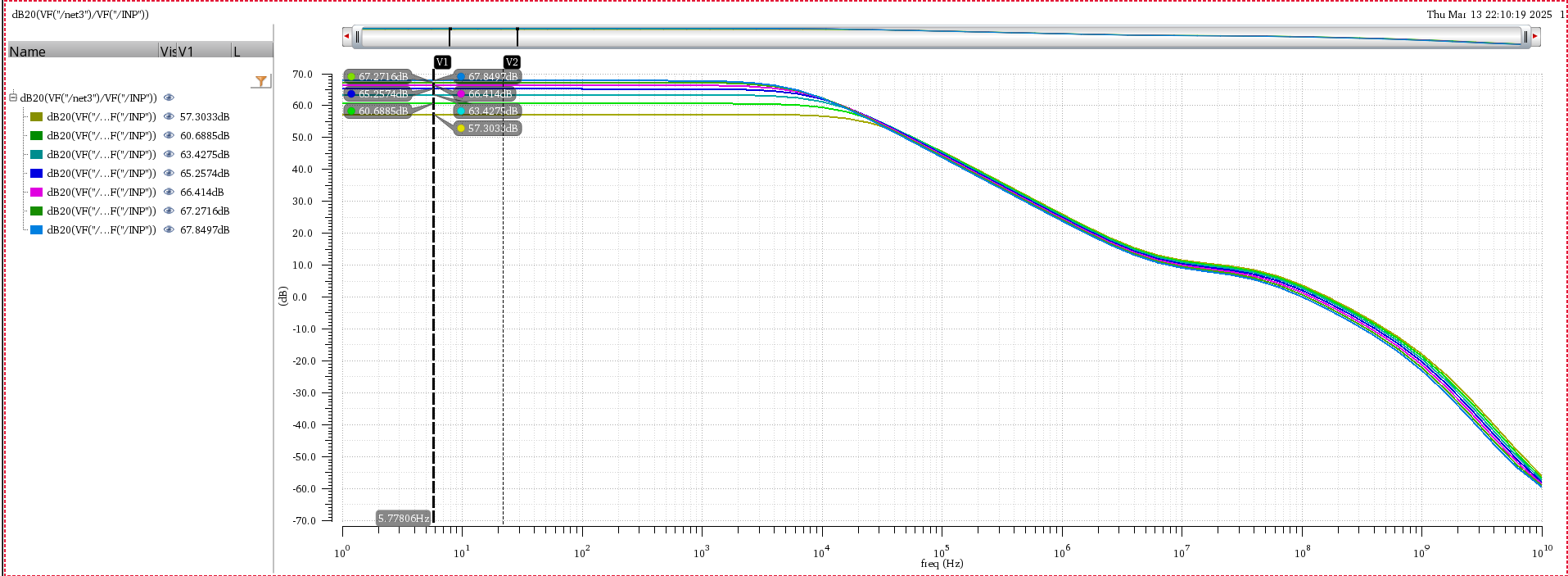

功耗优化:如何在保证其他基础上,进一步降低功耗?

-

偏置电流

在一定的范围内修改偏置电流,确保器件均工作饱和区,这样的情况下,可以在性能大致不变的的情况下,降低功耗

不同偏置电流下,器件的交流增益

由上图可以看出,偏置电流不一致,但是所有交流仿真曲线是重合的,在增益大致不变的情况下,降低了功耗。

但是需要注意的时,实际上直流电流分量对交流仿真是没有影响的,因而上述的图像是比较理想的,实际情况下,直流偏置电流的值应该会影响交流增益以及带宽的。

- 改变工作电压

在很小的范围内,改变电压可以满足基本增益的同时,降低功耗

VDD值对ac性能指标的影响

需要注意的是,降低电压对交流性能指标的趋势方向是一致的,它会拉低增益,同时降低单位增益带宽,此外,电路对电压的变化是非常敏感的,因而不推荐采用此方法。

-

如何进一步提高增益:如何进一步提高增益?

-

提高电压

增大电压对增益的影响

可以看出,提高电压的值能提高电路的增益,当器件不能尚未全部进入饱和状态时尤其明显(VDD从1.6V~2.1V);但是继续增加电压,尽管可以提升增益,但是效果微弱,此外还会增大电路功耗,在电路设计时,需要好好权衡

- 增大器件长度

增大器件长度对交流增益的影响

提高器件的长度,可以增大器件的输出电阻,从而提高增益;但是随着沟道长度的增加到一定范围后,在相同的直流偏置下,晶体管的过驱电压会上升,从而部分抵消了沟道增加而带来的增益的变化;此外增加沟道长度,会增大电路的寄生电容,会影响器件的开关速率,因而在设计时需要谨慎考虑

- 降低器件宽度

降低器件的宽度,和增大器件沟道长度的逻辑是一致的,这里也需要考虑增大虑寄生电容的可能

- 并联晶体管

可以在改变晶体管宽度的同时,通过调节multiply 和finger的数目,有可能提升增益,但是会增大寄生电容,因而也需要好好考虑。

五、总结

通过本次实验,我们成功设计并仿真了一个两级放大器电路,验证了其各项性能指标均达到了预期要求。特别是通过详细的DC、AC、PSRR、CMRR和Slew Rate仿真,全面评估了电路的稳定性和可靠性。此外,通过对工艺角的仿真,进一步了解了不同工艺条件下电路性能的变化。这些实验结果为后续的实际应用提供了重要的参考依据。

8738

8738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?