嵌入式系统的VGA接口设计 (包含各种VGA接口的设计)

目前越来越多的嵌入式处理器上集成了LCD控制器。典型的如三星的S3C2410A,Intel的Xscale系列。这样可方便地外接大屏幕的 LCD,且分辨率也能达到640×480,甚至800×600;色深能从6.5万色(16位)到26万色(18位)。但是大屏幕LCD的价格都比较昂贵。另一方面,普通计算机的VGA接口显示器,保有量巨大、技术成熟,如果能通过接口转换手段,让嵌入式处理器直接支持VGA显示器,则能很大地利用现有资源,节约系统成本。

LCD接口转换为VGA接口

VGA (Video Graphics Array)接口信号为模拟信号。其关键信号有5个,分别是Horizontal Sync水平同步信号(也叫行同步信号),垂直同步信号Vertical Sync(也叫场同步信号),Red红色,Green 绿色和Blue 蓝色。电子枪从左至右,从上至下地进行扫描,每行结束时,用行同步信号进行同步;扫描完所有行后用场同步信号进行场同步。因电子枪偏转需要时间,所以扫完回转中,要对电子枪进行消隐控制:在每行结束后的回转过程中进行行消隐;在每场结束后的回转过程中进行场消隐。消隐过程中不发送电子束。

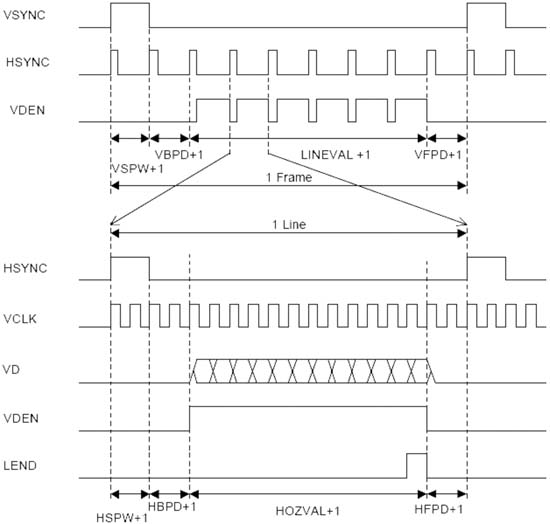

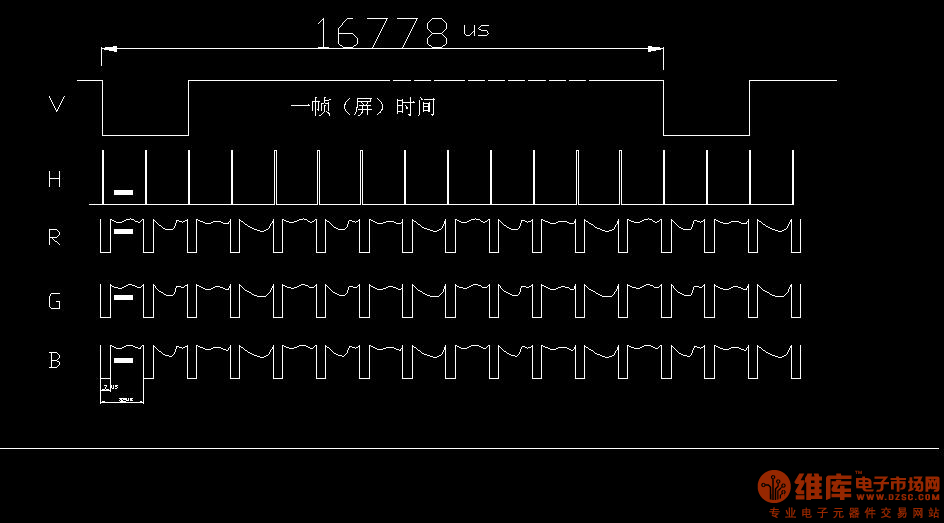

扫描式LCD接口(以S3C2410A的LCD控制器为例图1),在每一场完毕后,也是用VSYNC来进行场同步;每一行完毕后,也是用HSYNC进行行同步;也有VCLK像素时钟,用于锁存数据;

其场同步信号,宽度为(VSPW+1),之前有场消隐前肩(VFPD+1),之后有场消隐后肩(VBPD+1);

其行同步信号,宽度为(HSPW+1),之前有行消隐前肩(HFPD+1),之后有场消隐后肩(HBPD+1);

可以发现,扫描式LCD接口的同步信号时序和VGA接口是一致的。原因是发明LCD后,尽管显示原理不同,但为了在时序上和CRT兼容,也采用了这样的控制时序。基于此,完全能将LCD接口转换为VGA接口。

图1 三星S3C2410A的LCD信号时序图(来自S3C2410A数据手册)

方案实现

VGA接口只需Hsync和Vsync两个同步信号和RGB三个色彩分量信号。而扫描式LCD接口的同步信号的时序和VGA接口的完全一致,可直接把两个同步信号接入VGA接口。

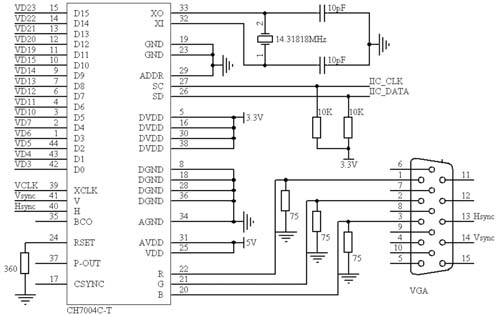

S3C2410A的LCD控制器输出的是RGB数字信号。因此若用一些DAC芯片把RGB数字信号转换为模拟信号,即可实现VGA接口的RGB 信号输入。这类视频专用DAC芯片较多,例如ADI公司的ADV7120;CHRONTEL公司的CH7004C。实验中选用的CHRONTEL公司的 CH7004C。S3C2410A的LCD控制器与CH7004C的连接如表1。

表1 S3C2410A的LCD控制器与CH7004C的连接

在选择数据格式时,RGB565较合适,因为16位数据已经有6.5万色,完全足够;24位数据时每个像素实际占用32位,4个字节,传输时对S3C2410A的总线资源占用太大。

整个电路原理图如图2所示。其中一些需要注意的地方有:

CH7004C工作在从模式下,由S3C2410A的I2C控制。在实验中使用的是精度较好的日本村田(murata)的阻容元件,包括 10K,360欧,75欧和10pF的电容。10K用于I2C总线的上拉,360欧用于RSET引脚接地;75欧为R,G,B三个输出管脚和地之间的终端电阻,10pF电容用于晶振。另外,CH7004C的IIC地址,是通过把ADDR引脚拉高或拉低来设定;接地时,根据芯片手册,其7位的I2C地址为 1110110,最后加一个读/写位。

图2 CH7004C的电路原理图

CH7004C的关键寄存器及设置

CH7004C片内有25个寄存器。其中比较关键的是Display Mode,Input Data Format,Sync Polarity三个寄存器。Display Mode显示模式寄存器,片内地址0X00,输入分辨率为640×480,由芯片手册,可选模式从Mode13到Mode17均可。实验中选择的是默认的 Mode17,对应参数为0X6A。Input Data Format输入数据格式寄存器,片内地址是0X04,因为输入的数据格式为RGB565,且需打开pass-through模式,故对应参数为 0X20。Sync Polarity同步信号极性寄存器,片内地址0X0D,根据输入的Hsync和Vsync的极性来设定,如果是均为负脉冲,则把VSP位和HSP位都置 0;如果均为正脉冲,则把VSP位和HSP位都设置为1。实验中,把S3C2410A的LCD控制器的同步信号极性均设为低电平有效,故参数为0X00。

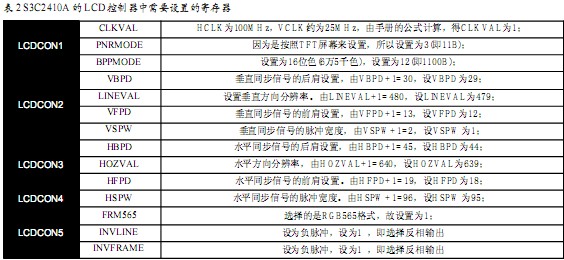

S3C2410A的LCD控制器设置

作为输出源,S3C2410A的LCD控制器也需要进行相应设置。需要的输出分辨率是640×480,16位色(RGB565格式),刷新率 60Hz。一共有LCDCON1到LCDCON5共5个寄存器需要设置,具体参数要参考VGA时序规范和LCD时序图(图1)。所需设置的寄存器如表2。

表2 S3C2410A的LCD控制器中需要设置的寄存器

实验及数据

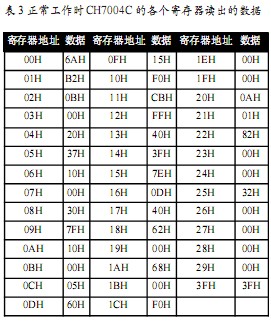

实验中,选择的操作系统嵌入式Linux,内核版本2.4.18,图形系统是Qtopia 1.7.0。bootloader选用的韩国MIZI公司的vivi。上电后,vivi将进行初始化,其中包括设置CH7004,然后再引导进入 Linux。对CH7004的操作,完全可以看作对一个IIC接口的EEPROM来进行,可专门定义一个函数IIC_Write()来写数据。例如对 IDF寄存器的设置为I2C_Write(0xec,0x04,0x20)。设置好后,CH7004的所有寄存器数据如表3。

实验中还发现,设定SPR同步信号极性寄存器时,如果都设同步信号为正脉冲有效,接显示器也能正常显示,但是有闪烁。负脉冲有效则无这种情况,故推荐均设置为负脉冲有效。

表3 正常工作时,CH7004C的各个寄存器读出的数据

结语

本文提供的LCD接口转换为VGA接口的解决方案,经过实际验证,切实可行。在Linux和Windows CE 4.2两种嵌入式操作系统下均进行了测试,Linux下VGA显示器的画面非常稳定;在Windows CE 4.2下基本稳定,略有闪烁。该方案最大特点在于让嵌入式系统直接支持VGA显示器,具备较大的实际应用意义。

2064

2064

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?