Introduction

PCI Express是一种高性能的通用I/O 接口,用于各种未来的计算和通信平台。对于一些属性(如使用模式、负载存储体系结构和软件接口)都是由PCI Local Bus维护,而PCI Local Bus的并行总线实现由一个高度可伸缩的全串行接口取代。

PCI Express利用了点对点互连、基于交换机的技术和分组协议方面的先进技术来传输数据。同时支持一些其他功能比如:电源管理,QOS(质量服务)、热插拔、数据集成以及错误处理等等。

总而言之,PCIE 就是 PCI loacl Bus 的升级版。

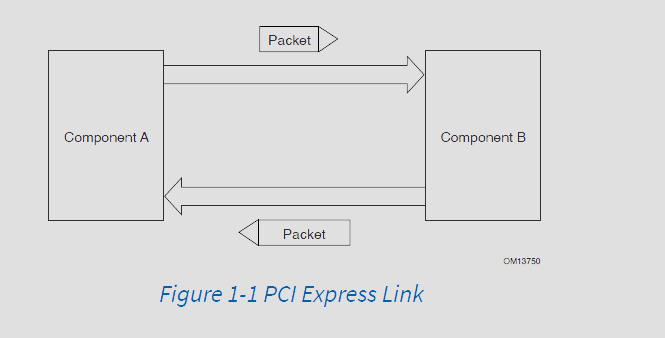

PCI Express Link

PCIE 的数据链路表示两个组件之间的双工通信通道。基本的PCI Express Link由两个单向、低压、差分的传输信号对组成:一个用于发送一个用于接收。PCIE 的传输速率也是通过增加这个信号对的组数来增加。

、

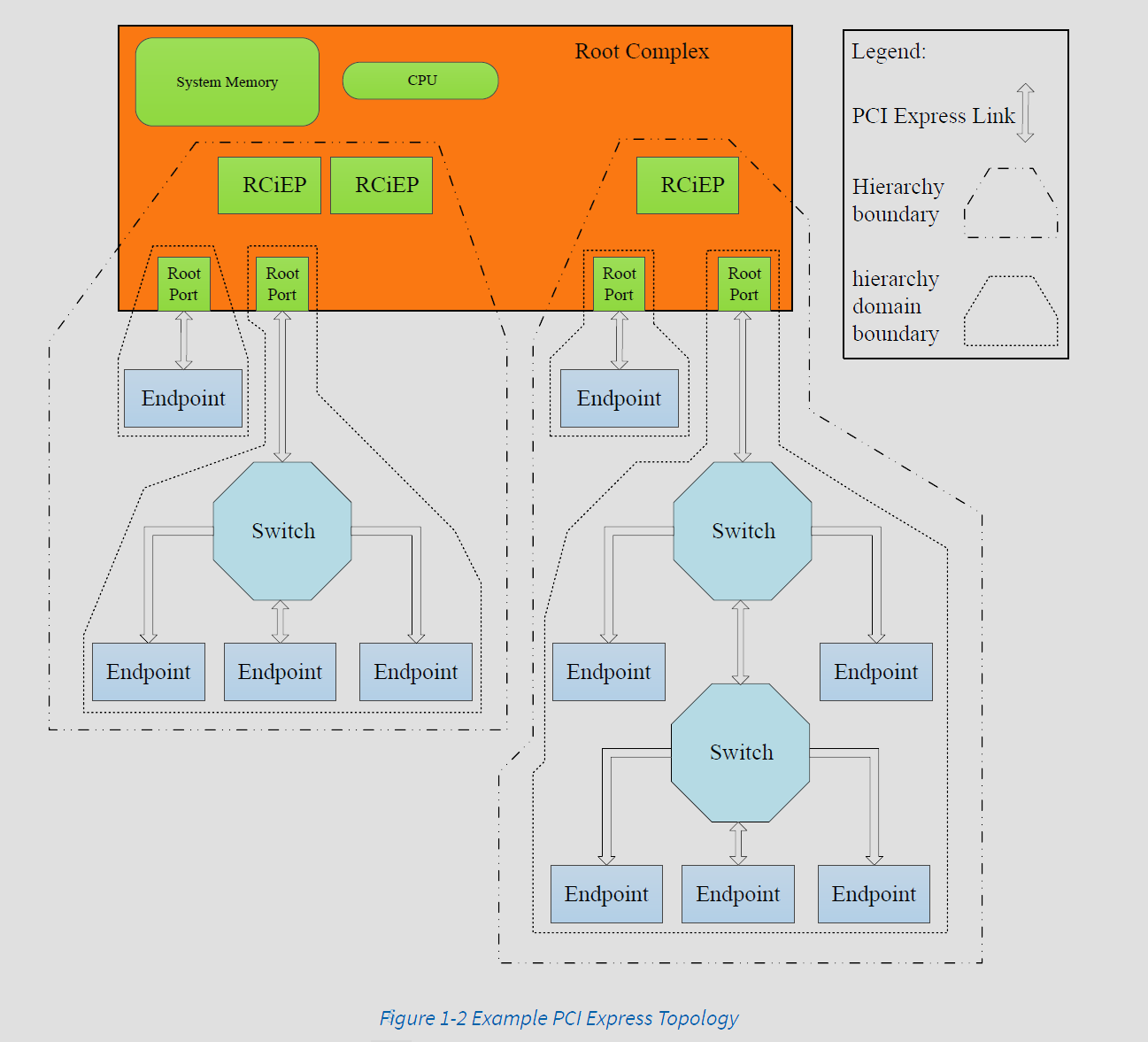

PCI Express Fabric Topology

PCIE 的基本拓扑结构是基于 Switch 的点对点结构,主要是包含三部分:Root Complex、Switch、Endpoint。它们通过 PCIE link 连接。

Root Complex

RC 可以看作是 I/O 系统的 root,主要是用于连接 CPU/Memory 和 I/O 设备。每个 RC 同时包含一个或者多个 Root Port,每个 RP 可以直接连接一个 EndPoint 或者通过一个 Switch 连接多个 Endpoint。RC 可以对来自 Root Port 的请求进行修改和分割,可以将一个数据包分为几个,但是修改或是分割完,需要再返回给原来的发起者。同时,RC 也可以被当作是所有请求的发起者。

Endpoints

EndPoint 不能认为就是一个设备,它是一种功能实现,可以是 PCIE 事务的发起者也可以是完成者。它即可以代表一个 PCIE 设备,也可以代表一个非 PCIE 设备(除 CPU 和 PCIE 设备外的设备),例如图像控制器、PCIE USB host 控制器。

Endpoint 可以分为:

-

- legacy Endpoint

- PCIE Endpoint

- Root Complex Integrated Endpoint(RCiEP)

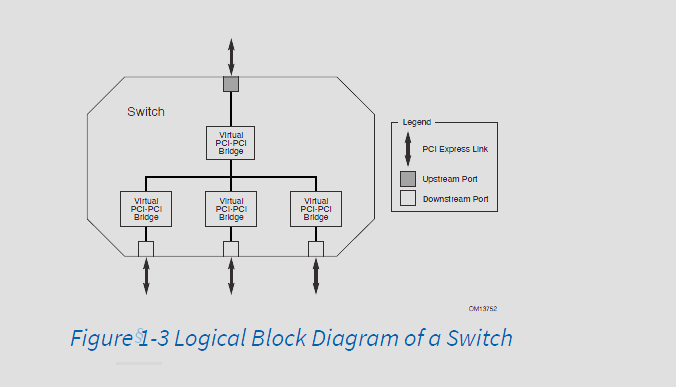

Switch

Switch 其实可以理解成为多个 PCI-to-PCI bridge 的逻辑集合,对于PCI-to-PCI bridge 的介绍可以看 PCI local Bus Spec。

硬件/软件模型的发现,配置和

操作

PCI/PCIe硬件/软件模型包括所需的体系结构构造函数来实现发现、配置和使用,不需要特定于函数。

PCI Express配置模型支持两种机制:

PCI-compatible configuration mechanism:PCI兼容机制支持与传统PCI感知操作系统及其相应的总线枚举和组态软件的兼容性,也就是 PCI 中的配置空间,但是增加了对于 PCIE 扩展空间的信息,可以通过 address 去寻找 PCIE 配置空间。

PCI Express enhanced configuration mechanism:

提供增强机制以增加可用配置空间的大小并优化访问机制。

本文详细介绍了PCIExpress,一种高性能的通用I/O接口,它提升了数据传输速度,采用点对点互连和Switch技术。文章涵盖了PCIExpressLink、PCIEFabricTopology(包括RootComplex、Switch和Endpoints)、以及硬件/软件模型的配置机制,特别提到了兼容性和增强配置选项。

本文详细介绍了PCIExpress,一种高性能的通用I/O接口,它提升了数据传输速度,采用点对点互连和Switch技术。文章涵盖了PCIExpressLink、PCIEFabricTopology(包括RootComplex、Switch和Endpoints)、以及硬件/软件模型的配置机制,特别提到了兼容性和增强配置选项。

767

767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?