以太网被广泛应用于每一台计算机和复杂的硬件板或系统中,主要用于连接机箱外部的设备,但也有时用于内部连接。互联网是通过城市、国家和全球范围内的互联网骨干链路连接的所有本地以太网网络。以太网由IEEE 802.3标准定义,其速度和“介质”类型(如光纤、同轴电缆、背板等)由相关修订文件(如802.3X)规定。这些文件可以从电气和电子工程师学会(IEEE)购买。

以太网协议

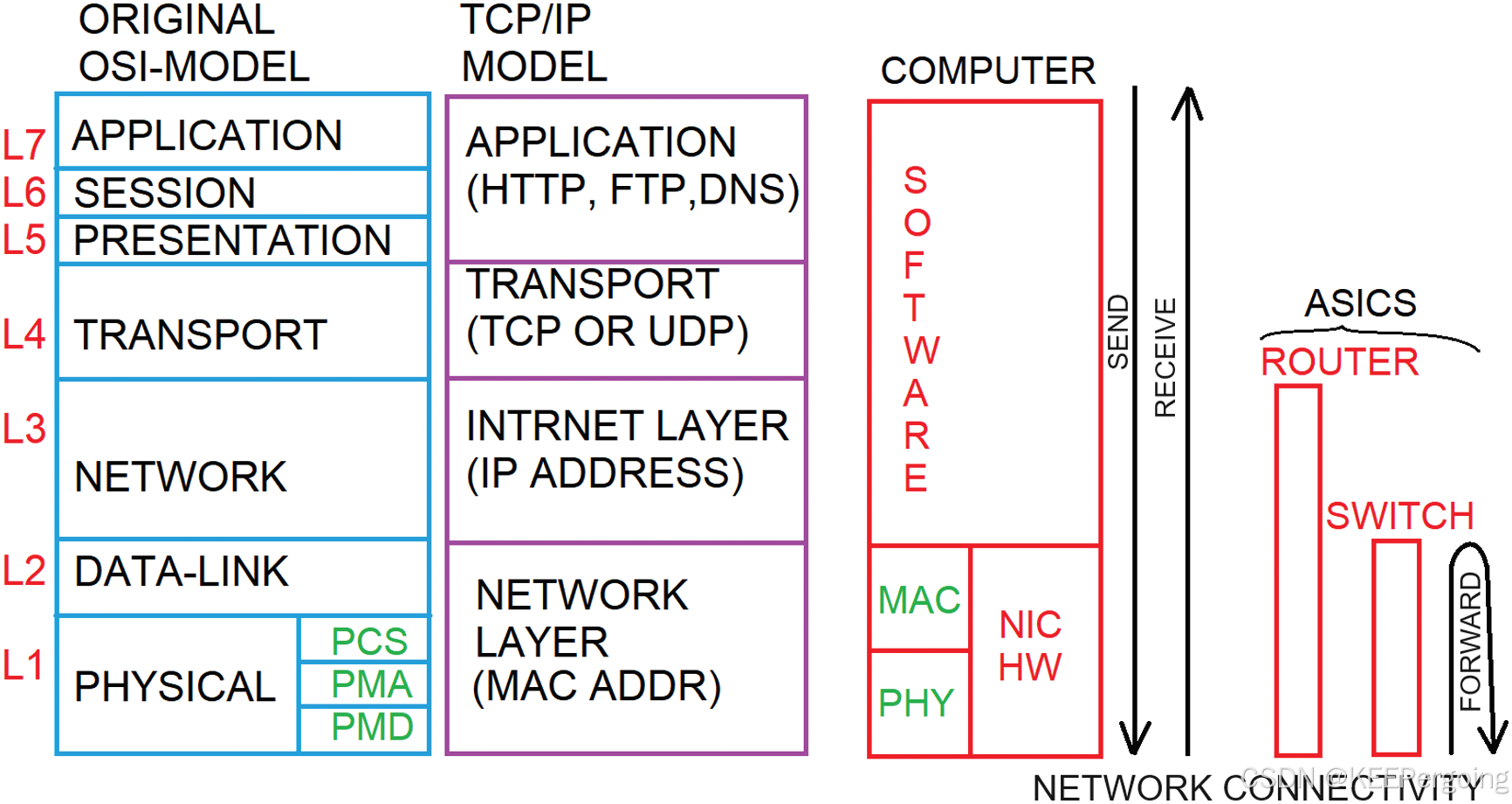

FIGURE 3.1 Layered Ethernet model.

最左边的是OSI7层模型,以太网接口采用分层架构设计,以便于设备之间的通信。以下是与以太网接口相关的主要组件和功能概述。

分层结构

-

下层

- 由物理元素组成,如电缆、板设计和芯片设计。

- 实现在硬件中,包括交换机和路由器ASIC(应用专用集成电路)。

-

上层

- 通常在以太网MAC(媒体访问控制)或控制器芯片中以硅实现。

- 这些芯片通常通过PCIExpress连接到处理器,允许软件通过内存映射读/写事务访问寄存器。

关键组件

-

MAC和PHY接口

- MAC与PHY(物理层,Physical Layer Transceiver)芯片之间的接口通常是MII(媒体独立接口)或C2C(芯片对芯片)接口。

- 有时,MAC和PHY集成在一个单独的芯片中,称为网络接口控制器(NIC) 或者说网卡。

-

以太网交换芯片

- 包含多个端口(每个端口都有自己的MAC和PHY),并增加了用于数据包转发的逻辑。

MAC地址

- 每个MAC或端口在制造时被分配一个唯一的6字节MAC地址,该地址存储在EEPROM中,并在启动时加载。这就是我们常说的物理地址。

IP地址

- IP地址用于标识计算机或计算机上的以太网端口,通常在运行时动态分配,用于在网络间路由数据。

物理层细分

物理层分为三个子层:

-

PMD(物理媒介依赖子层)

- 直接连接到外部线路,包括I/O缓冲电路和半模拟电路。

-

PMA(物理媒介附加子层)

- 负责串行化、时钟/数据恢复以及基于FIFO的时钟域隔离。

-

PCS(物理编码子层)

- 处理编码、MII/C2C链路数据包处理和去偏移。

切换与路由

-

切换(Switching)(第2层或L2)

- 根据MAC地址将以太网数据包从一个端口传送到另一个端口。

- 交换机会根据设备的MAC地址逐步建立知识。

-

路由(Routing)(第3层或L3)

- 基于IP地址路由数据包,需要更复杂的逻辑来解码更高层次的数据包抽象。

- 相较于交换机,路由器维护的路由信息量更大。

网络处理

- 交换机通常同时处理数据中心中的几十台服务器,而路由器则管理数百台服务器,将流量聚合到更少的电缆上。

- 整个互联网中,交换机数量往往多于路由器。

- 一些现代交换机(如脊骨交换机)具备L3路由能力。

结论

理解以太网接口的分层结构以及MAC、PHY的角色,以及切换与路由之间的区别,对于掌握网络通信的运作至关重要。这种分层方法使网络设计具有灵活性和可扩展性。

不同以太网端口类型的功能和应用——外部和背板接口

TABLE 3.1 External Ethernet Port Types

| Standard | TX Lanes | RX Lanes | Baud Rate | Modulation | Bandwidth per Direction |

|---|---|---|---|---|---|

| 100BASE-TX | 1 | 1 | 125 Mbit/s | NRZI | 125 Mbps |

| 1000Base-T | 2 | 2 | 125 Mbit/s | PAM5 | 500 Mbps |

| 1000Base-TX | 1 | 1 | 250 Mbit/s | PAM5 | 500 Mbps |

| 1000Base-KX | 1 | 1 | 1000 Mbit/s | NRZ | 1000 Mbps |

| 1000Base-X | 1 | 1 | 1000 Mbit/s | NRZ | 1000 Mbps |

| 2.5GBase-T | 2 | 2 | 200 Mbit/s | PAM16 | 1250 Mbps |

| 10GBase-T | 2 | 2 | 800 Mbit/s | PAM16 | 5000 Mbps |

| 25GBase-T | 2 | 2 | 2000 Mbit/s | PAM16 | 12500 Mbps |

| 10GBase-BX4 | 4 | 4 | 3125 Mbit/s | NRZ | 10 Gbps |

| 10GBase-KR | 1 | 1 | 10 Gbit/s | NRZ | 10 Gbps |

| 10GBase-R | 1 | 1 | 10 Gbit/s | NRZ | 10 Gbps |

| 10GBase-CR | 1 | 1 | 10 Gbit/s | NRZ | 10 Gbps |

| 25GBase-KR | 1 | 1 | 25 Gbit/s | NRZ | 25 Gbps |

| 40GBase-KR4 | 4 | 4 | 10 Gbit/s | NRZ | 40 Gbps |

| 56GBase-KR | 1 | 1 | 28 Gbit/s | PAM4 | 56 Gbps |

| 100GBase-KR | 1 | 1 | 112 Gbit/s | PAM4 | 112 Gbps |

| 100GBase-KR4 | 4 | 4 | 25 Gbit/s | NRZ | 100 Gbps |

| 200GBase-KR4 | 4 | 4 | 56 Gbit/s | PAM4 | 200 Gbps |

| 400GBase-KR | 4 | 4 | 112 Gbit/s | PAM4 | 200 Gbps |

-

-KR 类型:这些是使用差分对和DFE均衡的端口,通常用于板载或背板连接。" -KR4 "版本使用四个通道,表示总带宽而非信号速率。

-

-Base-T 和 Base-TX 类型:这些端口主要用于机箱外部连接,但也可在内部使用。它们使用RJ45连接器、变压器和双绞线电缆,支持两对或四对差分线。变压器可能内置在连接器中(称为“MagJack”)。RJ45连接器有金属外壳,有八个接触点用于四对差分线。10/100Meg版本只使用四个引脚。

-

XAUI:这是MAC到PHY接口,有时在背板上使用,替代KR。

-

Base-SR 和 Base-LR:光学端口类型。

-

Base-CR:用于数据中心机架的双绞铜缆,长度为1到3米,可插入与LR和SR相同的插槽

MAC-PHY接口

以太网端口的组织结构如下:

Host ← → MAC ← → PHY ← → Port ← → Ethernet connectivity (line)

每个以太网芯片都有一个面向CPU的主机端和一个面向外部电缆的线路端。这些模块可以在单个芯片上实现。主机可以是处理器、FPGA,或在交换ASIC中的一些数据移动逻辑。MAC-Host接口通常是PCIe或内部接口。

- MAC:媒体访问控制器(Media Access Controller)

- PHY:物理层设备(Physical Layer Device)

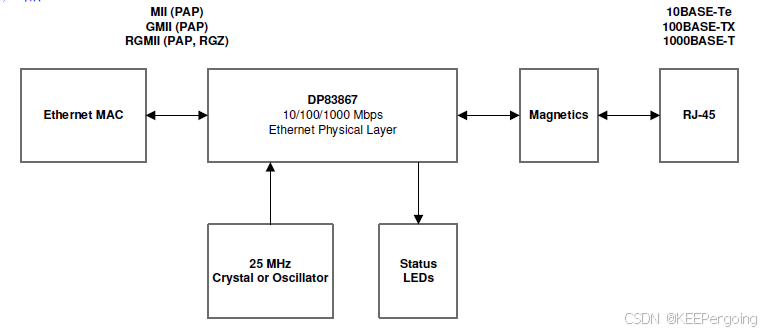

以TI DP83867系列芯片为例,如下图9-1清晰展示例应用连接图。

- RJ-45: 常见的以太网物理接口(Port),用于网络连接。

- DP83867 PHY芯片: 典型的物理层收发器,最大支持1000 Mbps(即1 Gbps)。它集成了PMD子层,支持10BASE-Te、100BASE-TX和1000BASE-T以太网协议。

- 处理器: 通常包含以太网MAC(介质访问控制),负责数据链路层的功能。

工作流程:

- 处理器通过RGMII接口与DP83867 PHY芯片直连,进行数据传输。

- DP83867将处理器传来的数据转换为以太网信号,并通过RJ-45接口发送到网络中。

- 在一般情况下,网卡直接结合了MAC和PHY功能,处理器则可以通过标准接口与网卡通信,实现网络连接。

图 9-1. Typical DP83867 Application

如果MAC和PHY在不同的芯片上,则它们之间有两个接口:一个是数据平面接口,另一个是用于配置PHY寄存器的控制平面慢接口。数据平面接口称为媒体独立接口(MII),有时也称为C2C或短芯片到芯片链接(Chip-to-Chip Link)。

控制平面接口

控制平面接口通常采用MDIO(管理数据输入/输出)链接,该链接由一个时钟线(MDC)和一个数据线(MDIO)组成,运行频率可达数兆赫。在某些情况下,也可以使用I2C总线。无论哪种方式,都需要上拉电阻。

在IEEE 802.3以太网标准中定义了两种MDIO接口变体:

- 第22条款:用于1 Gigabit PHY芯片。

- 第45条款:用于10 Gigabit或更高速的设备。

需要注意的是,上拉电阻的值通常应较低,但建议查阅PHY的数据手册或参考设计原理图以获取具体要求。

MDIO接口可以由MAC或交换ASIC控制,也可以由本地主处理器控制。通常,PHY寄存器的配置由运行在主处理器上的软件决定,或者由简单交换机ASIC内部的嵌入式ARM处理器来进行配置。

TABLE 3.2 Mac-PHY Interface Data Plane Portion Types

| 名称 | 参数 |

|---|---|

| MII | 原始介质无关接口,它是一个4位并行CMOS总线,包含系统信号、25MHz时钟、一组接收信号和一组发送信号。它是一种时钟转发接口,详见时序分析章节。 |

| RMII | 简化的介质无关接口,具有2位并行总线和与MII不同的时钟方式。 |

| GMII | 千兆介质无关接口,类似于MII,具有8位宽的数据和125MHz的时钟。 |

| RGMII | 简化千兆介质无关接口,类似于GMII,但具有4位总线和复用的系统信号。 |

| SGMII | 串行千兆介质无关接口,这是一种串行接口,以625MHz的双数据率和差分信号进行传输,具有一条TX和RX数据通道,以及TX和RX时钟。这支持带有外部1Gig SFP(1000Base-X)接口的PHY。 |

| HSGMII | 高速串行千兆介质无关接口,类似于SGMII,但支持2.5Gig SFP。 |

| QSGMII | 四路串行千兆介质无关接口,传输4个外部1Gig以太网端口的数据,适用于四端口PHY芯片,使用一条5…10Gbit/s SERDES链接的一条通道(一对RX差分对和一对TX差分对)。这允许MAC仅为4个1000Base-T端口占用4个引脚,而在PHY上需要4x8=16个引脚。基本上,它像是一个扇出或端口扩展接口。 |

| XGMII | 10千兆介质无关接口,支持10Gbit外部端口,是一个32位并行接口,具有2组,像MII一样具有时钟转发功能,运行在156MHz双数据率下。 |

| XAUI | 10千兆附加单元接口,具有4条常规SERDES通道,每条通道3.1Gbps。 |

| XLAUI | 40千兆附加单元接口,具有4条常规SERDES通道,每条通道10Gbps。IEEE802.3ba-附录83A描述了SERDES SI通道。也适用于单通道10G类型。 |

| CAUI-4 | 100千兆附加单元接口,具有4条常规SERDES通道,每条通道25Gbps。IEEE802.3bm-附录83D描述了SERDES SI通道。也适用于单通道25G类型。 |

| 400GAUI-8-C2C | 400千兆附加单元接口,具有8条常规SERDES通道,每条通道53Gbps PAM4。IEEE802.3bs-附录120D描述了SERDES SI通道。 |

| 800GAUI-8-C2C | 800千兆附加单元接口,具有8条常规SERDES通道,每条通道106Gbps PAM4。 |

以太网光端口

最常见的光学端口类型列在表3.3中。处理器端或控制平面链接使用I2C通信,每个模块响应相同的地址A0。由于所有端口具有相同的地址,因此它们需要独立的I2C总线。在低端消费级交换机中,I2C可以由交换芯片主控,而在高端机箱中则可以由主处理器主控。

-

插拔式光学收发模块:这些模块用于将板载电气SERDES信号转换为光纤信号,主要用于1Gbps以上的外部以太网端口。

-

I2C管理链接:每个模块使用相同的I2C地址(A0),但由于地址相同,需要独立的I2C总线,主控可以是低端交换芯片或高端主处理器。

-

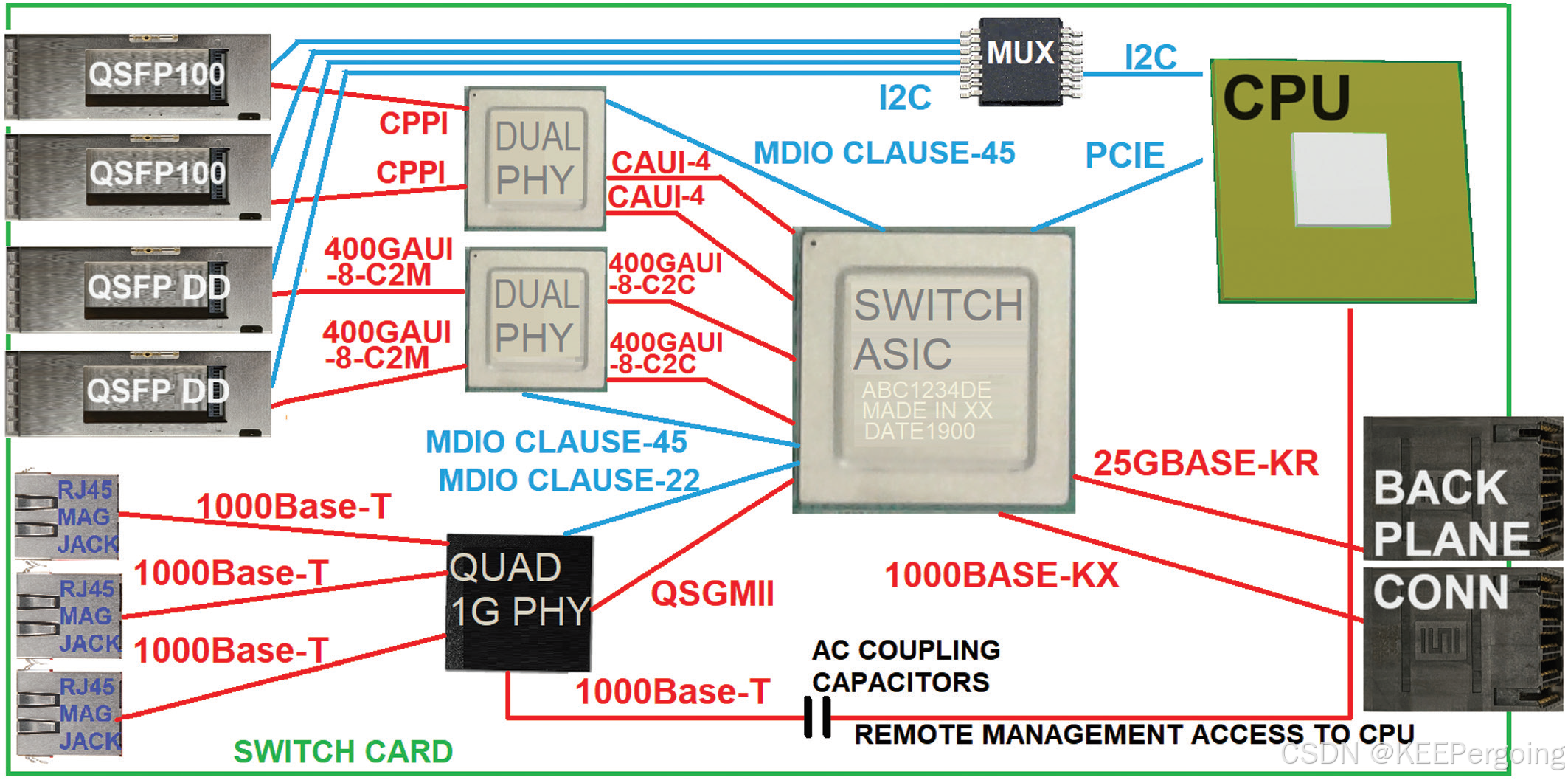

连接要求:只有在ASIC的数据手册明确提及电气接口标准(如XLAUI、SFI)时,才能直接将光学端口连接到交换ASIC;否则需要一个PHY或变速器作为两者之间的桥接。图3.2显示了一个虚拟的电路板框图,其中包含多种类型的外部光学、板载和MAC-PHY接口,以及它们通常的使用方式。

-

插入损耗和回波损耗:芯片与光模块之间的插入损耗和回波损耗要求应根据特定标准(如SFF、OSFP和QSFP-DD)获取,这些值通常在6dB到13dB之间。如果没有找到确切的标准,可以使用相同速度的类似标准,或者使用不同速度但其限制线按照正确的波特率进行缩放的标准。

-

光纤标准:在同一模块类型内,插拔式光学收发模块的光纤侧可以遵循不同的标准。 例如QSFP100模块的100GBase-SR4短距离100m电缆标准,每个方向有四根多模光纤,并且在MTP光连接器中有八个光耦合器。100GBase-LR4长距离标准,是一种长距离10公里的电缆,使用细单模光纤,具有单个TX和单个RX光纤,同时将四束激光通过波长分复用(WDM)技术复用到单根光纤上。任何光学纤维连接至少都包含一根发射光纤和一根接收光纤。

FIGURE 3.2 General use of on-board Ethernet electrical interfaces (sketch).

TABLE 3.3 Common Optical Pluggable Module Types

| 模块名称 | 速率 | 通道 | 适用标准 | 电气接口 | SERDES通道 |

|---|---|---|---|---|---|

| SFP | 1Gbit/s | 单通道(一个RX和一个TX差分对) | INF-8074 | 1000Base-X,单通道1Gbps NRZ | - |

| SFP+ | 10Gbit/s | 单通道 | SFF-8083 | SFI,单通道10Gbps NRZ | 描述于SFF-8418 |

| SFP28 | 28Gbit/s | 单通道 | - | - | 通常沿频率轴缩放SFF-8418 10Gig通道规格 |

| QSFP+ | 40Gbit/s | 4条10Gbit/s通道 | SFF-8436 | XLPPI,4条10Gbps NRZ | 可使用SFF-8418或IEEE802.3ba-annex86A |

| QSFP28 | 100Gbit/s | 4条28Gbit/s通道 | SFF-8665 | CPPI,4条25Gbps NRZ | 在IEEE802.3bm-annex83E中称为CAUI4-C2M |

| QSFP-DD | 400Gbit/s | 8条53Gbit/s PAM4通道 | QSFP-DD . com | 400GAUI-8-C2M,8条53Gig PAM4 | 来自IEEE802.3bs-annex120C |

| OSFP | 400Gbit/s | 8条53Gbit/s PAM4通道 | osfpmsa.org | 400GAUI-8-C2M,8条53Gig PAM4 | 与QSFP-DD相同 |

| OSFP800G | 800Gbit/s | 8条106Gbit/s PAM4通道 | osfpmsa.org | 800GAUI-8-C2M,8条106Gig PAM4 | 来自IEEE802.3df |

Base-T型以太网耦合

以太网端口类型如 1000Base-T 或 10GBase-T 设计为采用变压器(磁性)耦合和隔离。这种设计确保了:

- 长电缆支持:提高了长距离信号的完整性。

- 静电放电保护(ESD保护):提供与电静电放电的隔离。

- 阻抗转换:将扭绞对的阻抗从 75 欧姆转换为板上 50 欧姆单端。

以太网磁性模块

市场上有多种类型的以太网磁性模块,包括单个、双通道、四通道和八通道配置。每个端口包含四个差分对,命名为 MDI[0:3],每对需要一个变压器。

- 双磁性:指的是两组四个变压器,总共八个变压器。

- 以太网变压器:这些不是通用变压器,而是专门为以太网应用设计的,可以用于千兆或100兆选项。

- Magjacks:一种流行的解决方案,用于提供外部1Gig以太网端口,这种连接器是带有内置磁性组件的RJ45连接器(每个端口四个)。

以太网磁性组件类型

市场上有不同类型的以太网磁性组件,具体取决于其绕组数量。选择哪种类型取决于PHY芯片,可以在芯片的数据手册或参考设计中查找。

关键特征:

- 带中心抽头的变压器:通常包括共模电感。

- 中心抽头连接:

- 通常直接连接到 VCC 或通过去耦电容连接到PHY侧的 GND。

- 在线路侧,中心抽头连接到75欧姆AC终端。

阻抗考虑:

- Base-T阻抗:75欧姆线路阻抗。

- PHY侧接口:通常具有100欧姆差分接口。

- 接口数量:

- 一个Base-T接口中有四个差分对。

- Base-TX接口通过两个对进行支持。

1Gig Base-T Ethernet 的交流耦合

- 交流耦合:允许芯片之间的连接,而无需内部接口使用变压器。变压器仅在外部和外板接口中必需,以符合IEEE规范。

- 参考设计:检查每个芯片的参考设计,以查看RJ45变压器中心抽头引脚是连接到 VDD 还是 GND:

- 如果连接到电源,则在该芯片所在的AC电容一侧需要一个感应上拉电阻。

- 使用变压器时,中心抽头应根据芯片的参考设计连接到 GND 或电源/VDD。

1643

1643

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?