一、实验目的

1、掌握计数器的工作方式。

2、掌握计数器的EDA实现方法。

3、掌握数码管的动态扫描显示。

二、实验原理

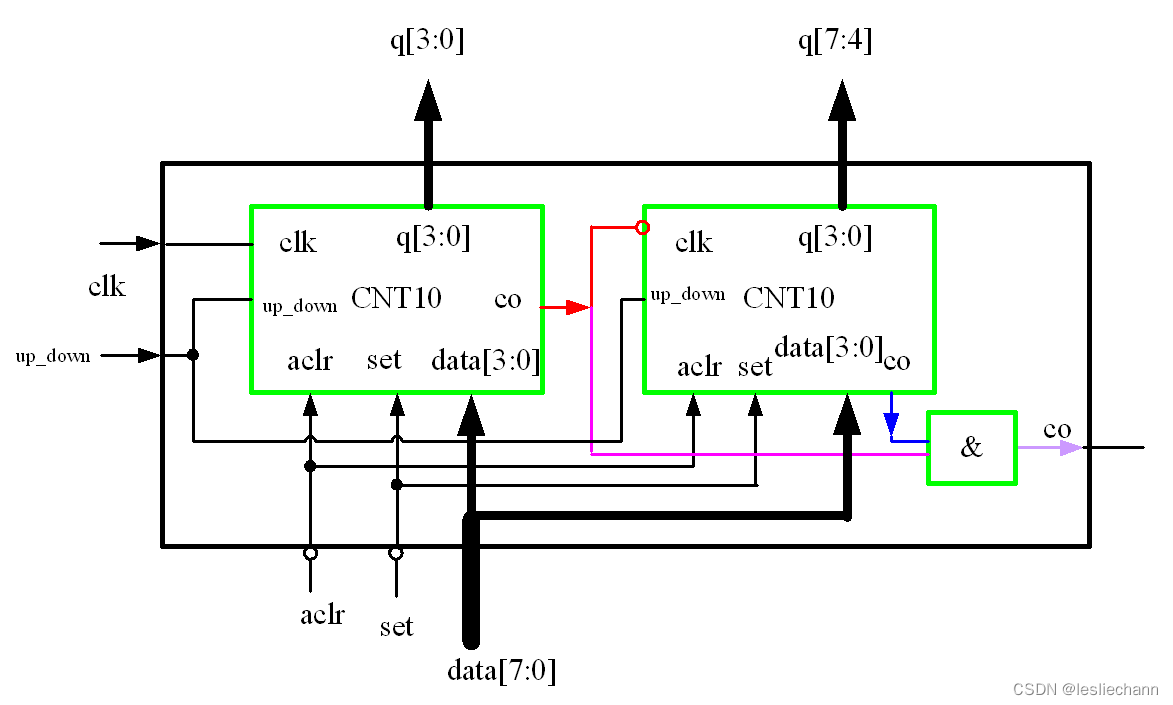

999计数器为三位十进制计数器,其计数范围为000~999。当低位计满10后,向下一个高位进位。利用三位十进制计数器级联即可实现999计数器。

三,实验内容和步骤

1、使用十进制计数器例化法或Verilog代码法实现一个999计数器,要求支持以下功能:

(1)异步清零

(2)异步置数。

(3)加法/减法计数器可设置。

(4)支持进位/借位输出

2、使用数码管的动态扫描方式显示三位计数值。

代码如下:

module CNT100(clk,aclr,set,up_down,date,q,co);

input clk;input aclr;input set;input up_down;input [11:0] date;

output[11:0] q;output co;

reg co0,co1,co2;reg [3:0] C,B,A;

always@(posedge clk,negedge aclr,negedge set)

begin

if(aclr==0)

A<=(up_down)?4'd0:4'd9;

else if(set==0) A<=date[3:0];

else if(up_down==1)

begin

if(A<4'd9) A<=A+4'd1;

else A<=0;

end

else

begin

if(A>0)A<=A-4'd1;

else if(A==0||A>9)A<=9;

end

end

always@(negedge co0,negedge aclr,negedge set)

begin

if(aclr==0)

B<=(up_down)?4'd0:4'd9;

else if(set==0) B<=date[7:4];

else if(up_down==1)

begin

if(B<4'd9) B<=B+4'd1;

else B<=0;

end

else

begin

if(B>0)B<=B-4'd1;

else if(B==0||B>9)B<=9;

end

end

always@(negedge co1,negedge aclr,negedge set)

begin

if(aclr==0)

C<=(up_down)?4'd0:4'd9;

else if(set==0) C<=date[11:8];

else if(up_down==1)

begin

if(C<4'd9) C<=C+4'd1;

else C<=0;

end

else

begin

if(C>0)C<=C-4'd1;

else if(C==0||C>9)C<=9;

end

end

always@(A)

begin

if(up_down==1&&A==4'd9)co0=1;

else if(up_down==0&&A==0)co0=1;

else co0=0;

end

always@(B)

begin

if(up_down==1&&B==4'd9)co1=1;

else if(up_down==0&&B==0)co1=1;

else co1=0;

end

always@(C)

begin

if(up_down==1&&C==4'd9)co2=1;

else if(up_down==0&&C==0)co2=1;

else co2=0;

end

assign co=co0&&co1&&co2;

assign q={A,B,C};

endmodule

2124

2124

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?