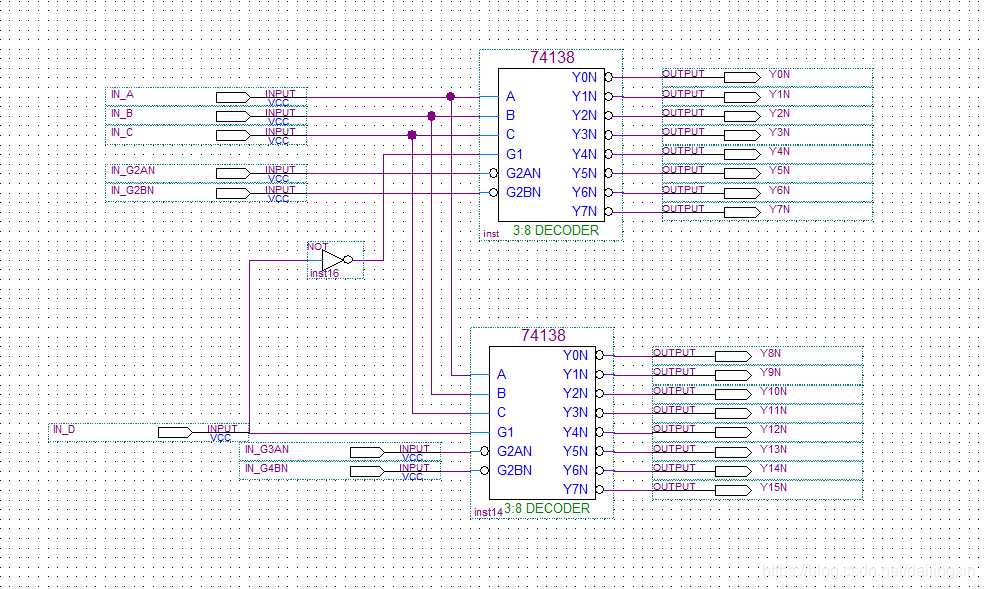

实验一:4-16译码器

内容:用两片74138芯片拼成4-16译码器。

为了达到四位二进制输入的目的,将两片74138芯片进行级联,并添加IN_D引脚,具体原理图如下:

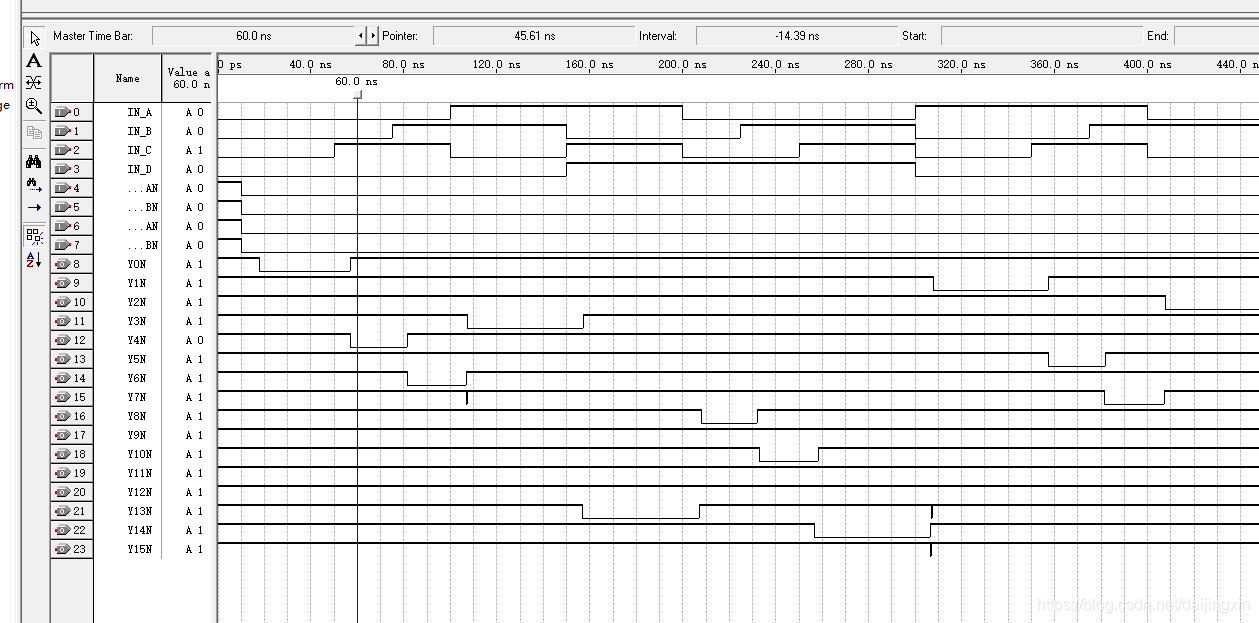

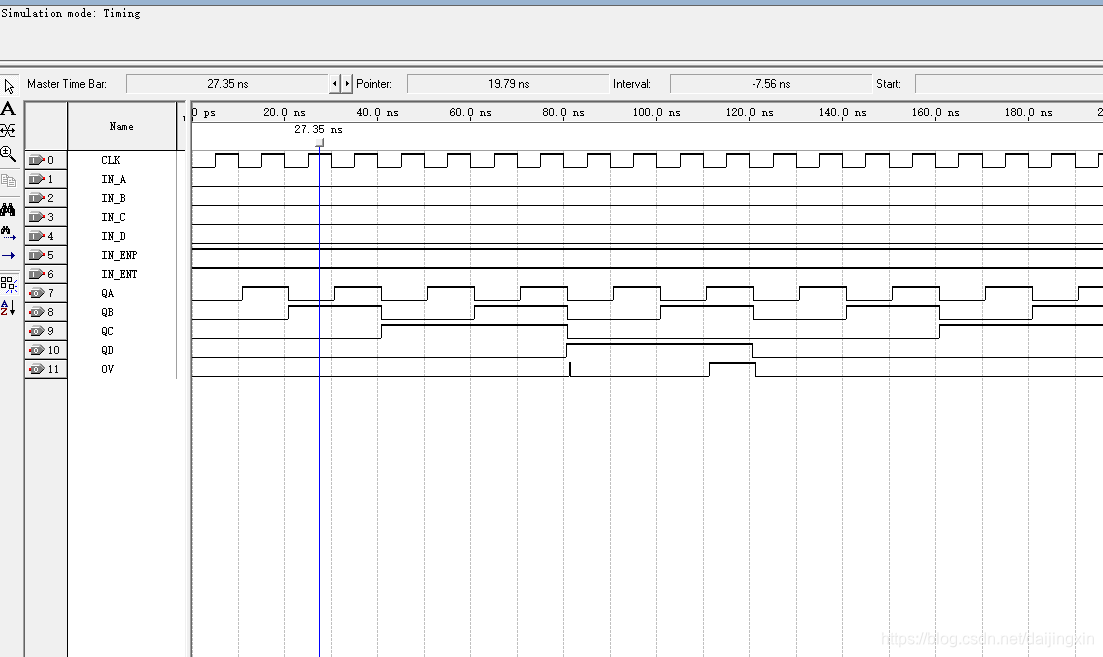

最终产生的波形图如下:

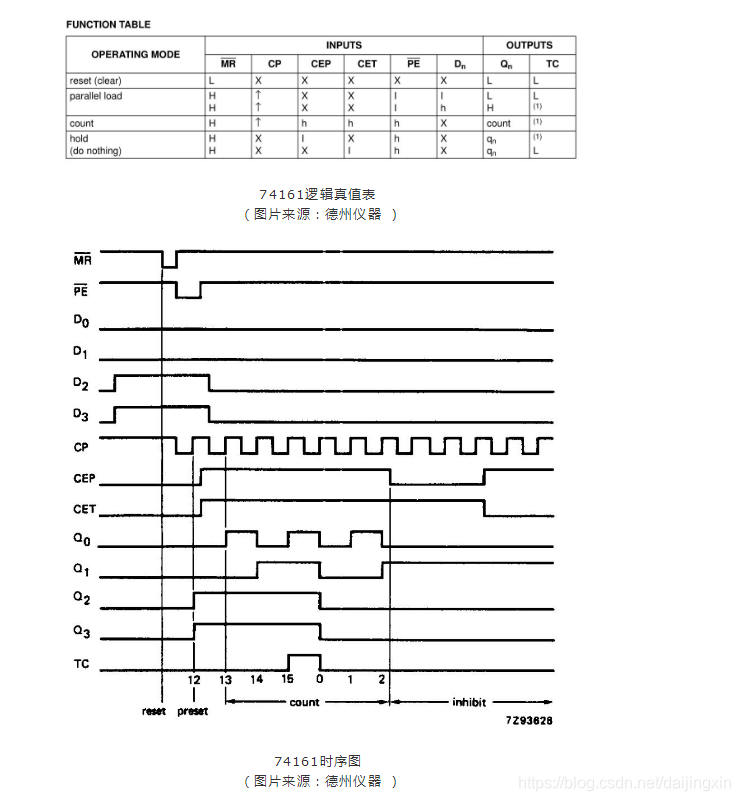

实验二:十二进制计数器

74161芯片的真值表与时序图如上图所示。

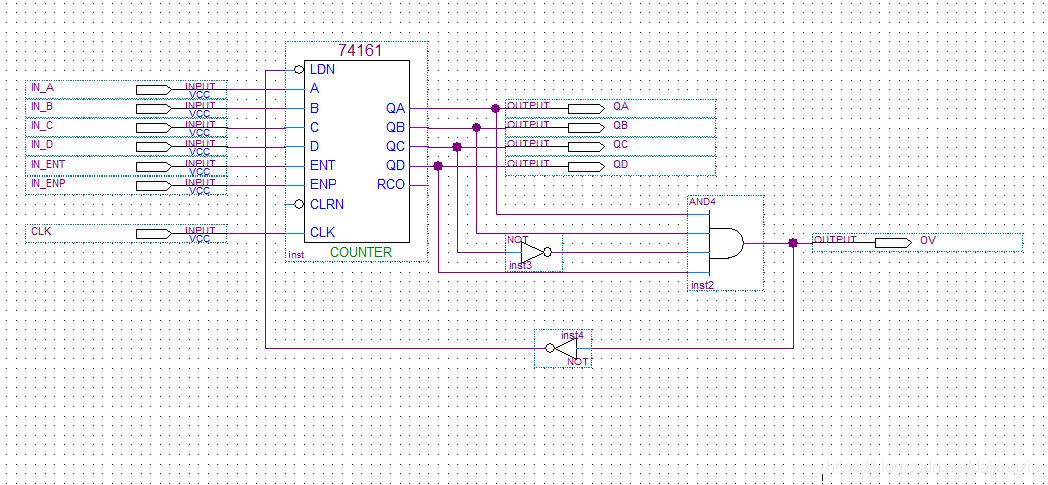

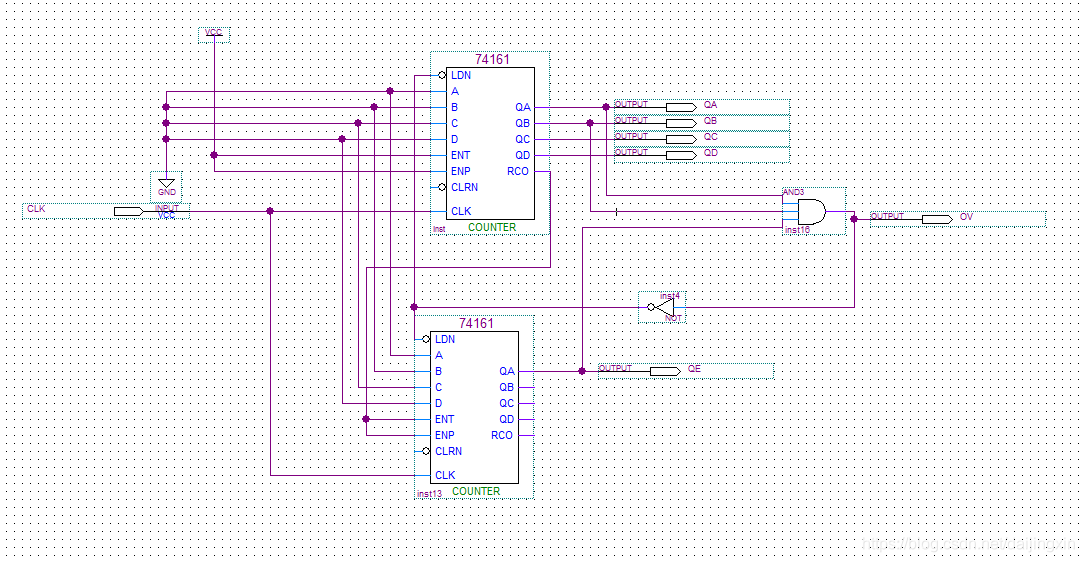

从时序图中可以看出,单片74161芯片最多能进行16进制计数,当输出为1100原理图如下:

波形图:

实验三:二十进制计数器

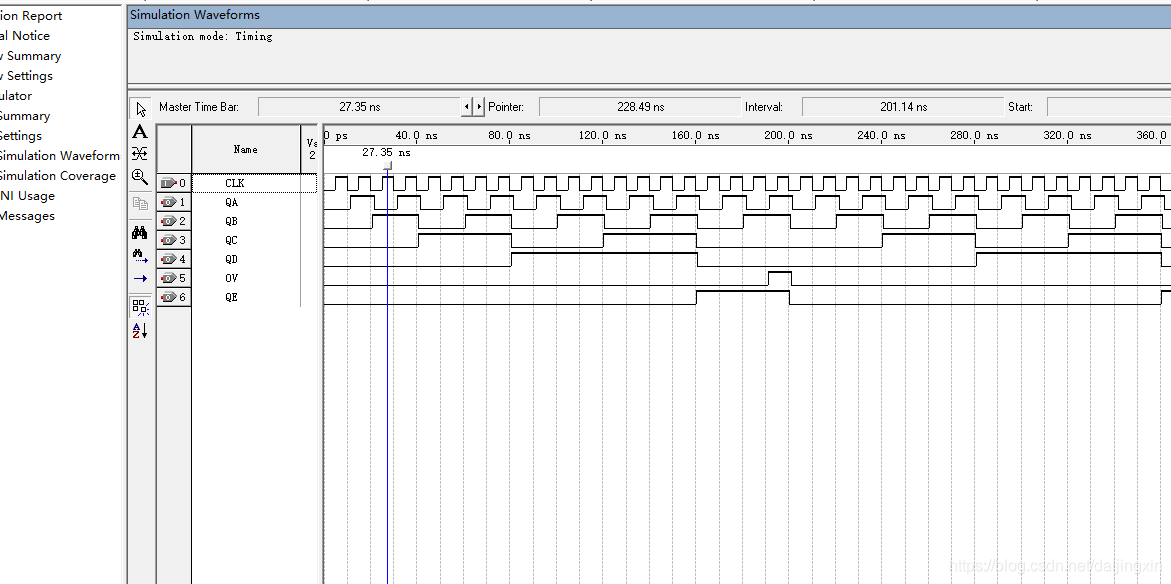

实现二十进制计数器需要两片74161芯片,当输出二进制数为10011时将计数器置零,其原理图如下:

波形图如下:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?