大家好,我是小悟。

打开招聘软件,输入“高薪+双休+五险一金”,蹦出来的岗位多到手指划到抽筋。但一封简历发出去,如同石沉大海,连个“已读”提示都等不来。

这时候,别急着怀疑人生,因为这或许不是你不够优秀的问题,而是招聘软件的“钞能力”把你和面试官隔在了银河系两端。

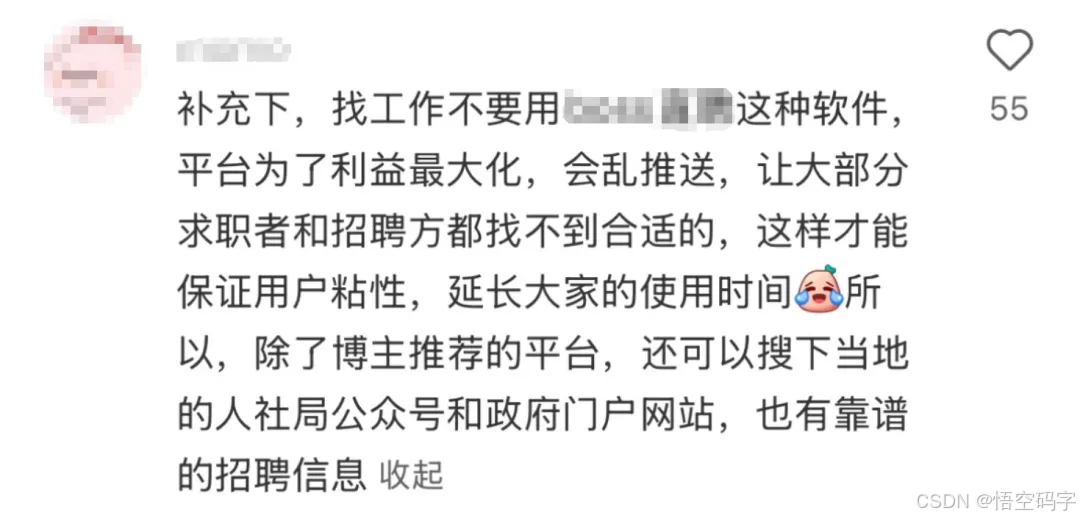

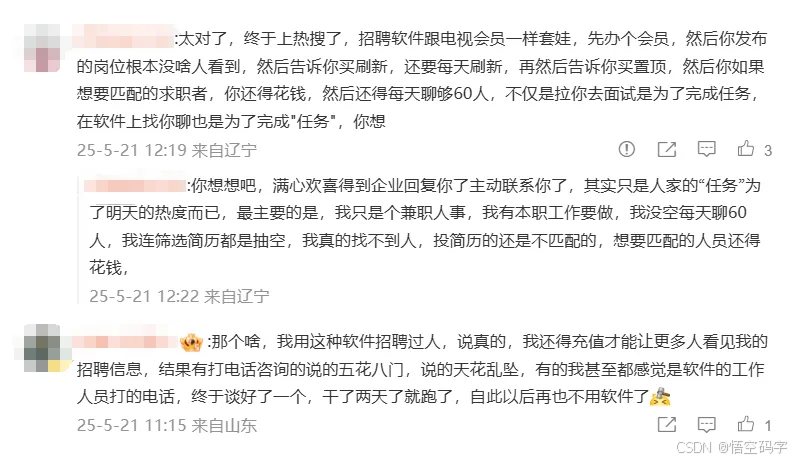

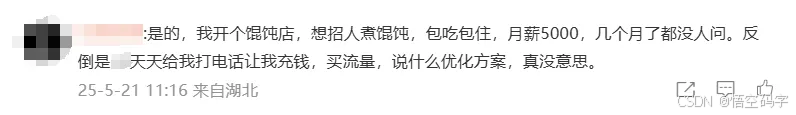

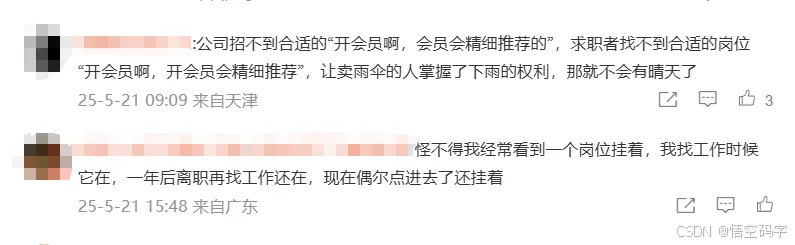

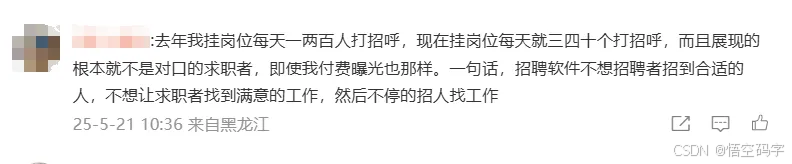

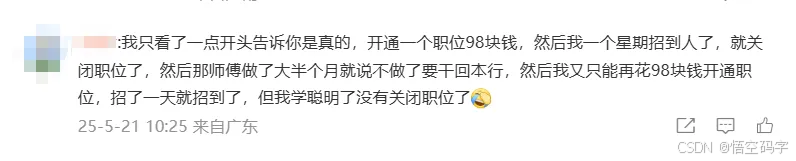

招聘软件的算法,本质上是个“看钱下菜碟”的精明商人。企业发布岗位后,若无后续充值操作,系统可能会直接将其丢进“冷宫”。

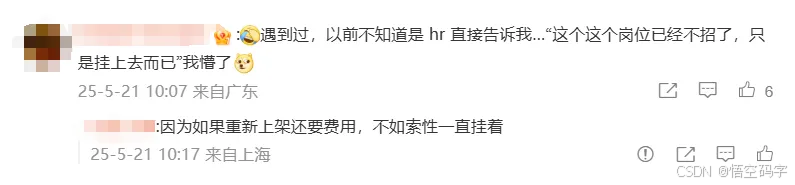

比如某招聘平台被曝悄悄限流中小企业的岗位,导致财务专员这类基础职位5天0投递。可一旦企业充了钱,同样的岗位立刻“原地复活”,简历纷至沓来。

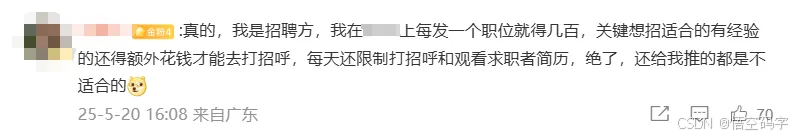

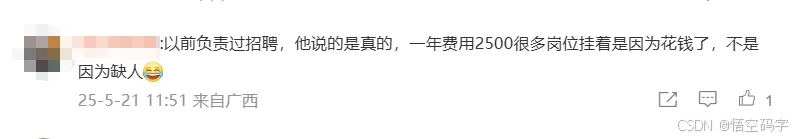

更魔幻的是,部分平台会对企业收“推广费”,比如置顶岗位、刷新提醒,就像给岗位开了个“闪光灯”特效。

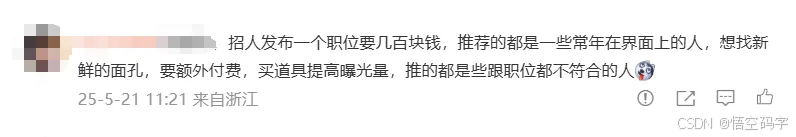

但别高兴太早,企业花了钱,也不一定能找到合适的人。毕竟简历的质量参差不齐,系统推送一堆“伪装成人才”的海投者,企业HR看得头疼。

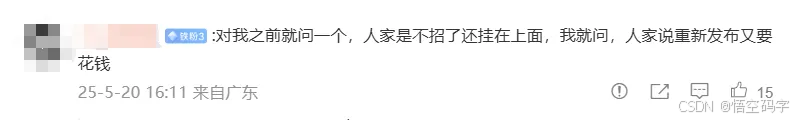

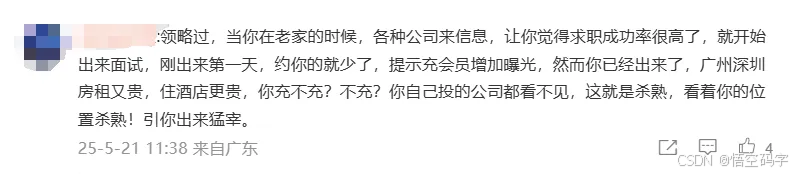

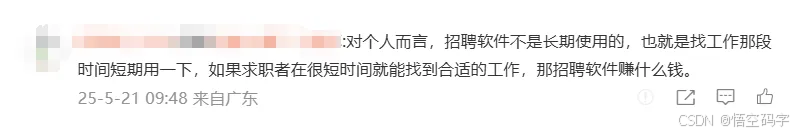

你以为投完简历就能在家躺赢等offer?太天真了。招聘软件的“黑洞”逻辑在这里等着你,普通用户的简历,除非撞大运匹配到企业HR的深夜加班时间,否则基本石沉大海。

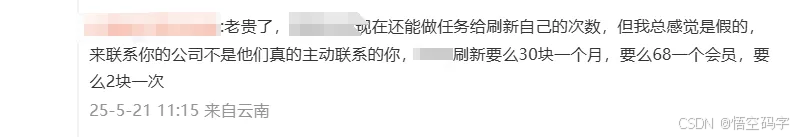

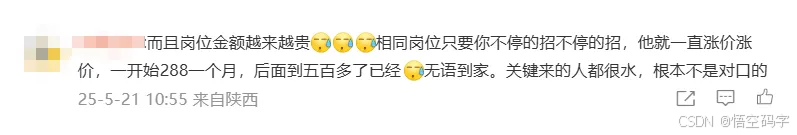

这时候,平台笑容可掬地递来VIP套餐,“升级会员,简历置顶、无限投递、优先推送!”

花了钱,你以为自己能C位出道?实际上,会员权益更像一张“安慰奖”。比如某招聘软件的“349元全能月卡”,承诺60次在线畅聊。

但你聊的对象可能是企业临时工临时助理的表弟开的皮包公司。更离谱的是,简历置顶后,依然被系统判定为“低匹配度”,连面试通知都收不到。

这时候你才恍然大悟:招聘软件的真相是“充值变气氛组”,你的钱只贡献了平台的KPI。

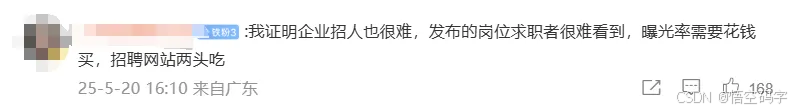

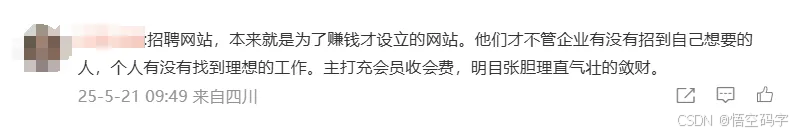

招聘软件的盈利模式,本质上是在制造一场“就业市场虚假繁荣”。平台一边向企业收“投流费”,一边纵容虚假岗位泛滥。

某些创业公司一口气挂出20个程序员岗位,月薪1.5万起,实际入职后只有8K,还附赠“996福报套餐”。

与其在招聘软件上死磕,不如换个思路:

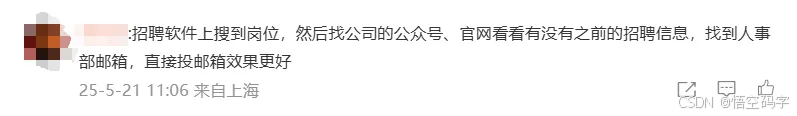

绕过平台,直接“撩”企业:盯紧心仪公司的官网和公众号,投递专属渠道的岗位,避免卷入平台竞价排名。

人脉才是王道:朋友、校友、前同事的推荐,成功率远高于系统推送。毕竟HR也怕踩雷,熟人背书就是“质量保证书”。

练就“火眼金睛”:看到“薪资范围大开大合”“岗位职责不清不楚”的岗位,直接划走,这类岗位要么是画饼大师,要么还是画饼大师。

多平台撒网:别只盯着大平台,小众招聘软件、甚至行业论坛都可能是宝藏。

招聘软件的赚钱逻辑,本质上是一场“双向割韭菜”的资本游戏,企业付钱抢曝光,求职者花钱买安慰。

但真正的职场高手,从不会把命运交给算法摆布。与其花冤枉钱买“伪机会”,不如修炼内功。真正的职场红利,从来不在招聘软件的算法里,而在你自己的本事上。

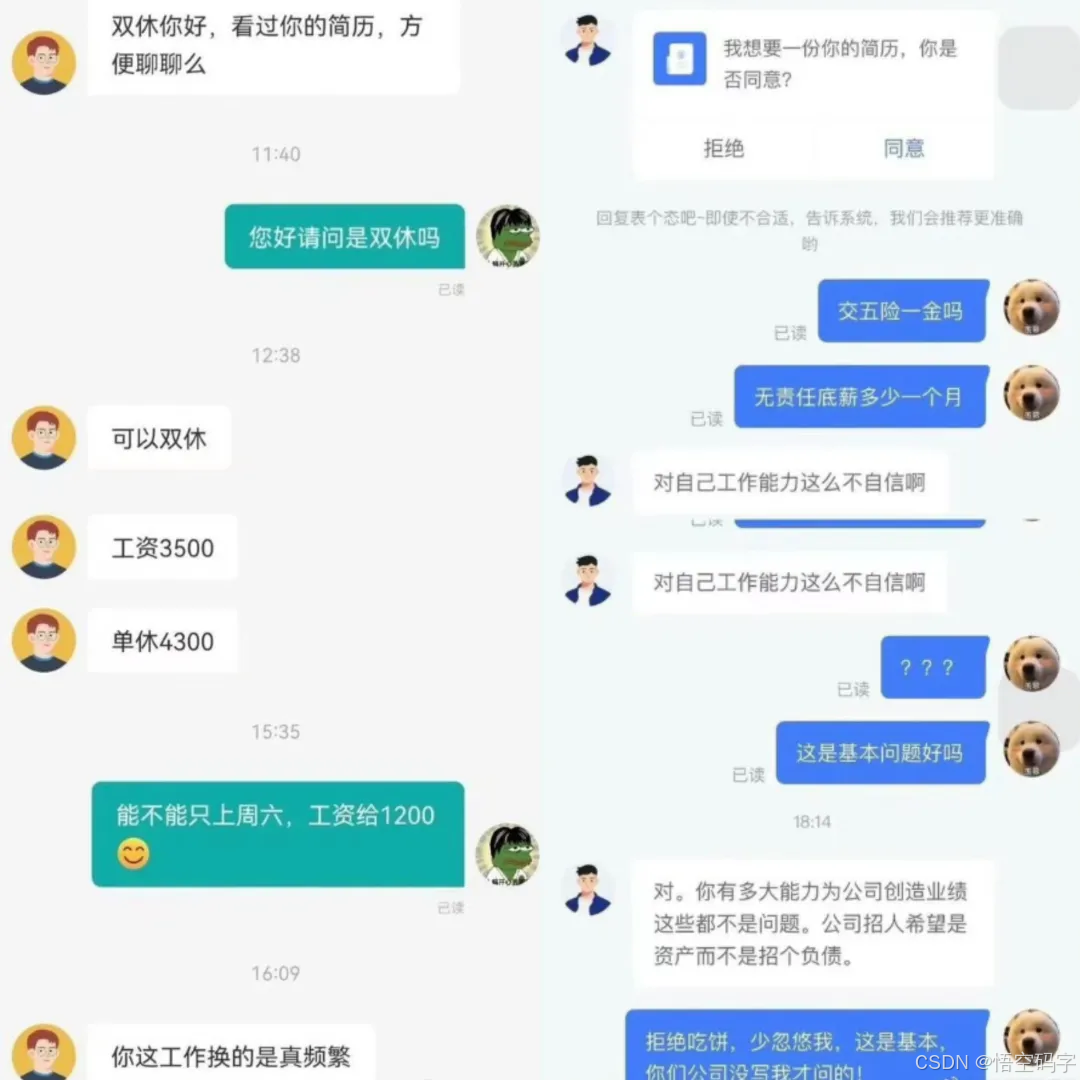

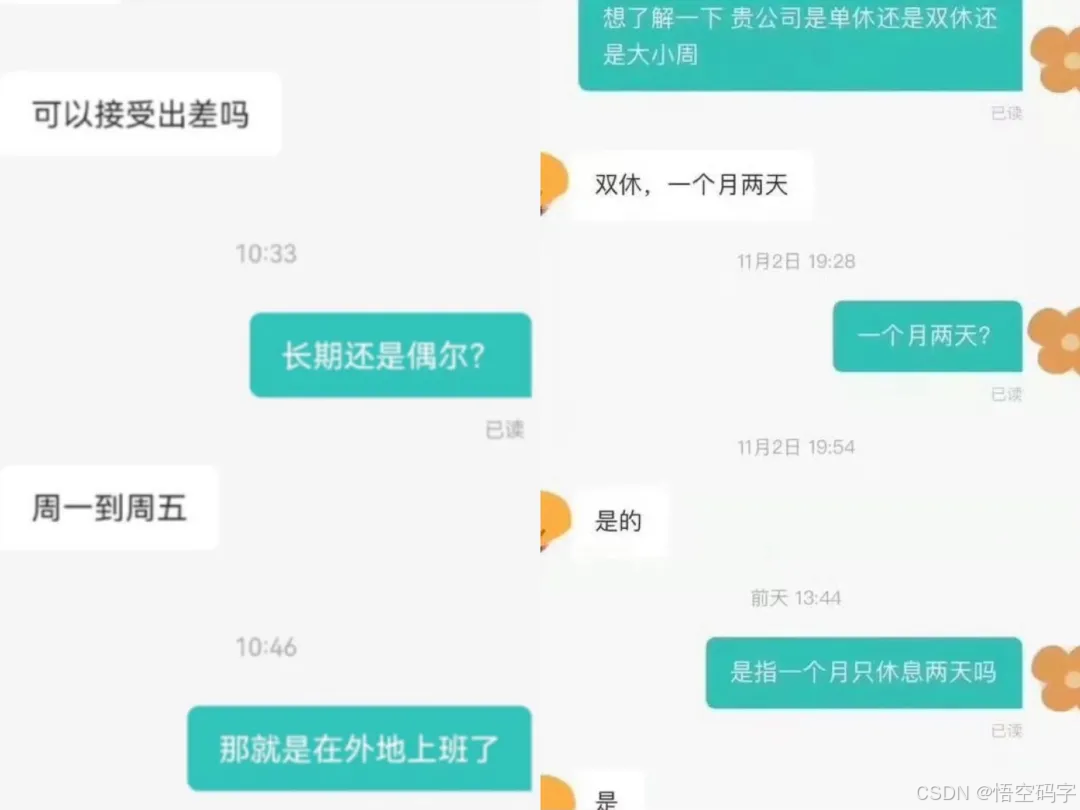

看到一组好笑的HR和求职者对话,分享给大家。

以上图源来自微博

谢谢你看我的文章,既然看到这里了,如果觉得不错,随手点个赞、转发、在看三连吧,感谢感谢。那我们,下次再见。

您的一键三连,是我更新的最大动力,谢谢

山水有相逢,来日皆可期,谢谢阅读,我们再会

我手中的金箍棒,上能通天,下能探海

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?