一 目的

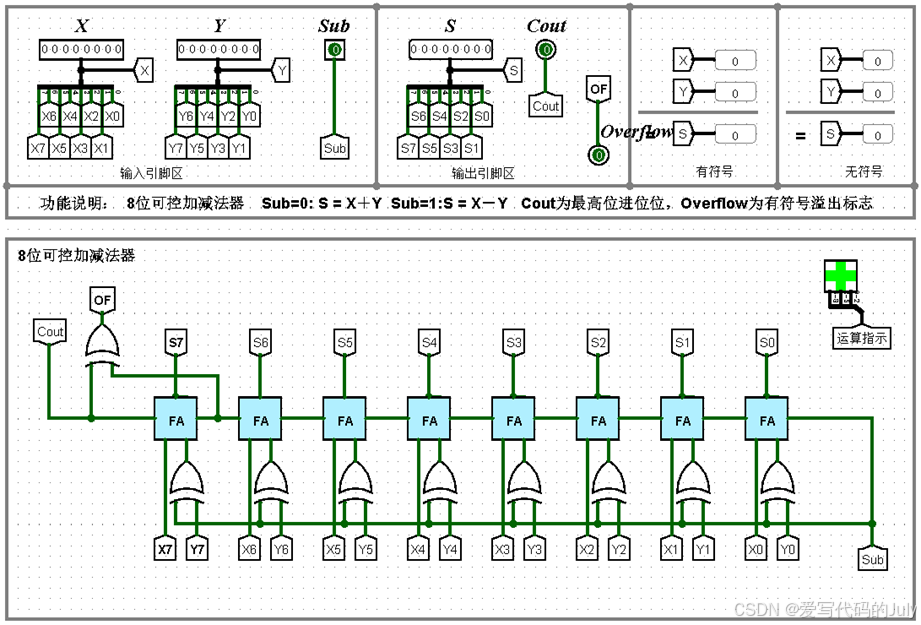

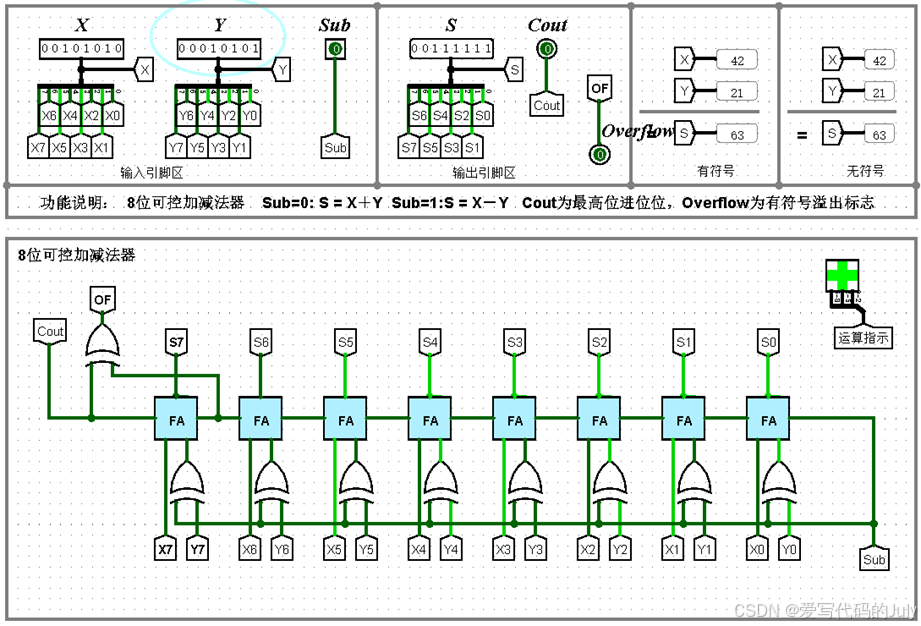

利用logisim平台中现有运算部件构建一个8位可控加减法电路,支持八位加减法运算,支持以下状态标志:有符号溢出信号OF,进位输出Cout。

二 方案设计

1.利用全加器进行减法运算

首先要解决的问题就是如何利用全加器进行减法运算。两个数进行减法运算可以看被减数加负的减数,因此要将y转换成(-y)补之后再进行加法运算:符号位转换成1,数值位按位取反再加1。由于减法运算时sub为1,因此可以将y的各位与sub异或,同时sub作为最低为全加器的低位进位输入,以此实现上述功能。

2.判断溢出

第二个要解决的问题是溢出的判断:两个数的加减法运算可以分为以下四种情况:正+正,正+负,负+正,负+负,而溢出仅会在正+正与负+负时有可能发生。

m表示最高数值位进位,n表示符号位进位,首先讨论一定不会发生溢出的两种情况(正+负与负+正):可以总结为10+01或10+11两种情况(高位为符号位,低位为最高数值位),可能的结果有两种:n=0,m=0和n=1,m=1。此时n异或m=0。

再讨论可能会发生溢出的两种情况。正+正:可能的情况可以概括为01+01,01+00,00+00,其中第一种情况会发生溢出(n=0,m=1,n异或m=1),后两种情况不会发生溢出(n=0,m=0,n异或m=0).负+负:两个负数相加结果应为负数,结果符号位应为1,当符结果号位为0时发生溢出,可能的情况可概括为10+10,10+11,11+11,其中前两种情况的结果符号位为0,发生溢出(n=1,m=0,n异或m=1),第三种情况符号位为1,没有发生溢出(n=1,m=1,n异或m=0)。

综合以上讨论,可以发现当符号位进位和最高位进位异或结果为1时发生溢出,异或结果为0时没有发生溢出。由此就得到了补码运算判断溢出的方法。

3.电路图

三 具体步骤

1.处理减法运算,连接电路图。

2.求溢出判断的方法。

3.由2中得到的方法连接电路图。

4.在实验平台上进行测试。

四 可能遇到的问题及解决方案

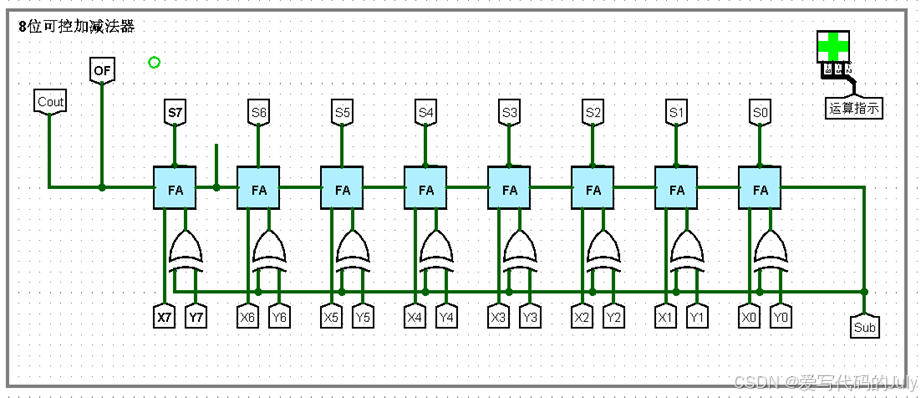

故障现象:接口处数据传输问题

原因分析:如图 ,平台测试时发现了错误,进一步对溢出的情况做了分析。加入了一个异或门部件,正确判断溢出。

解决方案:重新连接电路,正确判断溢出。

如上图所示,加减法控制器sub:是通过异或门给到【操作数y】,为0是加法过程,为1是减法过程。因为异或门取0时正向,取1反向;以此将y转化为反码,个位+1可以将y转化为补码形式参与加法。

而在各个位置上的运算,则以一位全加器的封装作为基本单元,只是通过sub增加对操作数y的变化,使其可以为原码/补码。

检查符号位进位与最高位进位,相同就没有溢出,不同就产生溢出,同样采用异或门实现。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?