一、实验目的

1.验证基本RS、JK、D、T和T’触发器的逻辑功能及使用方法;

2.能进行触发器之间的相互转换;

3.学习触发器的一些应用。

二、实验原理

触发器可分为电平触发的触发器、边沿触发的触发器以及脉冲触发的触发器。触发器与锁存器的不同在于他除了置1、置0输入端以外,又增加了一个触发信号输入端,只有当触发信号到来时,触发器才能按照输入的置1、置0信号制成相应的状态,并保持下去。这个信号被称为时钟信号(CLOCK),记作CLK。当系统中有多个触发器需要同时动作时,就可以用同一个时钟信号作为同步控制信号。

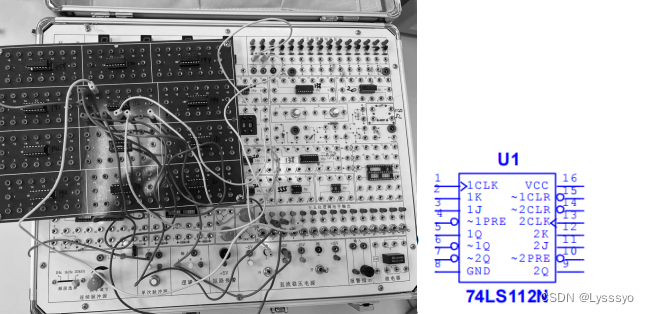

三、使用仪器、材料

双JK触发器74LS112

双D触发器74LS74

四、实验步骤、过程和记录

1)测试D触发器的逻辑功能

74LS112是指一种数字逻辑IC芯片,它由两个可编程JK触发器组成,可实现双稳态控制逻辑,并且具有置位和复位功能。此芯片经常用于电子数字设备中的计数、存储和时序控制等方面。在引脚图中,J:JK触发器的J输入端、K:JK触发器的K输入端、CLR:清除输入端(当CLR=0时清零输出)、CLK:时钟输入端、Q:输出端、~Q:输出端Q的反相输出、T:触发器的时钟控制输入,GND:地

真值表如下:

| PRE ’/CLR ’ | JK | CLK | QN=0 | QN=1 |

|---|---|---|---|---|

| 01 | XX | XX | ||

| 10 | XX | XX | ||

| 11 | 00 | 1→0 | ||

| 11 | 00 | 0→1 | ||

| 11 | 01 | 1→0 | ||

| 11 | 01 | 0→1 | ||

| 11 | 10 | 1→0 | ||

| 11 | 10 | 0→1 | ||

| 11 | 11 | 1→0 | ||

| 11 | 11 | 0→1 |

当时钟输入端口CLK收到上升沿时,如果J和K的输入为0,那么输出不变。如果J和K的输入为1,那么输出翻转。如果J为1,K为0,那么输出为1。如果J为0,K为1,那么输出为0。

2)将其改为T触发器,测试其逻辑功能

真值表如下:

真值表不见了

-

测试74LS74的逻辑功能

74LS74是一种双T触发器集成电路芯片,常用于数字电路中的计数器、分频器等电路中。它由两个T触发器构成,并且可以通过输入端实现控制清零、控制置位、控制预置等功能。

| QN+1 | |||

|---|---|---|---|

| D | CLK | QN=0 | QN=1 |

当时钟信号为高电平状态(或上升沿)时,输入信号会被写入到相应的触发器中。输入信号的稳定时间必须提前到达到触发器的输入端口。当时钟信号为低电平状态时,触发器不会接收或改变输入信号。CLR端口和PRE端口都是异步的,与时钟无关。当CLR为低电平时,所有触发器的输出都被清零。当PRE为低电平时,所有的输出都被置为1。在其他情况下,输出保持不变。

五、实验结果分析与感想

在本实验中,双JK触发器74LS112和双D触发器74LS74都符合其逻辑功能,具体而言,双JK触发器可以实现同步复位、异步复位、异步置位和数据锁存的功能,而双D触发器则可以实现同步复位和异步复位功能。

在实验中,通过给双JK触发器74LS112和双D触发器74LS74不同的输入信号,观察它们的输出变化。经过实验发现,双JK触发器在输入J、K和时钟信号变化时能够正确地输出预期结果,而双D触发器也能够正确地输出结果。

7890

7890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?